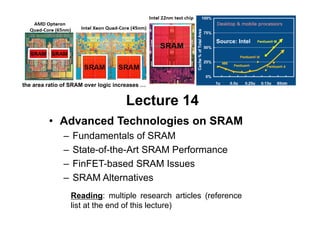

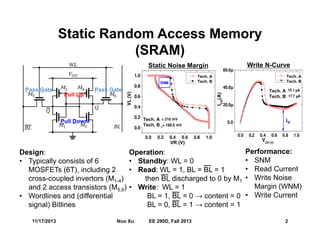

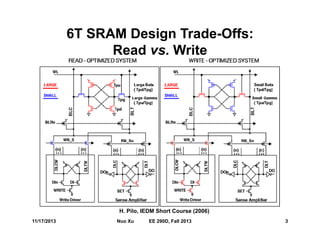

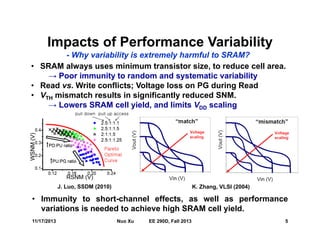

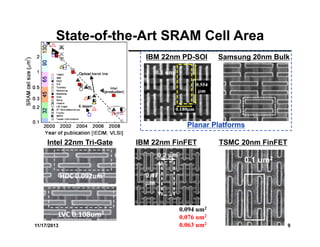

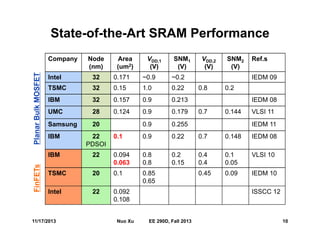

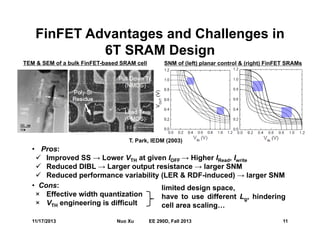

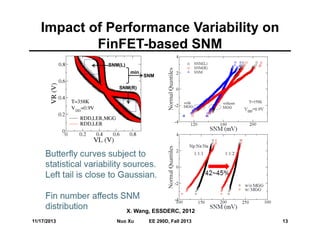

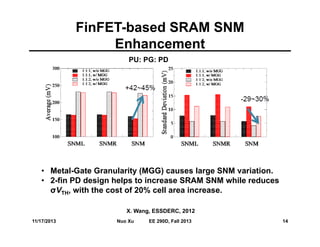

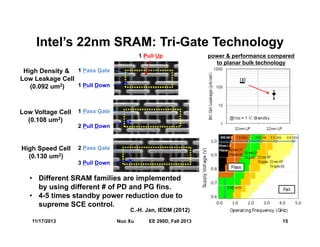

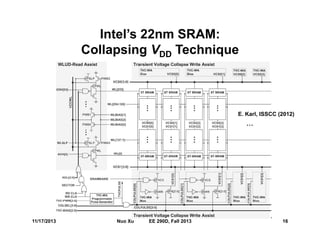

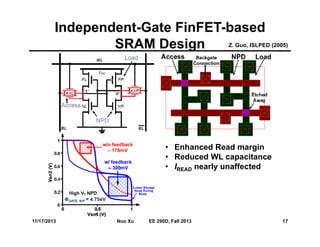

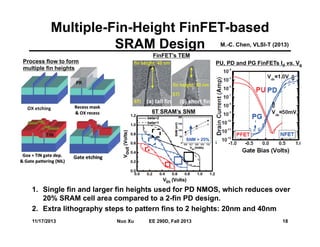

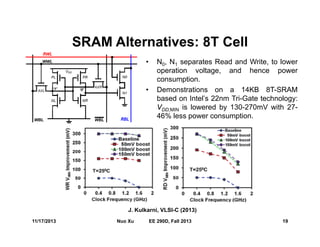

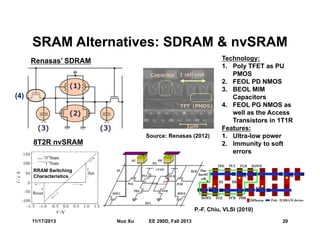

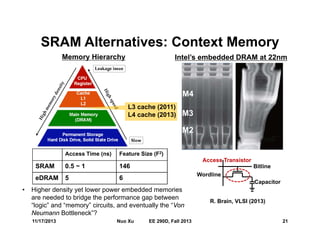

This lecture discusses advanced SRAM technologies including FinFET-based SRAM issues and alternatives. It begins with fundamentals of 6T SRAM design and reviews state-of-the-art SRAM performance. Key challenges for FinFET-based SRAM include variability impacts and design tradeoffs. The lecture explores techniques to improve SRAM stability for FinFETs and reviews Intel's 22nm tri-gate SRAM technology. Finally, it discusses SRAM alternatives such as 8T cells, SDRAM, and context memory to address scaling challenges.