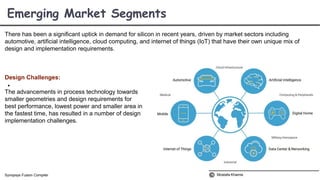

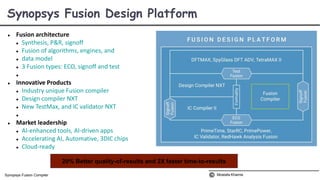

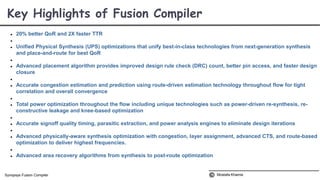

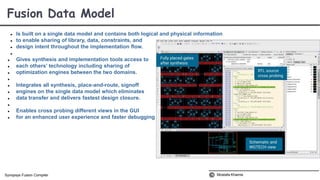

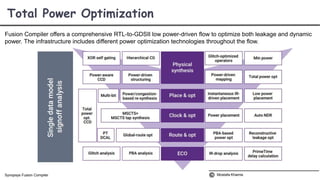

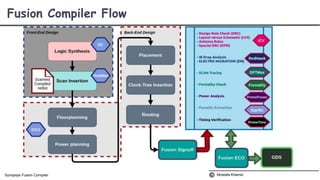

The document discusses the Synopsys Fusion Compiler, a comprehensive RTL-to-GDSII implementation system designed to address the complexities of modern silicon design. It highlights improvements in performance and efficiency, aiming for 20% better quality of results and 2x faster time to results through unified physical synthesis and innovative technical solutions. Key features include advanced routing, total power optimization, and integration of synthesis and implementation tools to streamline the design closure process.