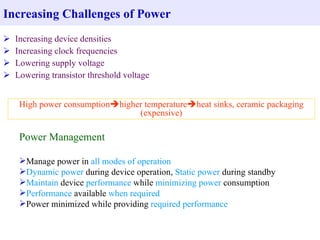

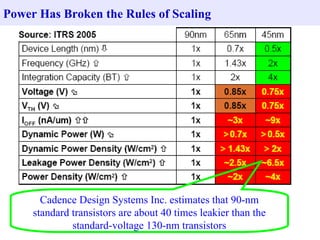

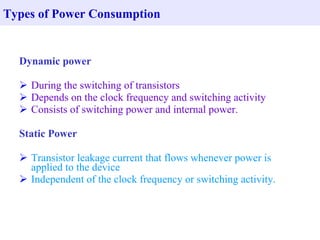

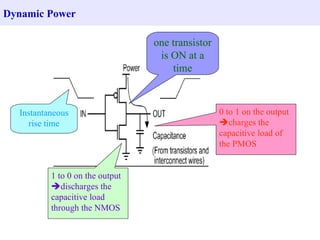

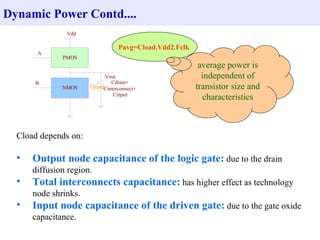

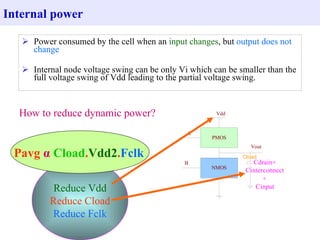

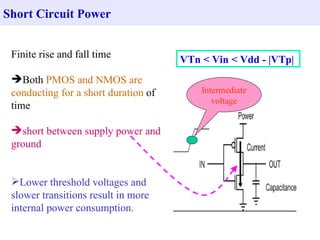

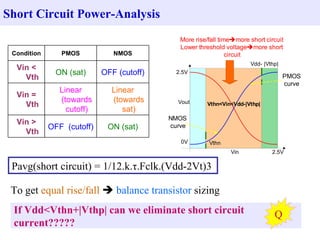

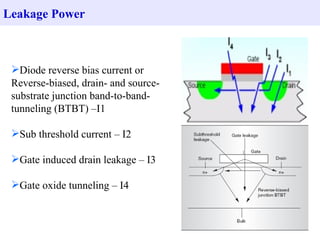

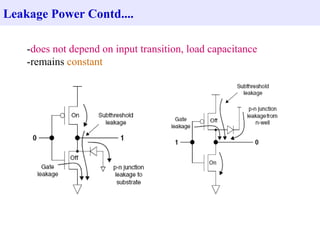

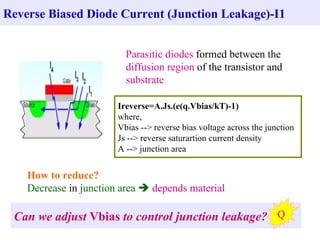

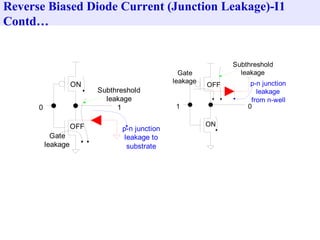

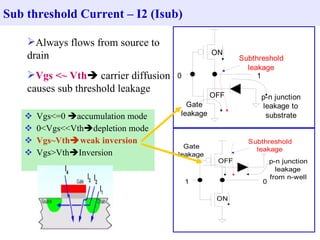

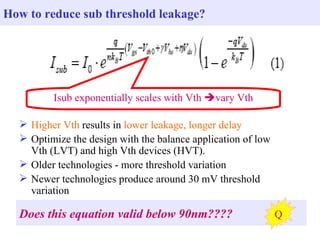

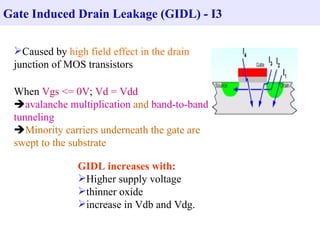

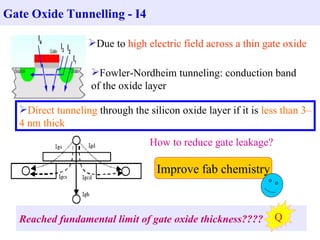

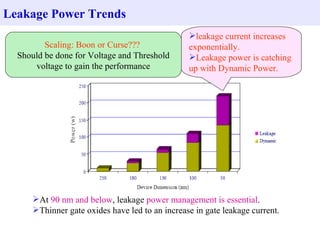

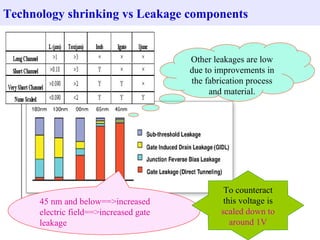

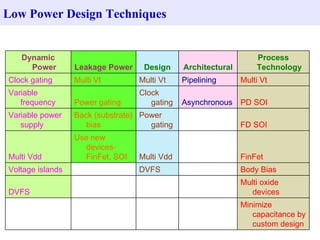

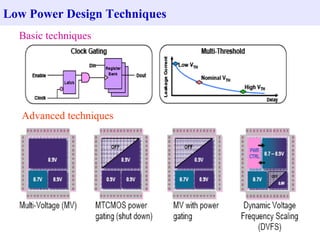

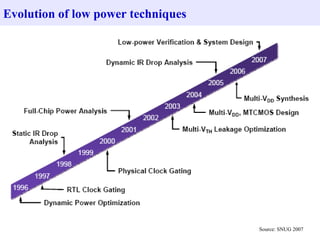

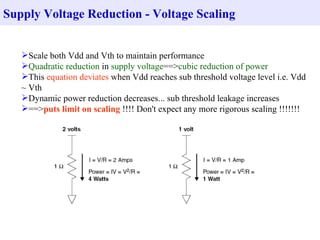

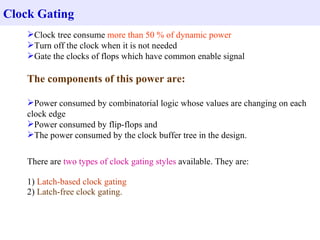

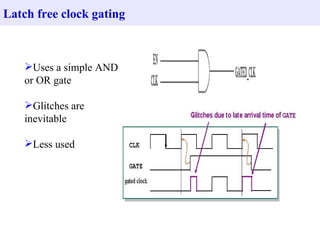

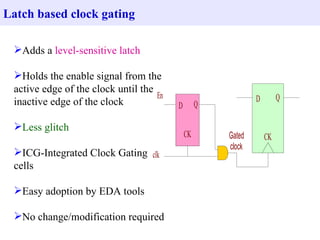

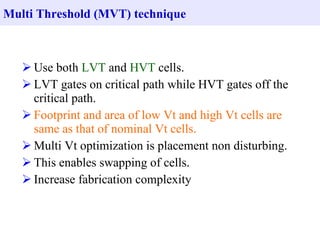

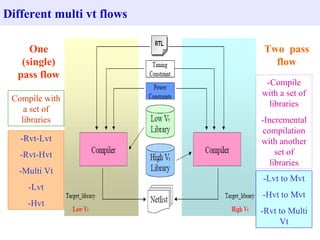

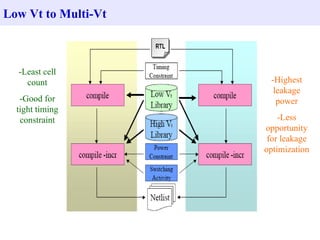

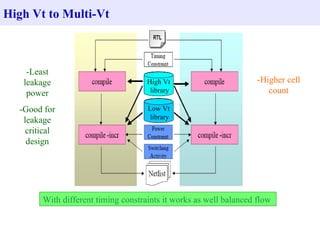

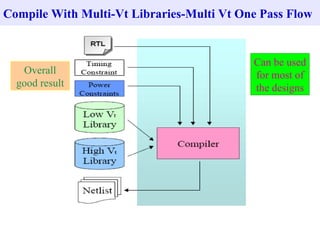

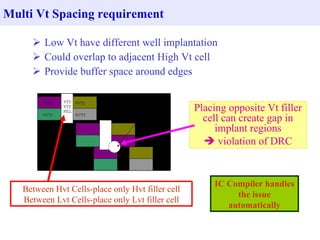

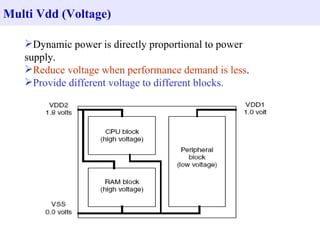

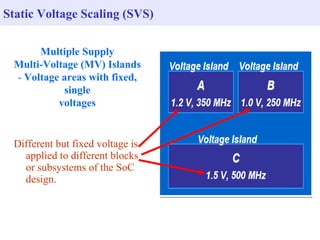

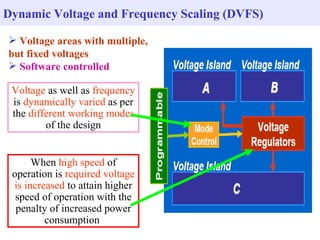

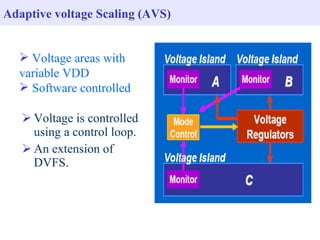

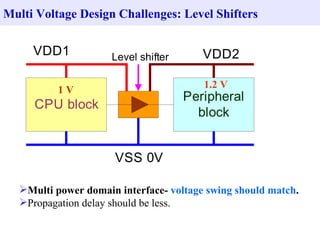

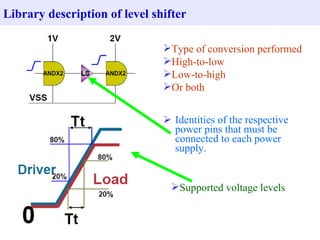

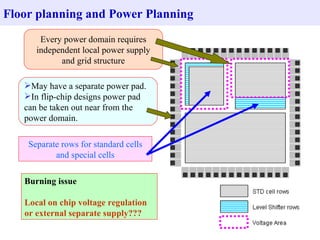

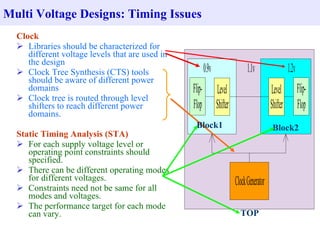

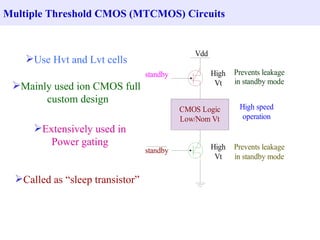

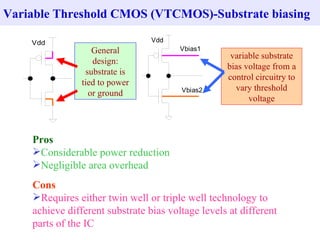

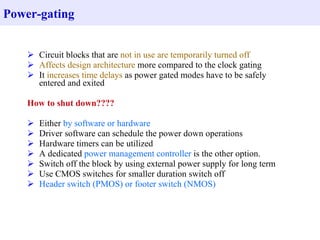

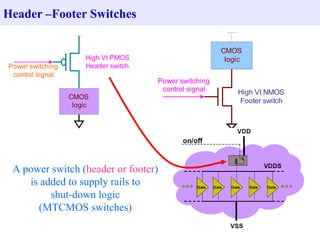

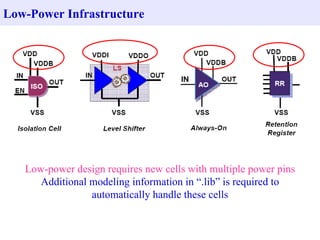

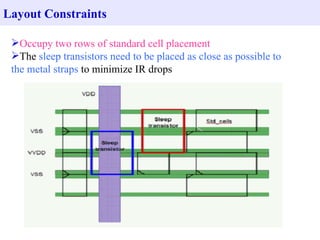

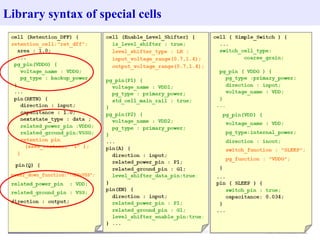

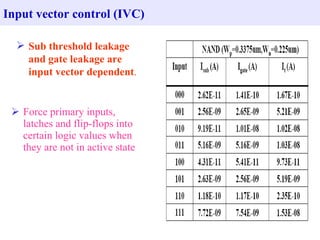

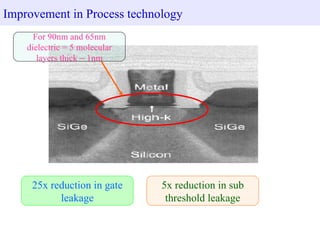

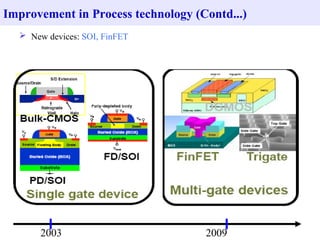

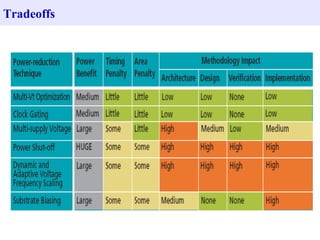

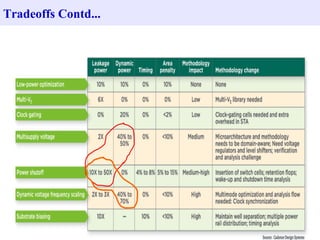

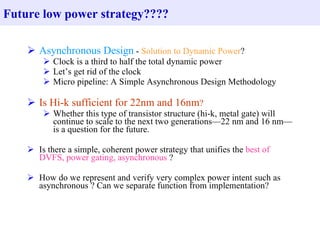

This document discusses various low power techniques for integrated circuits. It begins by describing the increasing challenges of power consumption as device densities and clock frequencies increase while supply voltages and threshold voltages decrease. It then discusses different types of power consumption, including dynamic power, static power, leakage power from different sources, and how they can be reduced. The document covers many low power design techniques like multi-threshold CMOS, clock gating, multi-voltage, DVFS, and more. It discusses the evolution of these techniques and challenges in their implementation like timing issues, level shifters, and floorplanning for multi-voltage designs.