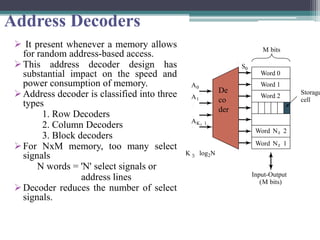

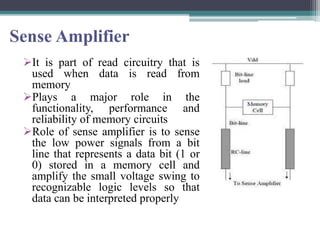

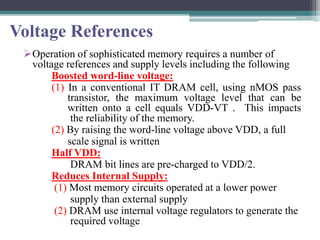

This document discusses memory circuits and techniques to reduce power consumption in memories. It describes the key components of memory control units including address decoders, sense amplifiers, voltage references, drivers/buffers, and timing and control circuits. Address decoders reduce the number of select signals needed for memory access. Sense amplifiers amplify signals from memory cells for data readout. Various voltage references are needed for memory operation. Power consumption comes from the memory cell array, decoders, and periphery circuits. Partitioning memory and reducing voltage levels can lower active power, while techniques like half VDD precharge and boosted word lines reduce DRAM retention power. Turning off unused blocks and increasing thresholds cuts SRAM retention power.

![IDD = Iarray+Idecoder+Iperiphery

= [miact+m(n-1)ihld]+[(n+m)CDE VINT f] +

[CPTVINTf+IDCP]](https://image.slidesharecdn.com/ec6601vlsidesign-memorycircuits-190810154544/85/EC6601-VLSI-Design-Memory-Circuits-10-320.jpg)