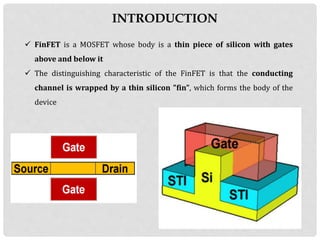

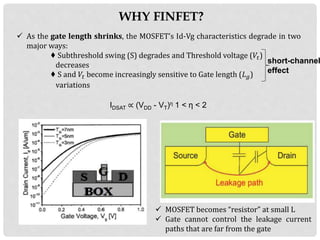

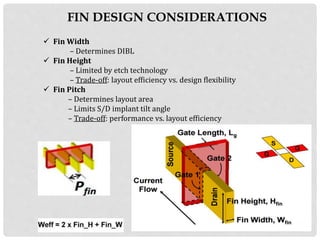

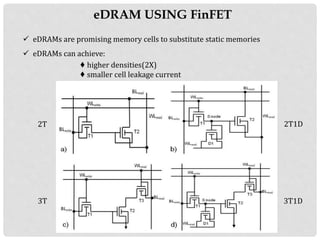

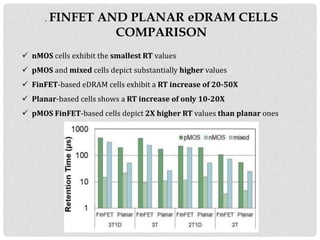

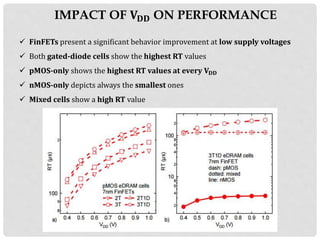

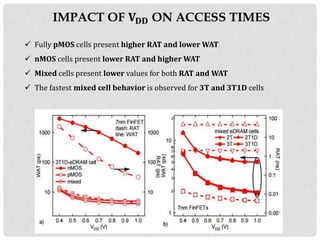

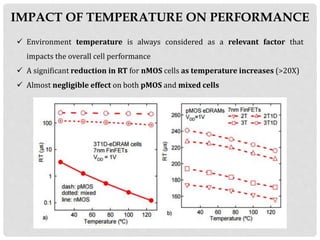

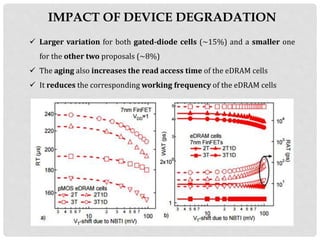

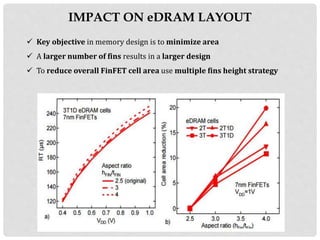

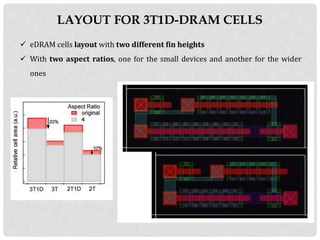

This document discusses the use of FinFET technology for embedded DRAM (eDRAM) cells. It begins with an introduction of FinFET transistors and why they are useful for advanced nodes. It then covers reliability issues, parameters of eDRAM cells, and comparisons between FinFET and planar eDRAM cells. The document analyzes the impact of supply voltage, temperature, device degradation, and layout on eDRAM cell performance. It concludes that FinFETs avoid issues faced by planar MOSFETs and can achieve a 2x improvement in retention time for eDRAM cells.