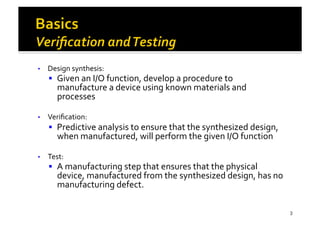

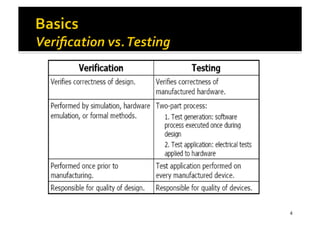

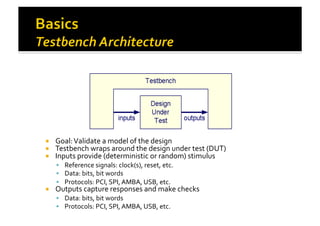

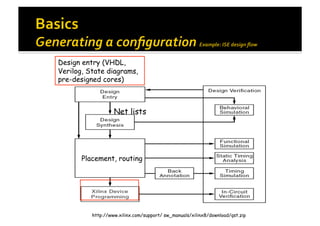

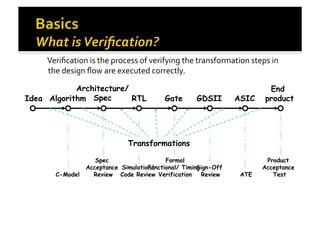

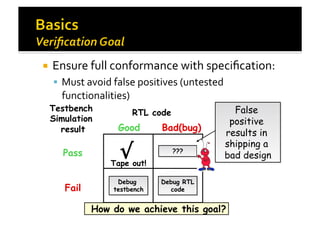

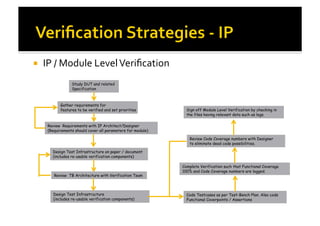

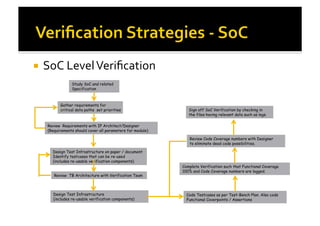

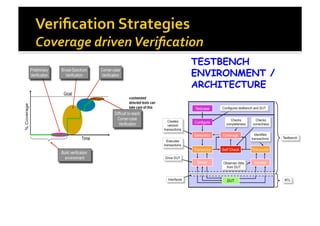

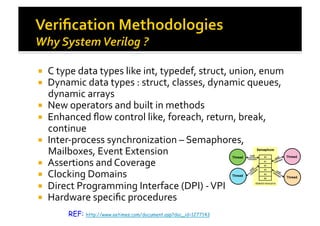

This document outlines an agenda for a presentation on verification challenges, strategies, and methodologies. The presentation covers the basics of verification, challenges in verification, strategies like testbenches and coverage-driven verification, verification methodologies, the verification market and opportunities, skills needed, and concludes with a question and answer section. Key points include the importance of functional coverage to ensure all required functionality is tested, and that high code coverage alone is not sufficient to guarantee a design is fully verified.