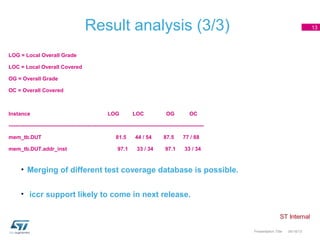

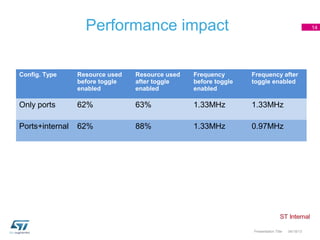

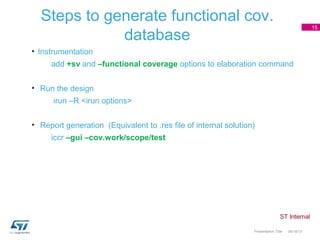

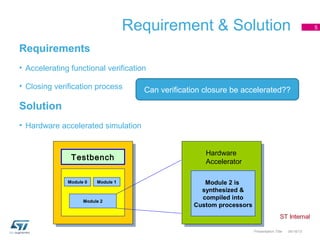

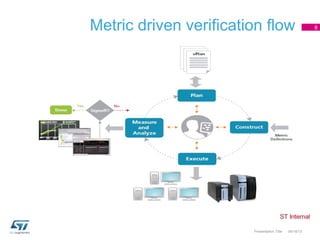

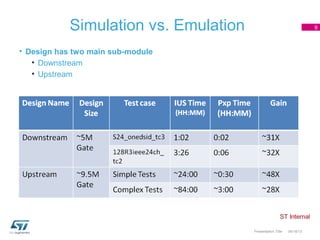

The document discusses using coverage to accelerate functional verification on emulators. It describes defining a test plan, running tests with coverage enabled, and analyzing coverage reports to focus on uncovered areas. Code coverage is demonstrated on an emulator with minimal performance impact. Functional coverage is also supported to further drive verification closure.

![Result analysis (2/3) 12

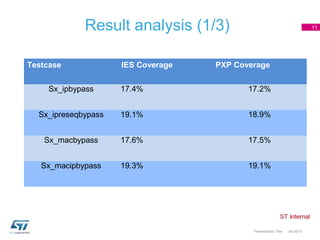

• Coverage results come in txt file as below

: Instance Name: mem_tb.DUT

File Name: mem.v

Hit(Full) Hit(Rise) Hit(Fall) Signal

1 1 1 clk

0 1 0 rst

<><><><><><><><><><><><><><><><><><><><><><><><><><><><>

: Instance Name: mem_tb.DUT.addr_inst

File Name: mem.v

Hit(Full) Hit(Rise) Hit(Fall) Signal

1 1 1 a[7]

0 1 0 out[7]

Presentation Title 04/18/13](https://image.slidesharecdn.com/dvclubdelhi-gupta-130418165528-phpapp02/85/Coverage-Solutions-on-Emulators-12-320.jpg)