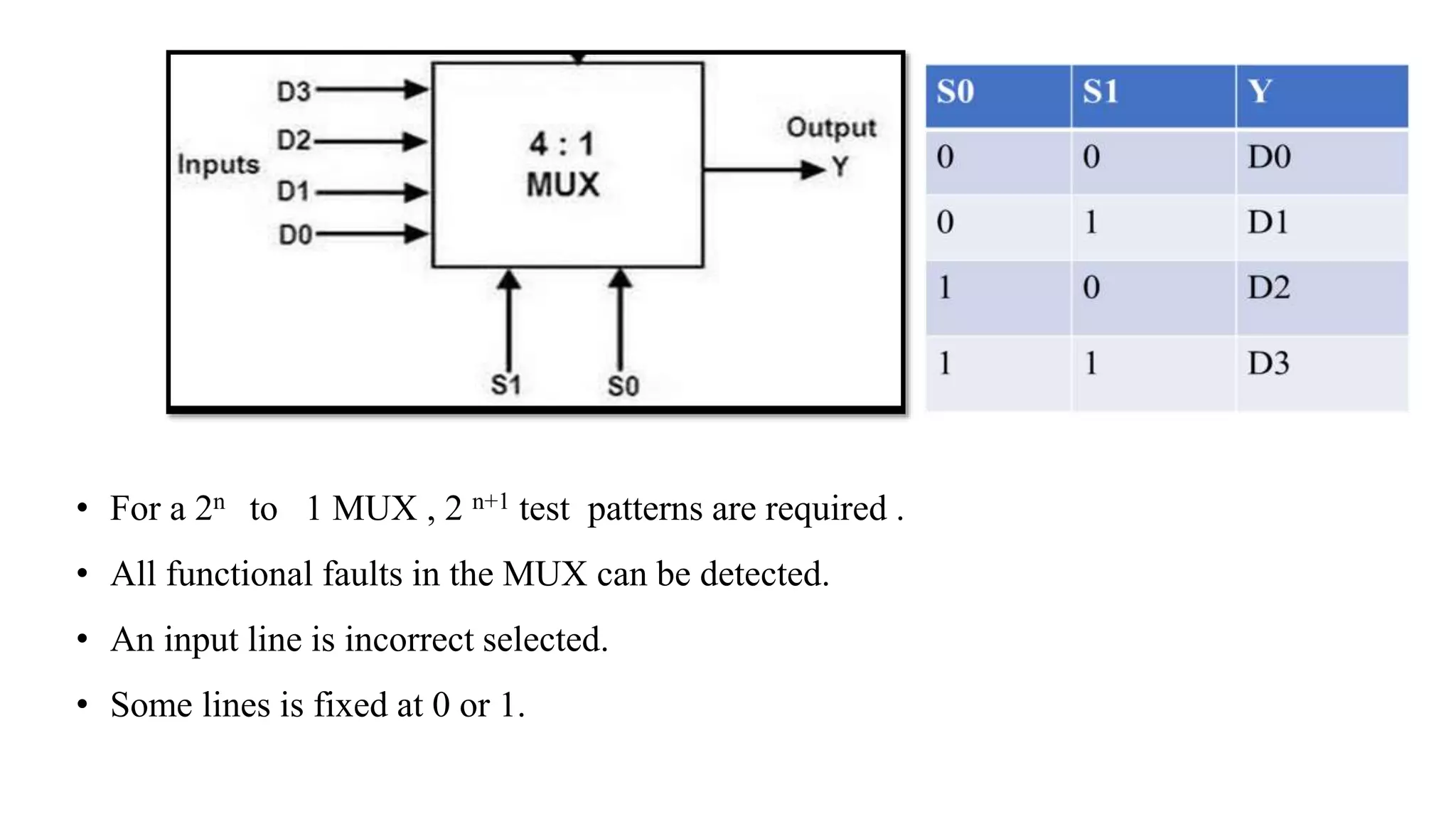

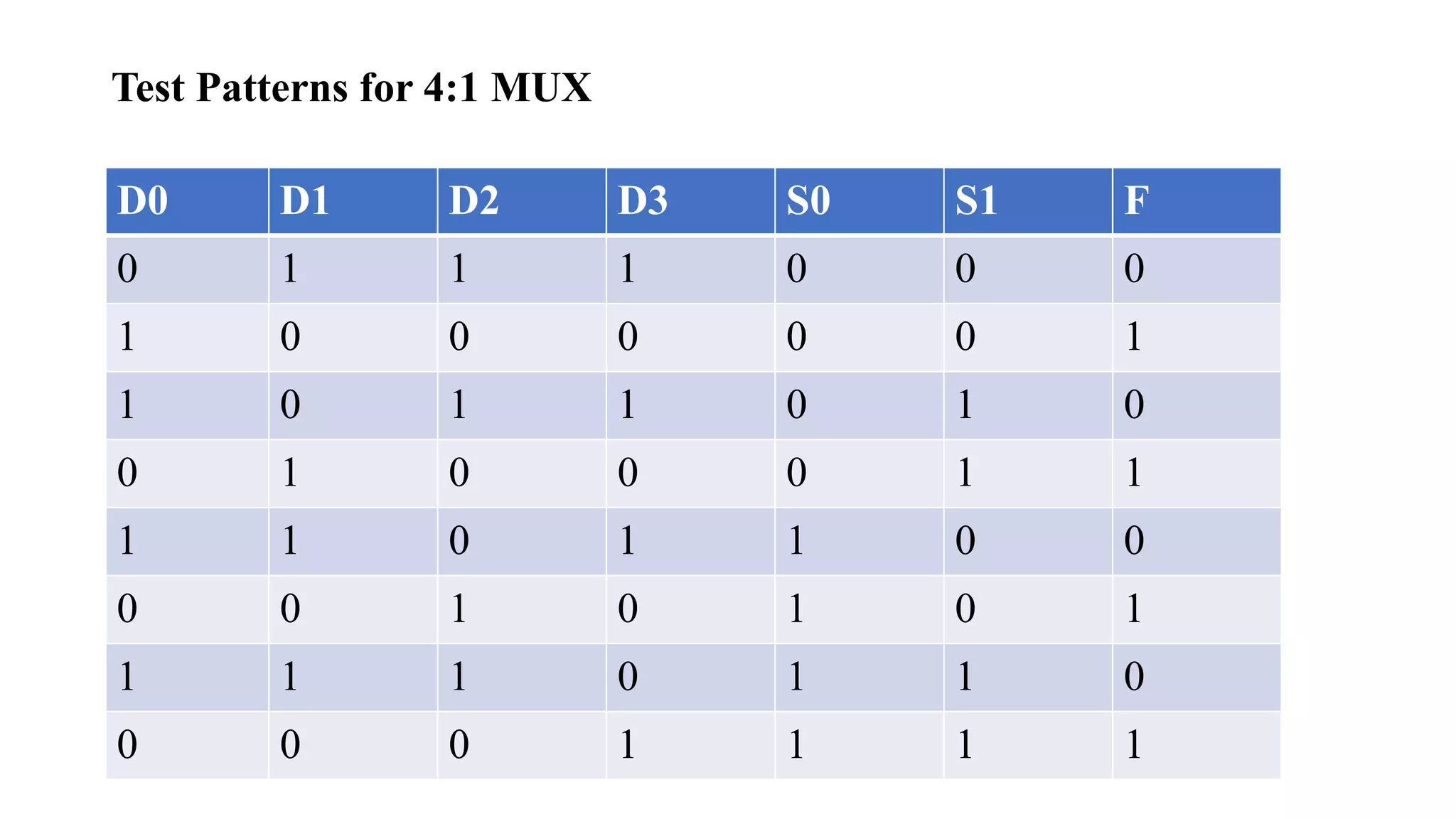

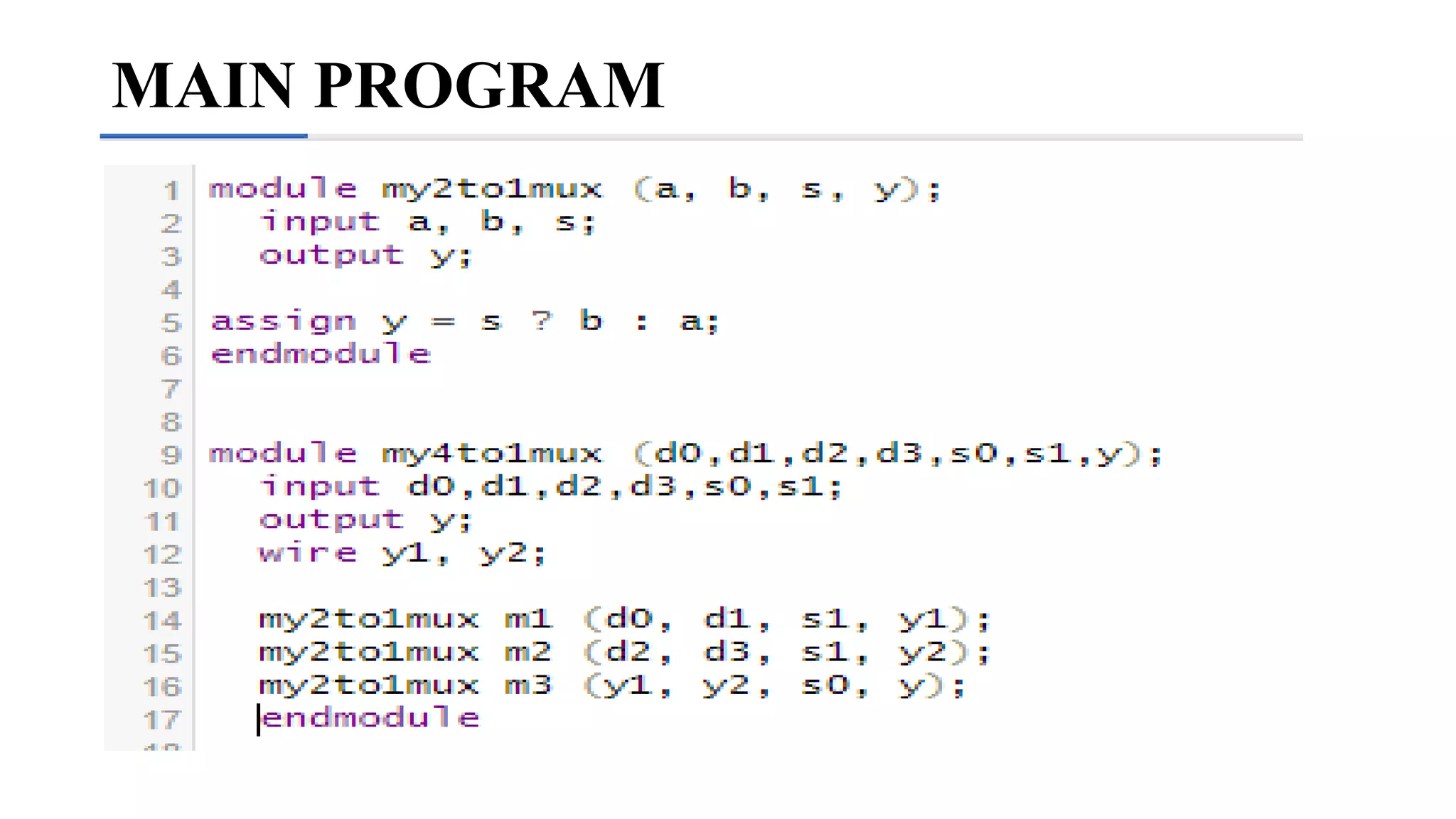

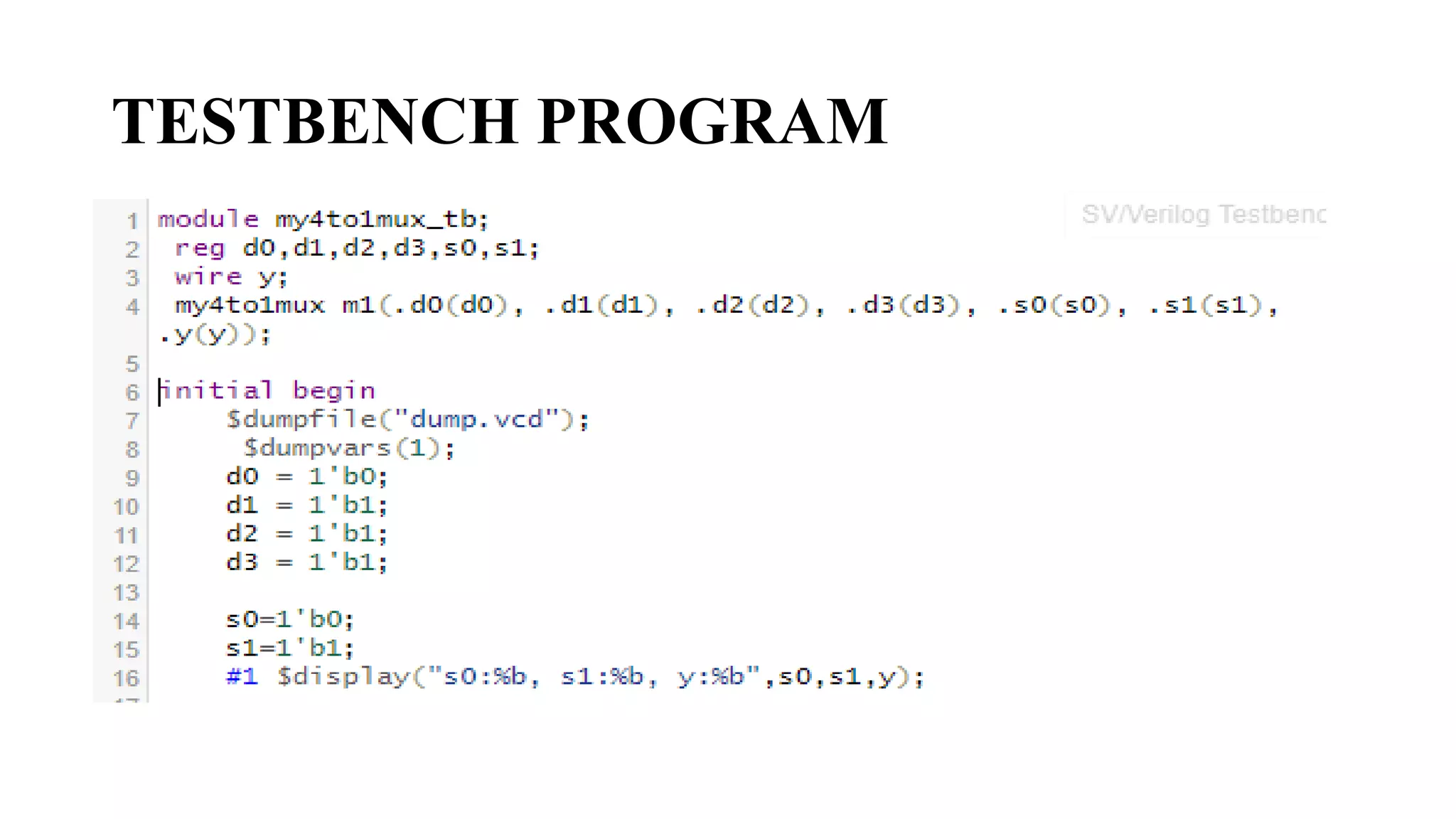

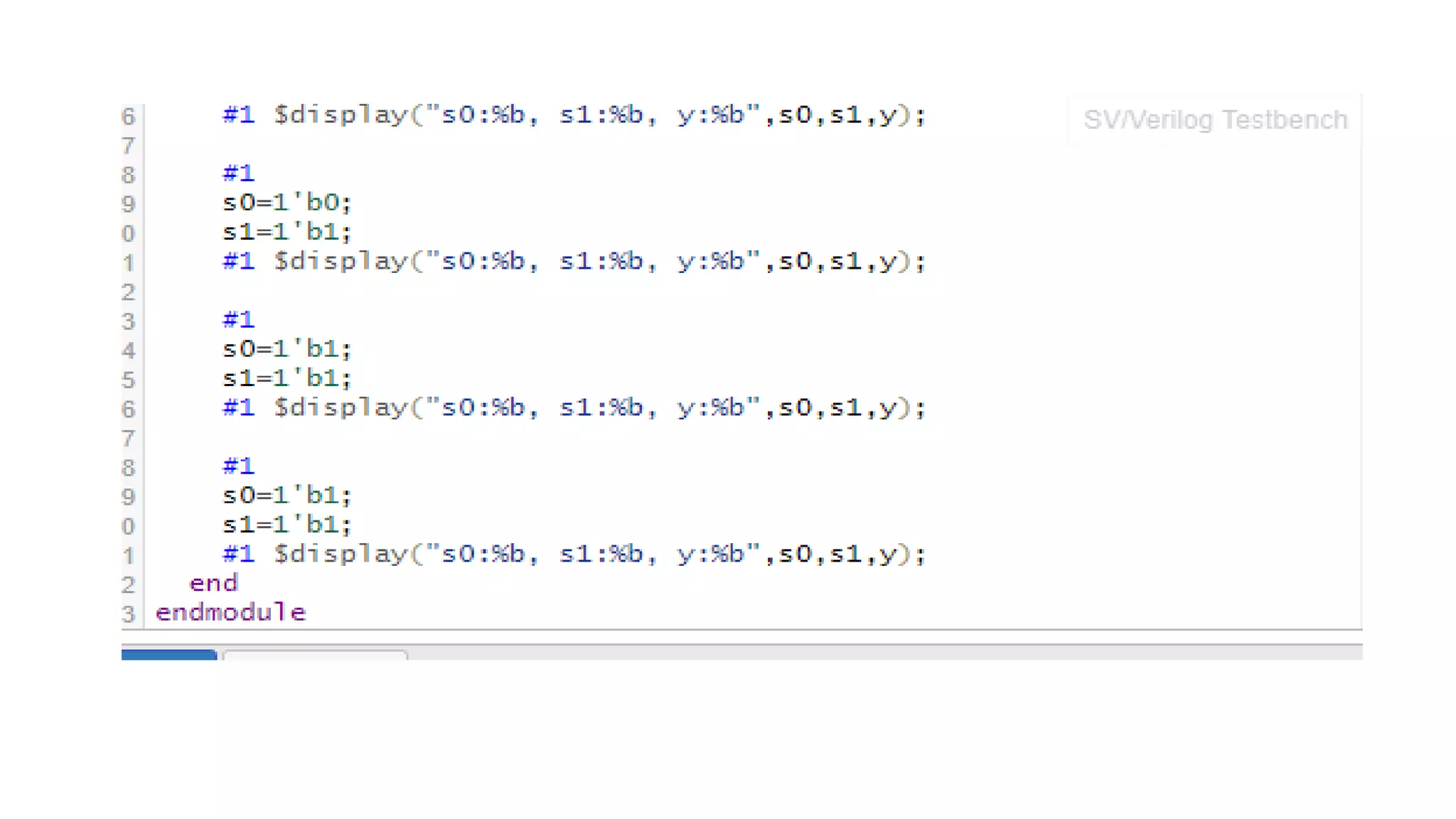

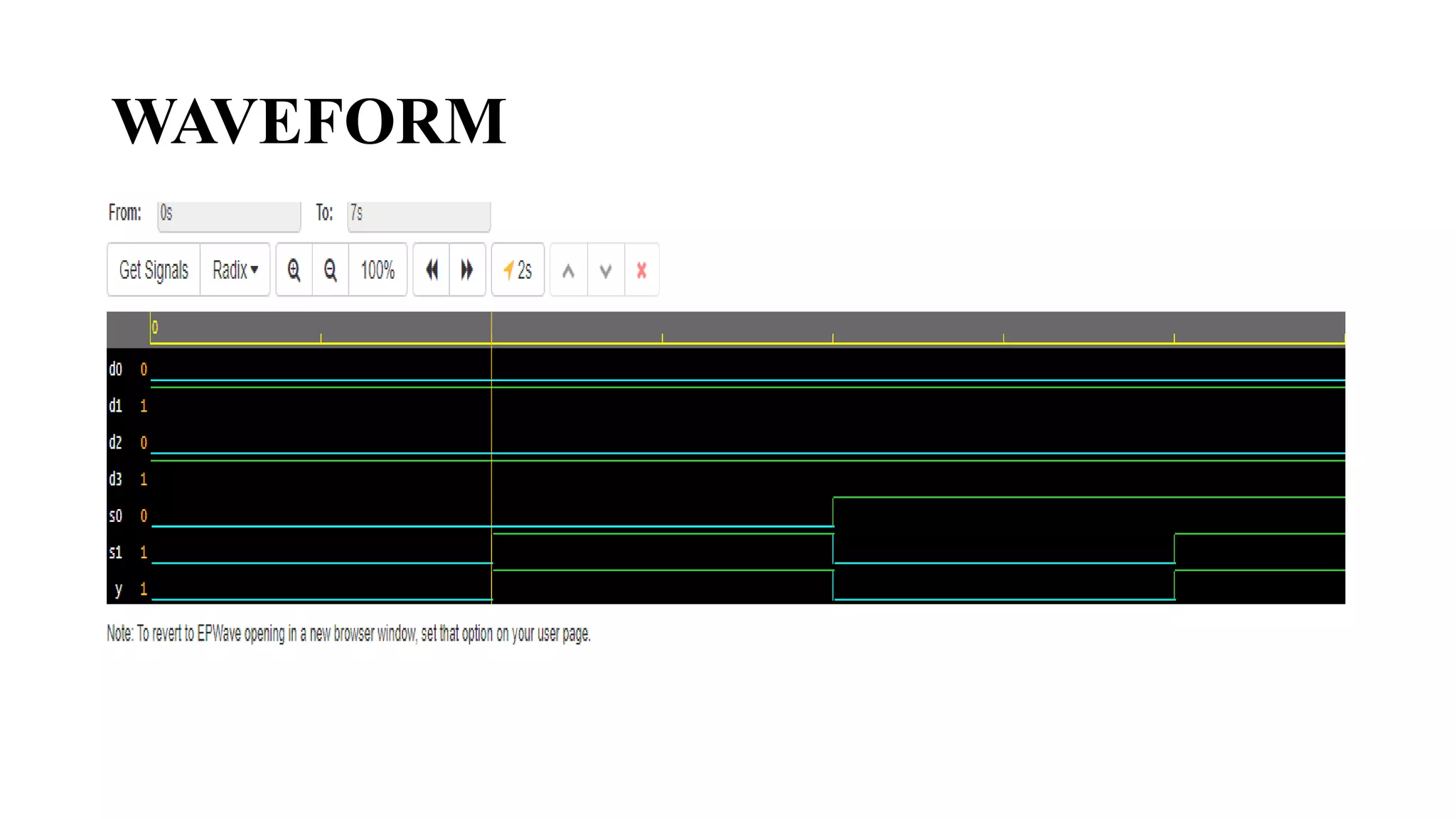

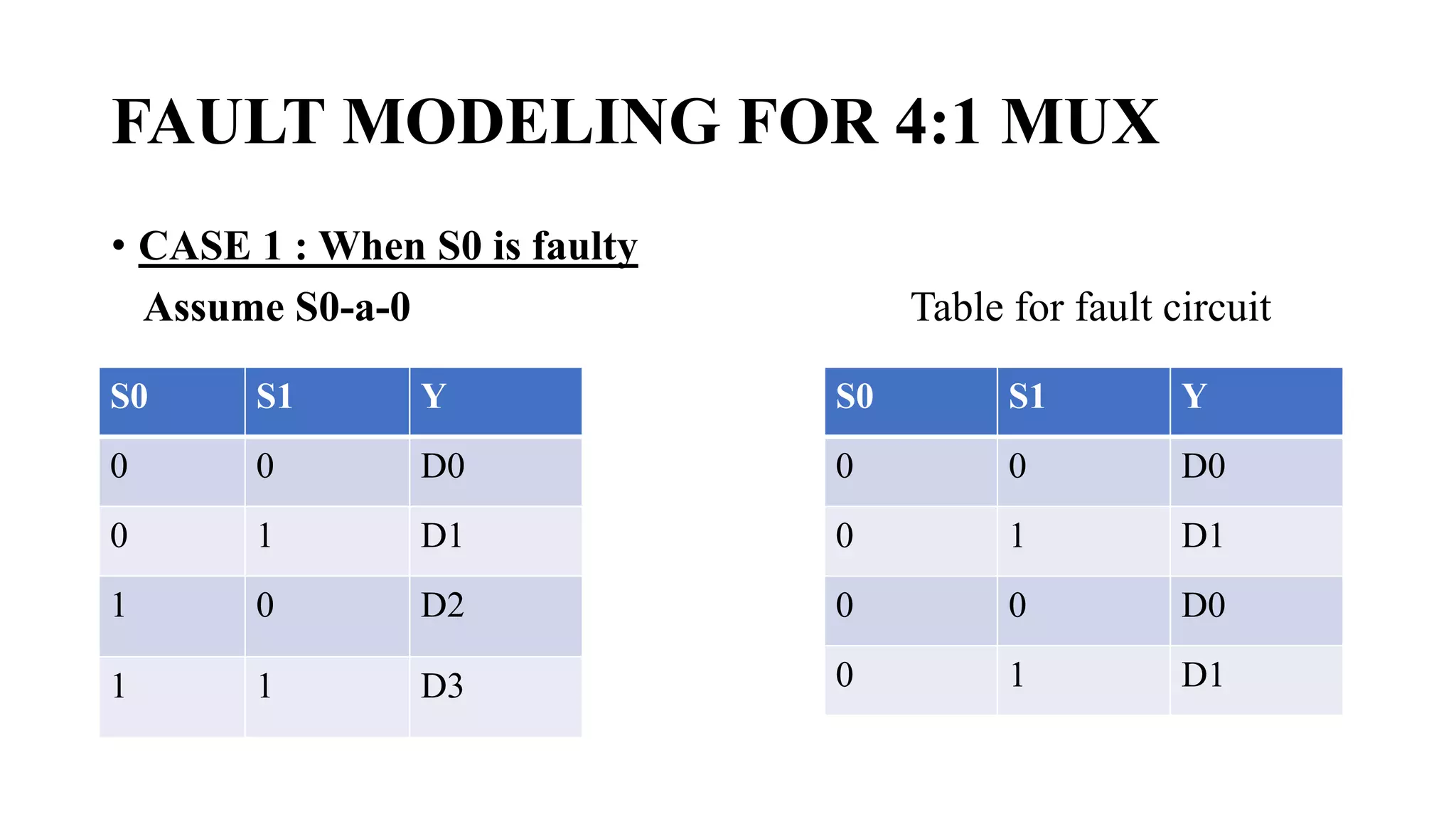

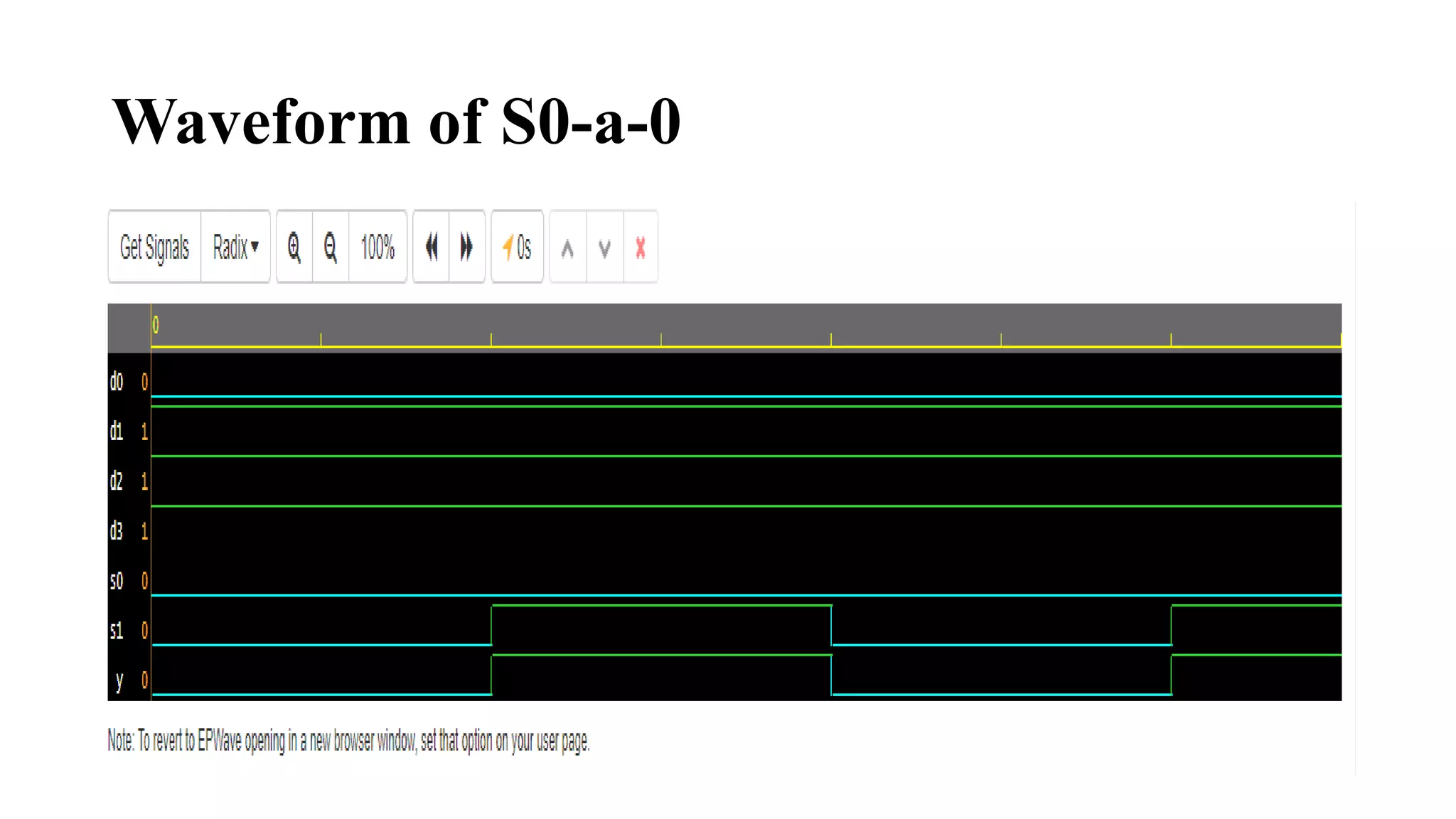

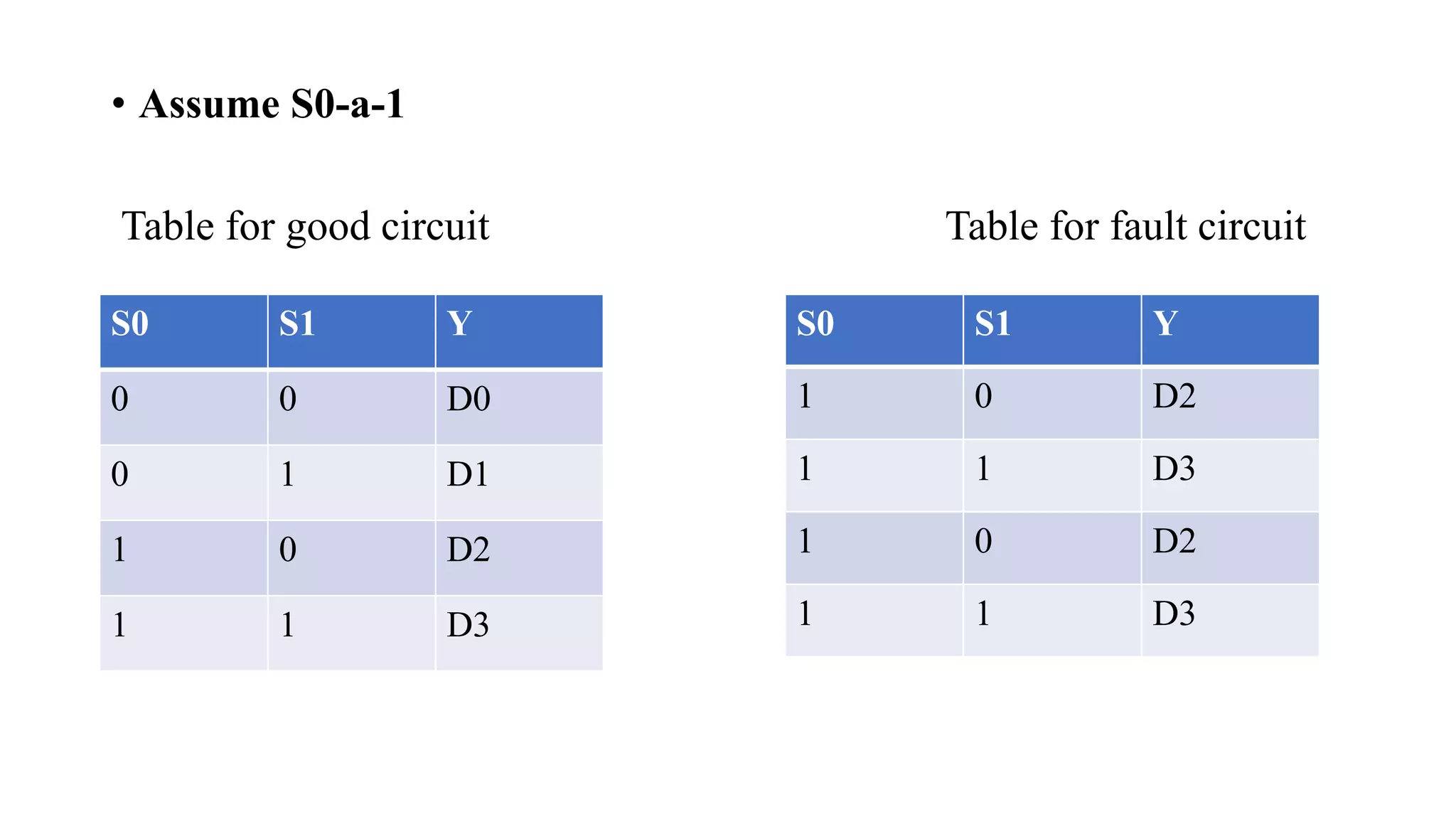

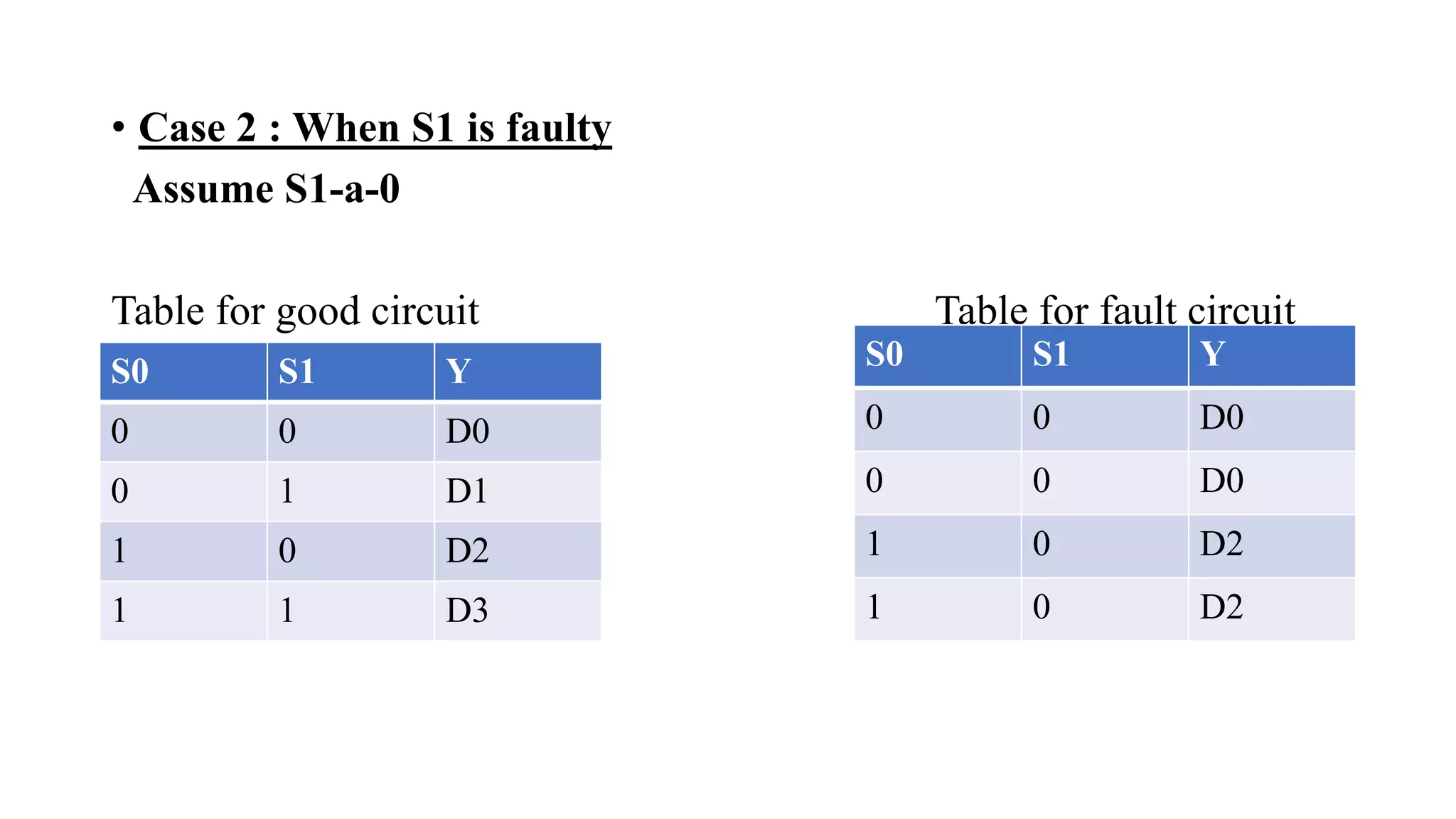

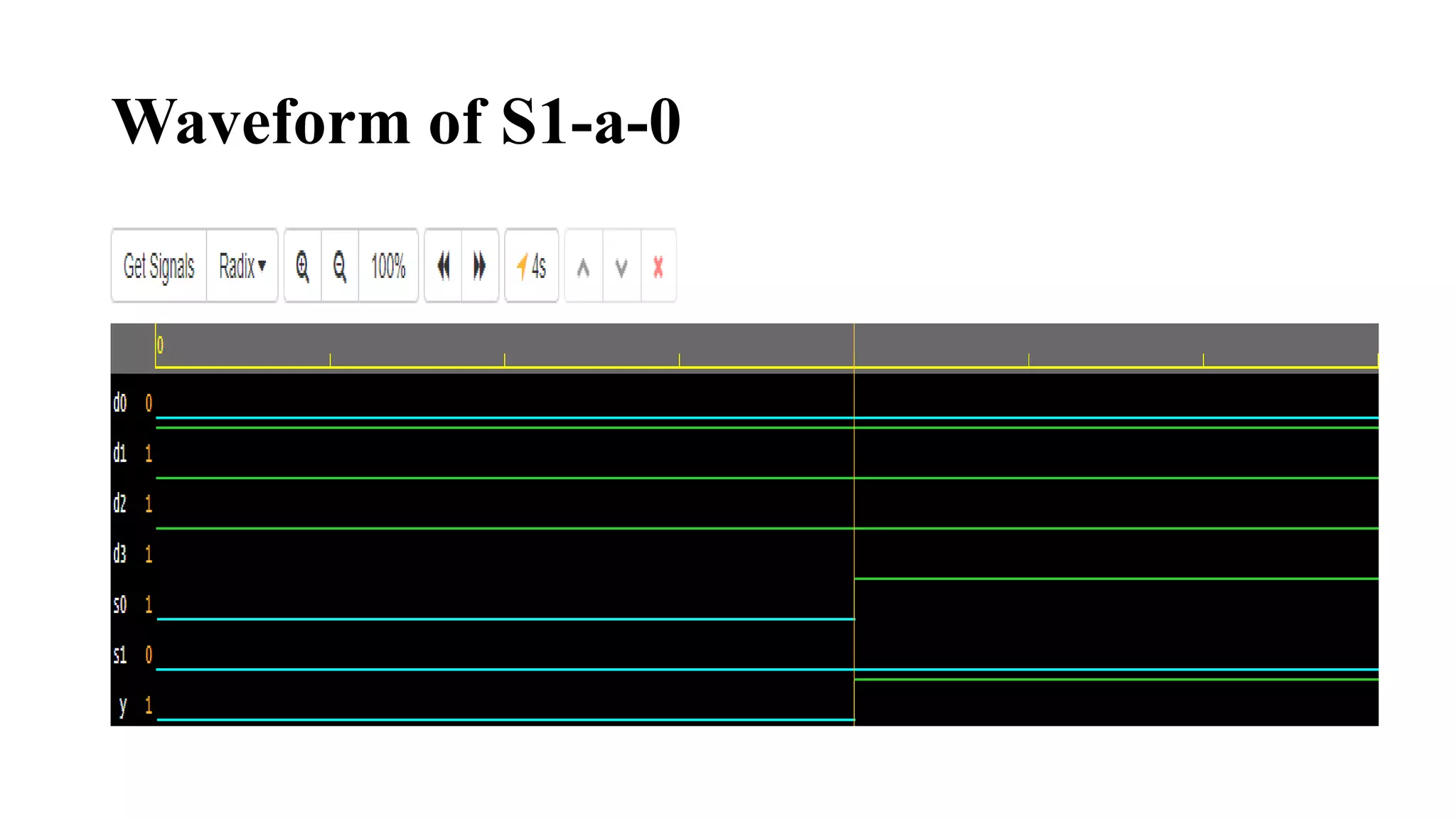

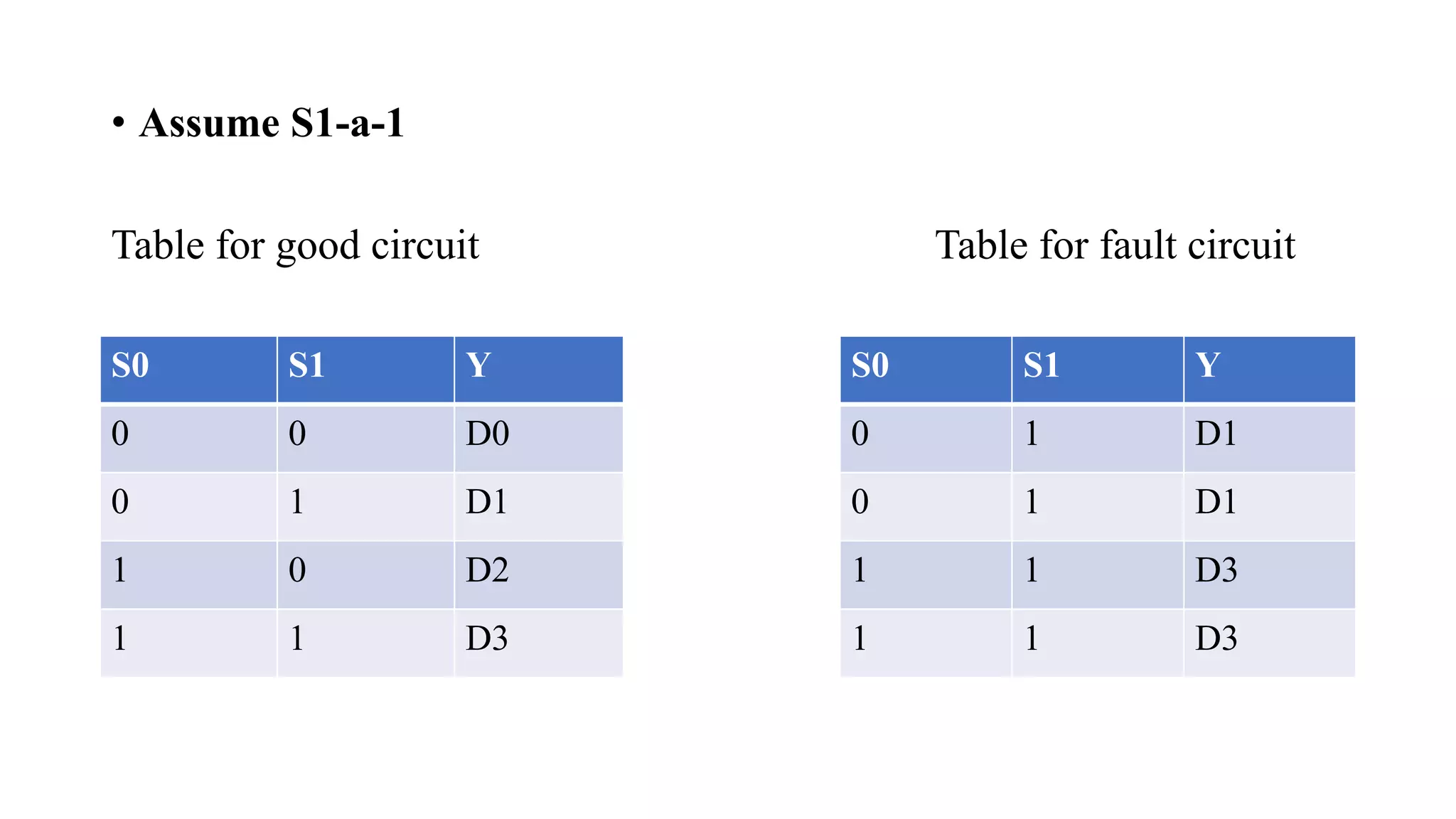

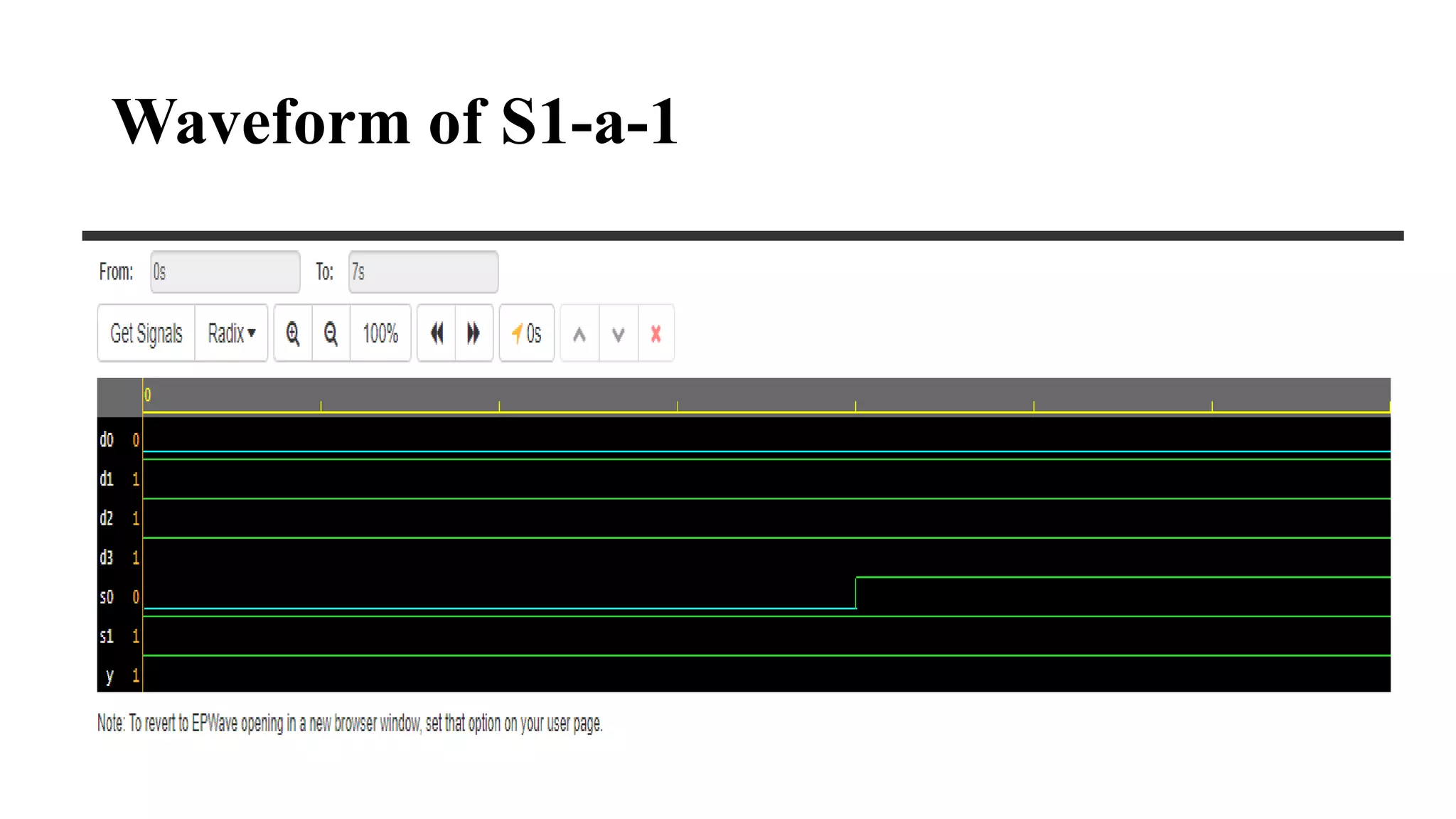

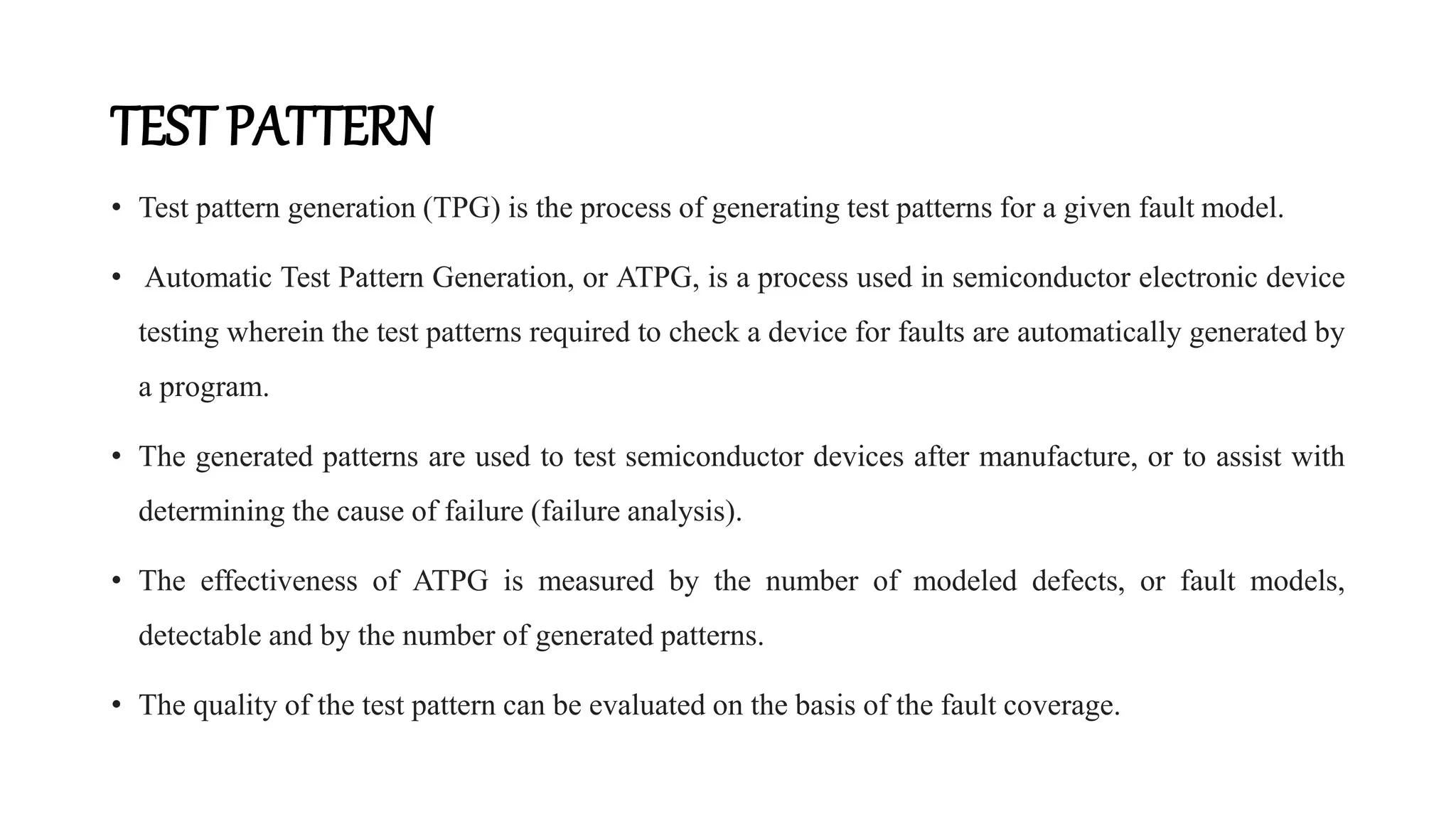

The document discusses test pattern generation for a 4:1 multiplexer (MUX). It provides the test patterns required to test all functional faults in a 4:1 MUX. There are 8 test patterns with different input combinations for the data (D0-D3) and selection lines (S0, S1). The document also analyzes fault modeling for the selection lines S0 and S1, considering stuck-at-0 and stuck-at-1 faults. It provides the expected output and sample waveforms for each of the faults.

![PROPERTIES OF THE GATE LEVEL SSF MODEL :

1) Boolean components are assumed to be fault-free.

2) Signal lines contain faults:

• a stuck-at-zero (s-a-0) fault when the logic level is fixed at value 0

• a stuck-at-one (s-a-1) fault when the logic level is fixed at value

(3) According to the single fault (SSF) assumption, only one fault is applied at a time when a test

set is either being created or evaluated.

(4) The fault-list is collapsed using the “check-point” theorem [ABR90]. The collapsed fault-list

of a module contains input as well as fan-out faults. Further collapsing may be done using

structural equivalence and dominance relationships.](https://image.slidesharecdn.com/mux-210906173856/75/Test-pattern-Generation-for-4-1-MUX-14-2048.jpg)