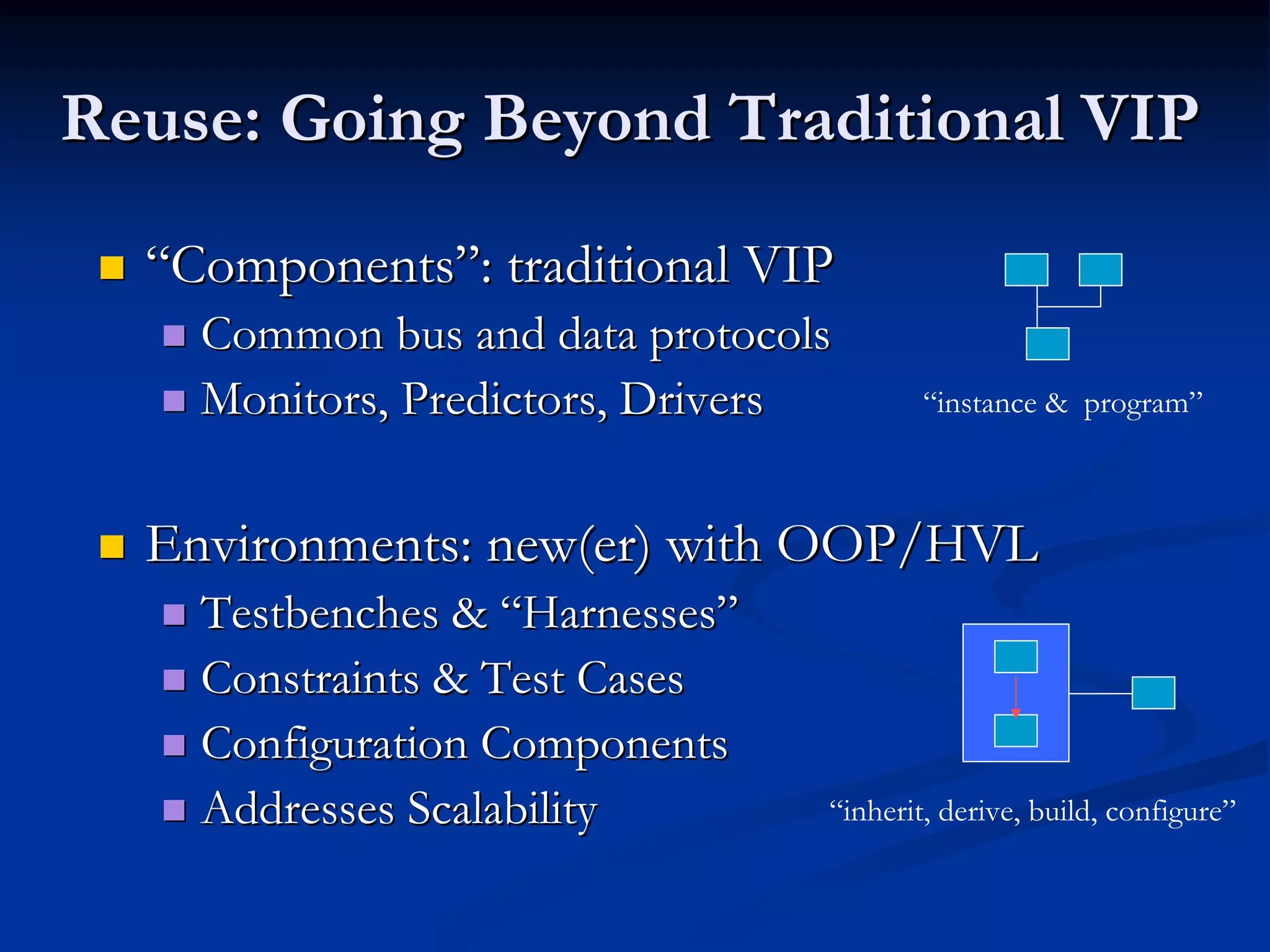

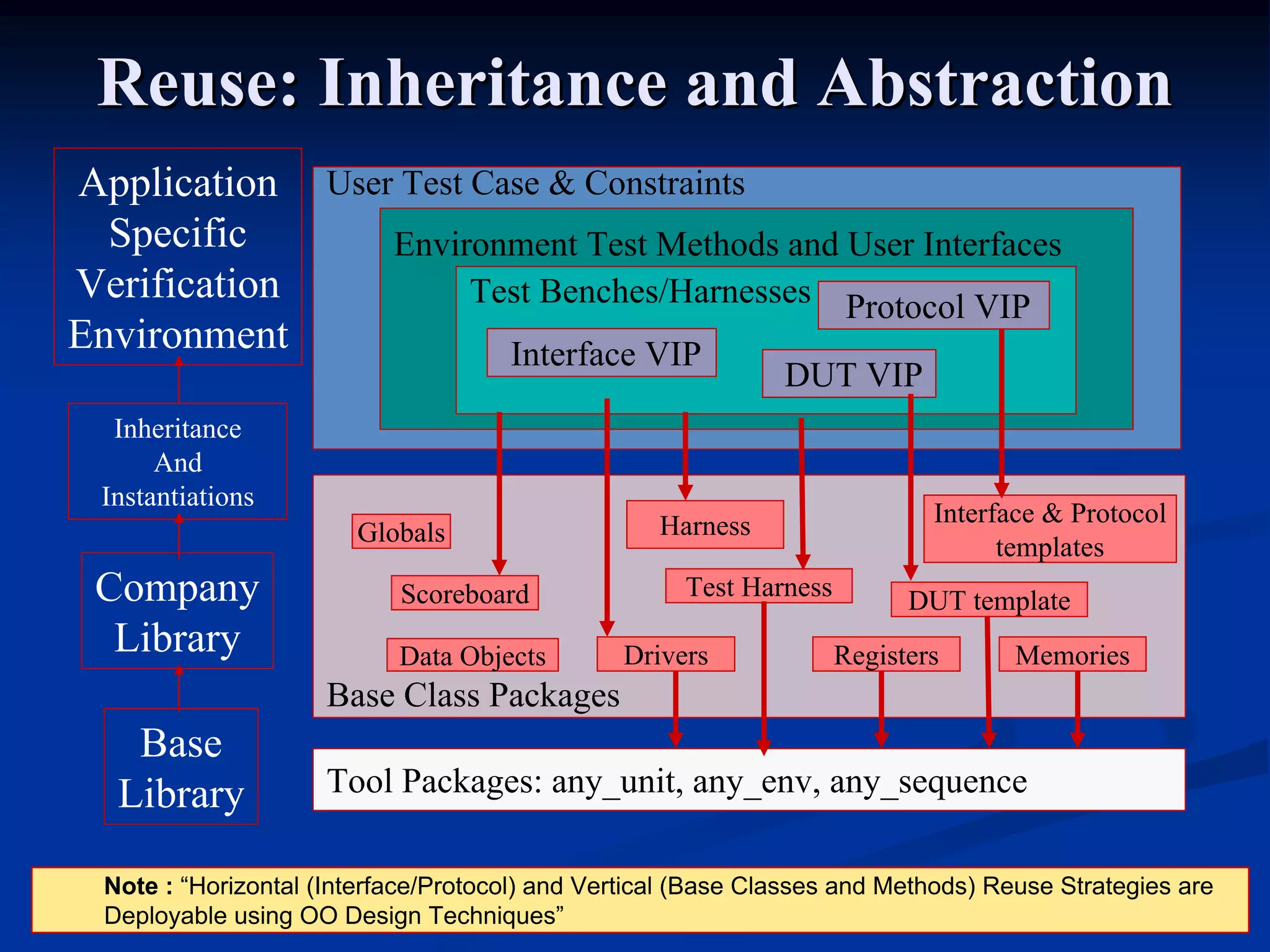

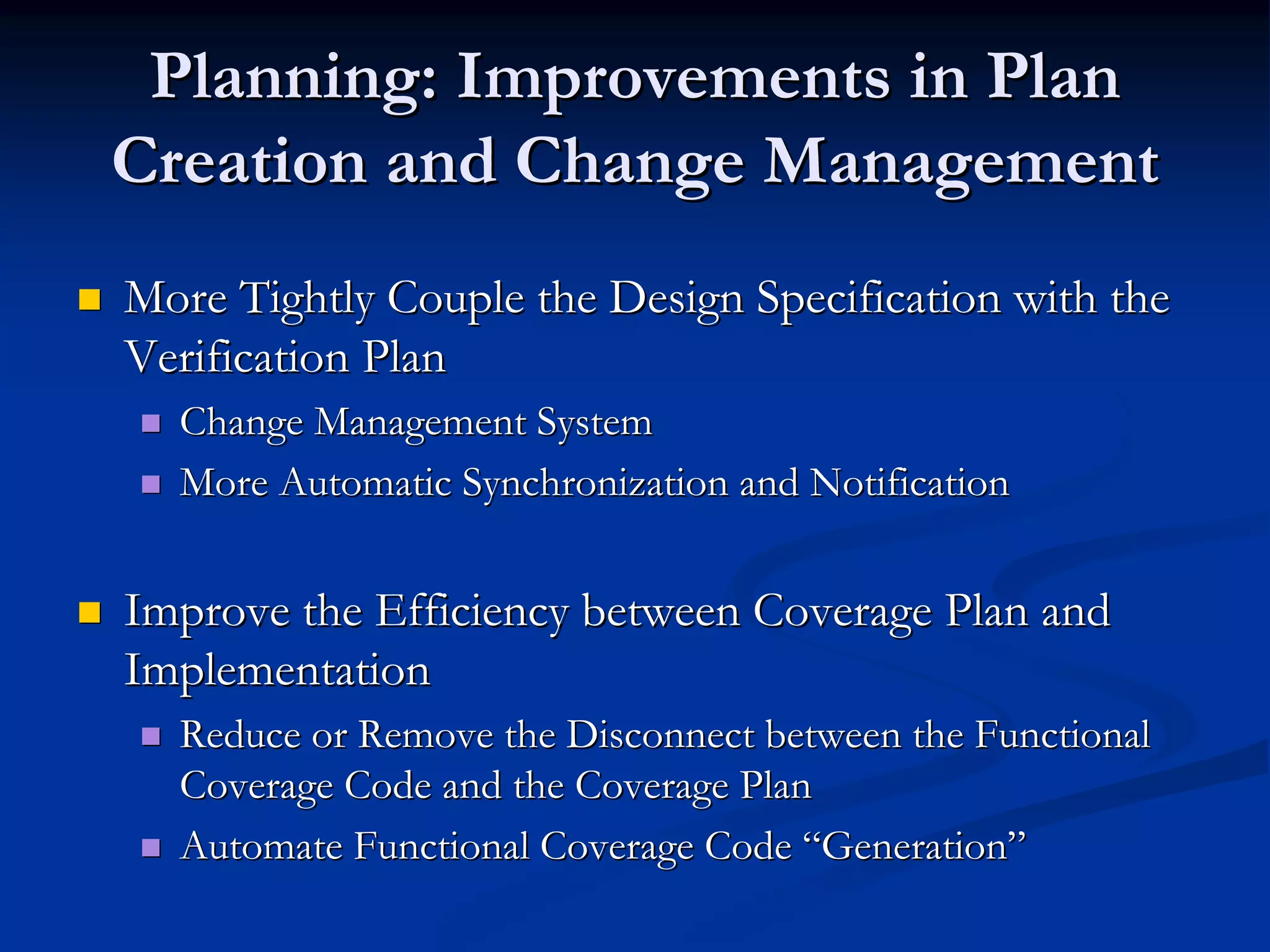

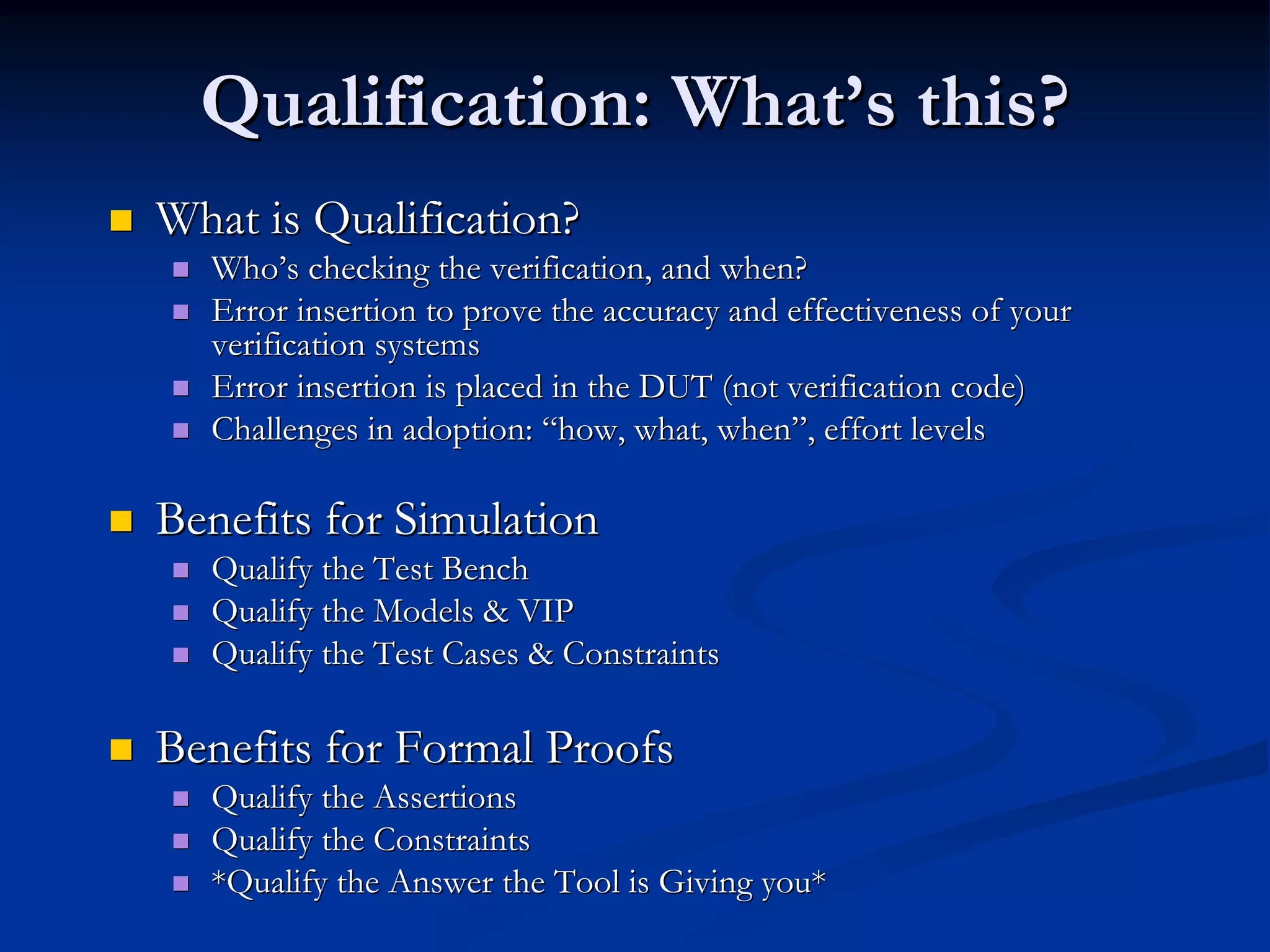

The document discusses topics in verification including reuse, coverage, regression engineering, planning, and qualification. It provides an overview of a voluntary community-based verification group called DVClub that discusses present day challenges in verification. The group has an advisory board of about 10 members from 6 companies. Topics discussed at meetings should relate to chip verification and may cover adjacent areas like design for verification, IT, and project management.