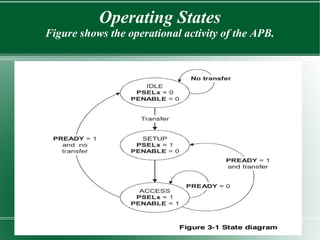

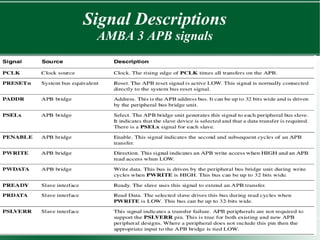

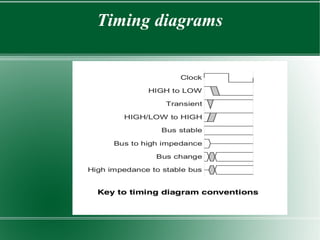

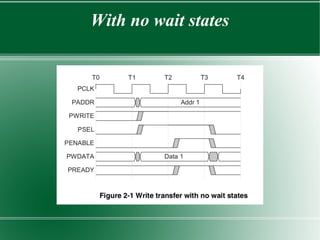

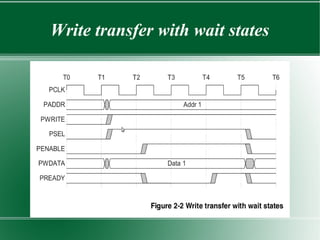

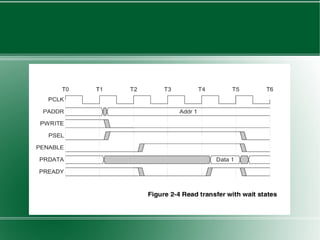

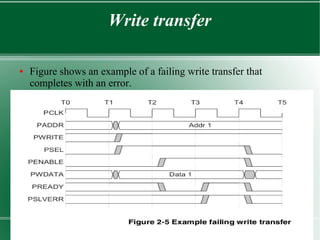

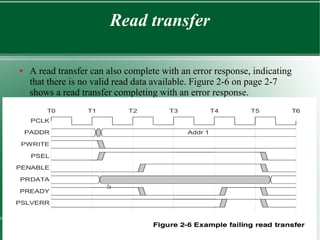

The document describes conventions and signals used in the AMBA 3 APB protocol specification version 1.0. It summarizes write and read transfer procedures, including optional wait states using the PREADY signal. Error responses are also described. The operating states of the APB include IDLE, SETUP, and ACCESS states. PREADY controls exiting the ACCESS state.

![Mapping of PSLVERR

● When bridging:

● From AXI to APB An APB error is mapped back to

RRESP/BRESP = SLVERR. This is achieved by mapping

PSLVERR to the AXI signals RRESP[1] for reads and

BRESP[1] for writes.

● From AHB to APB PSLVERR is mapped back to HRESP =

ERROR for both reads and writes. This is ac](https://image.slidesharecdn.com/apbppt-151203045605-lva1-app6892/85/APB-protocol-v1-0-24-320.jpg)