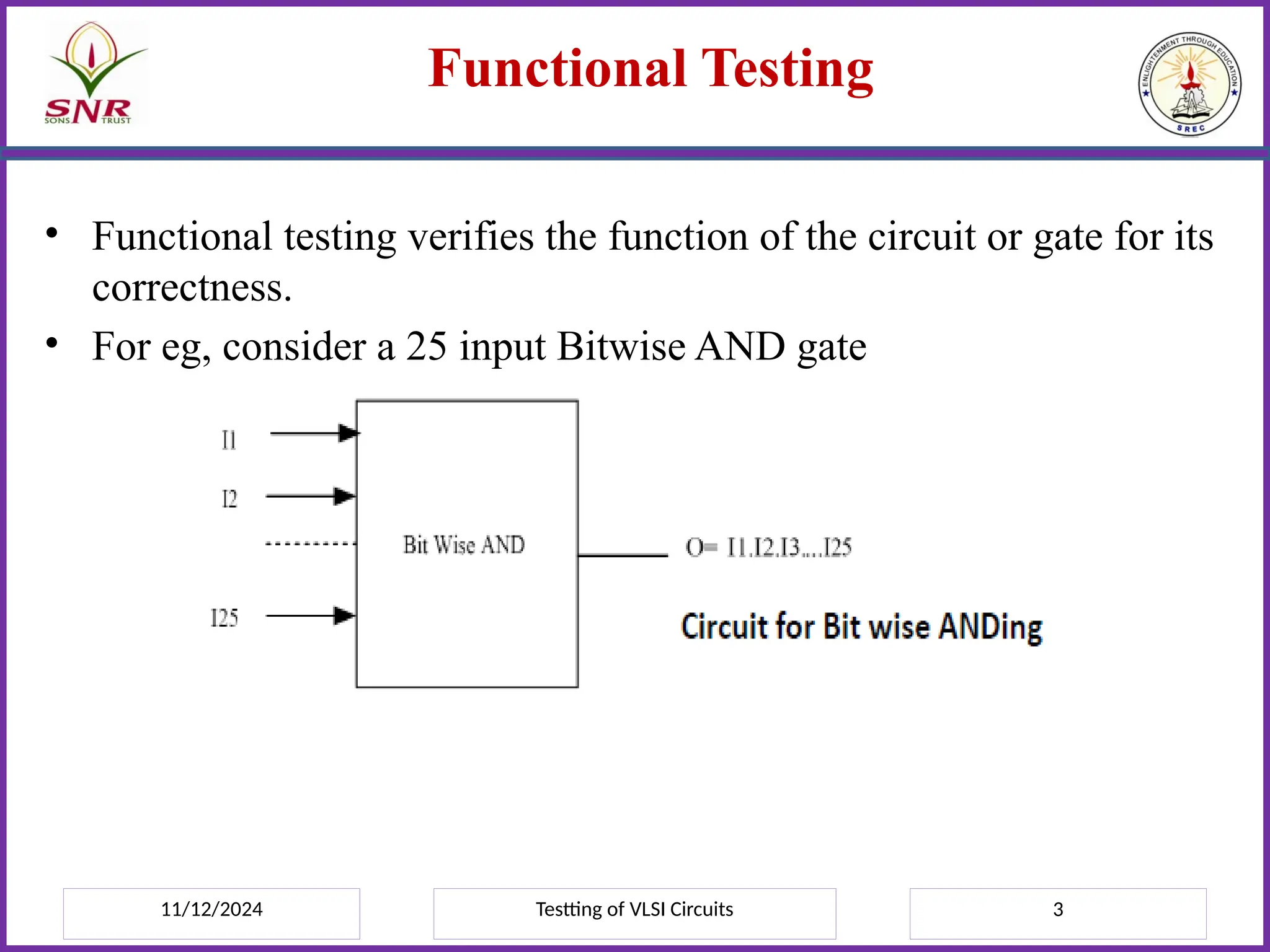

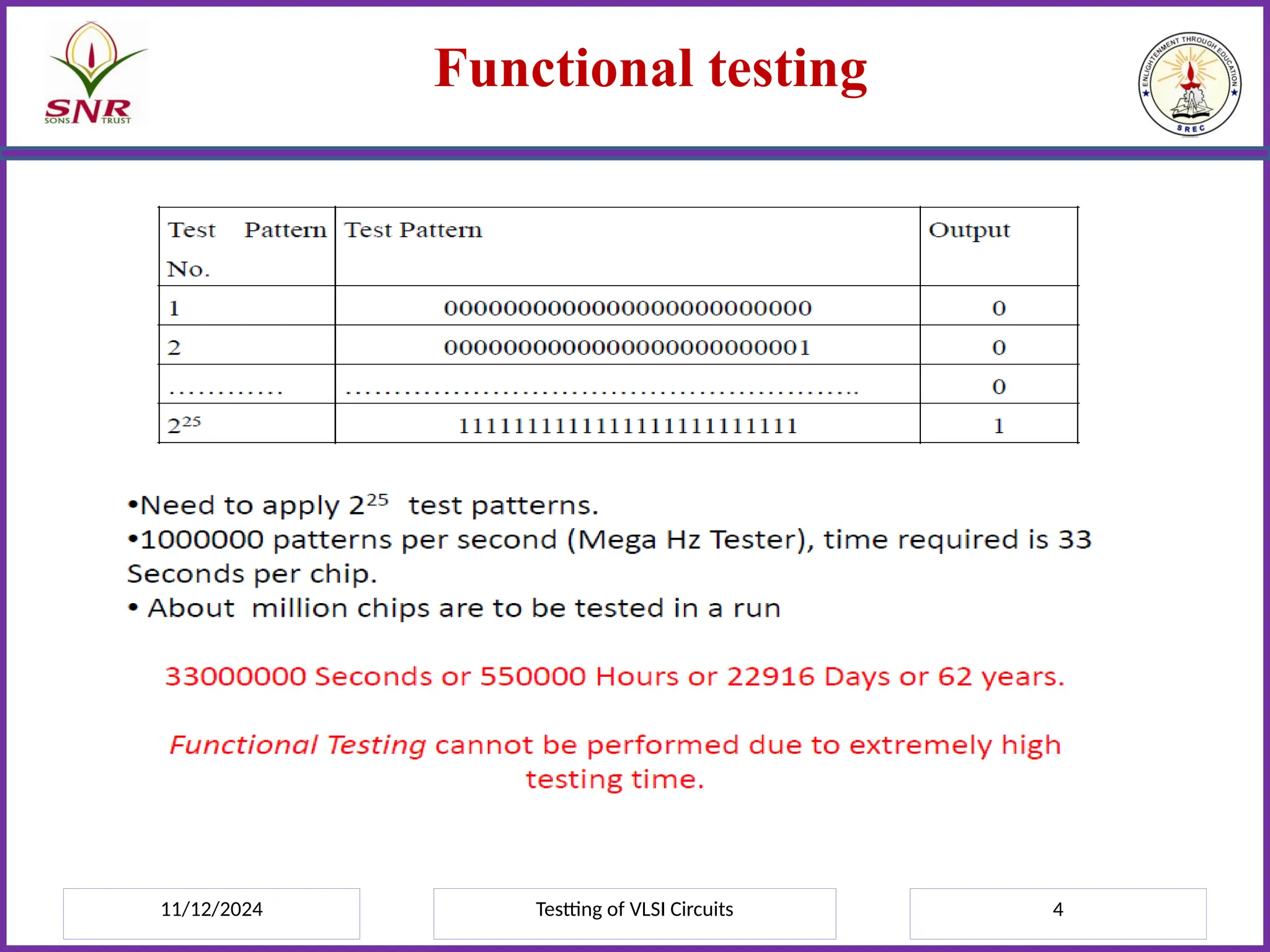

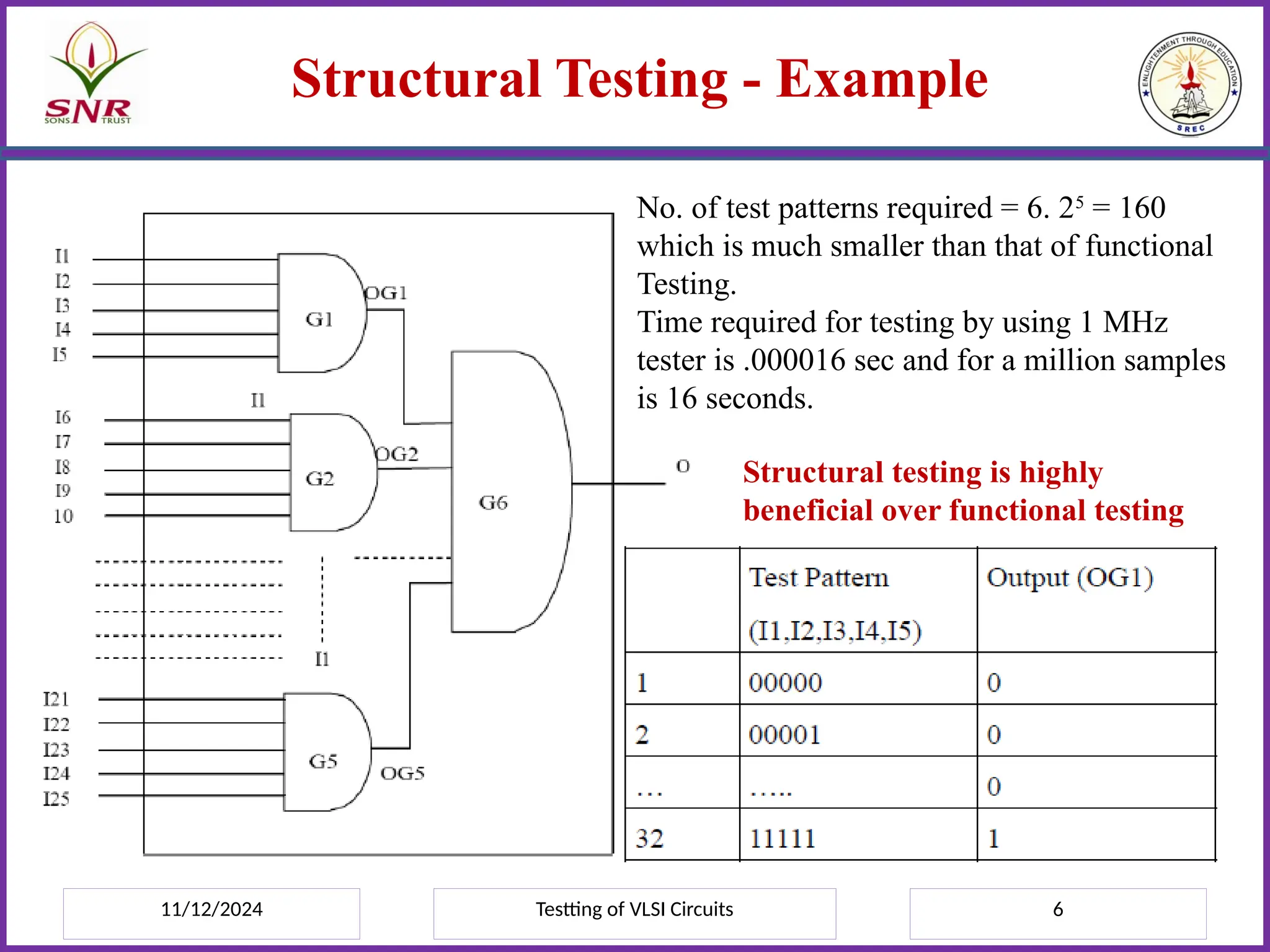

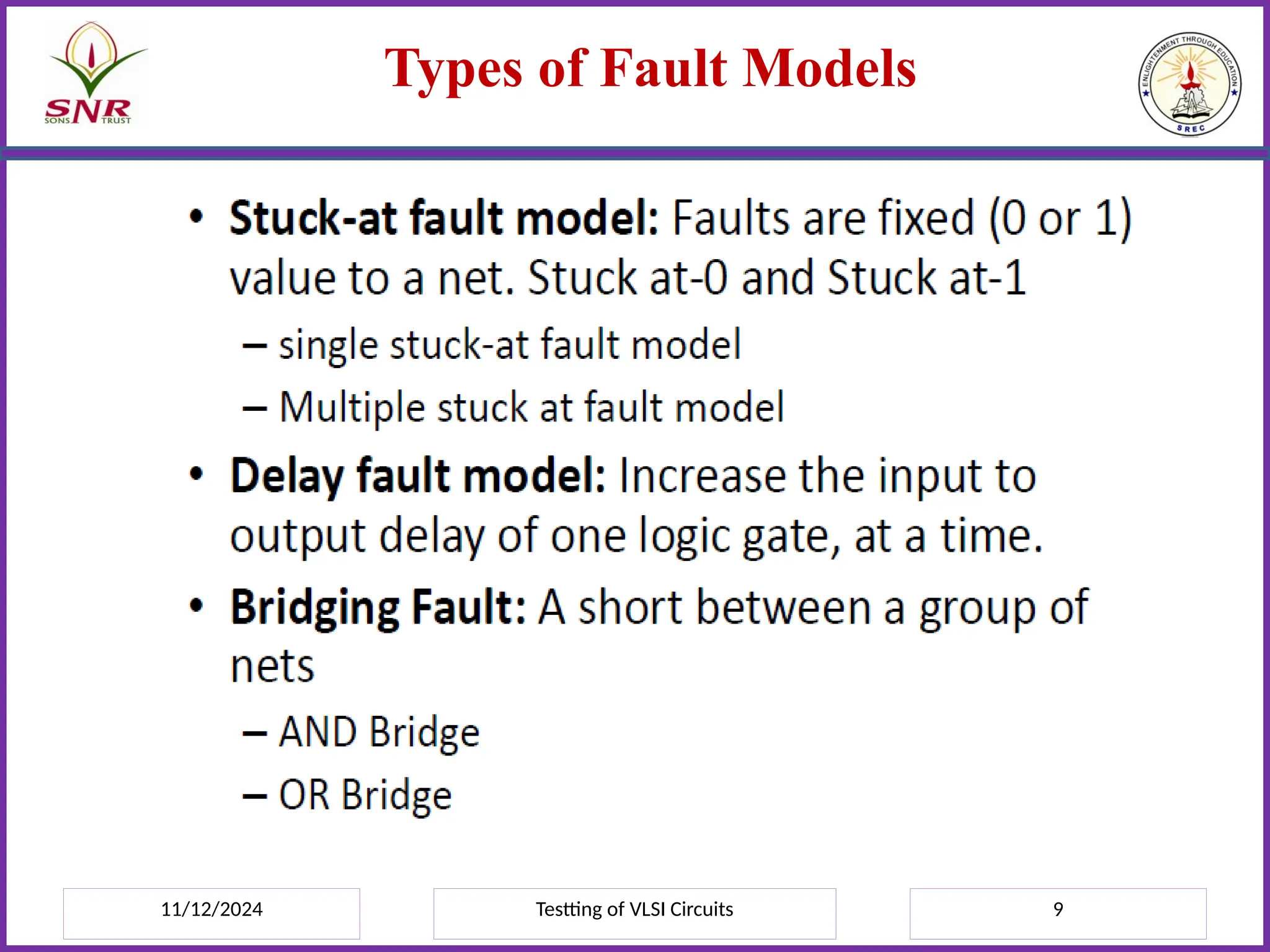

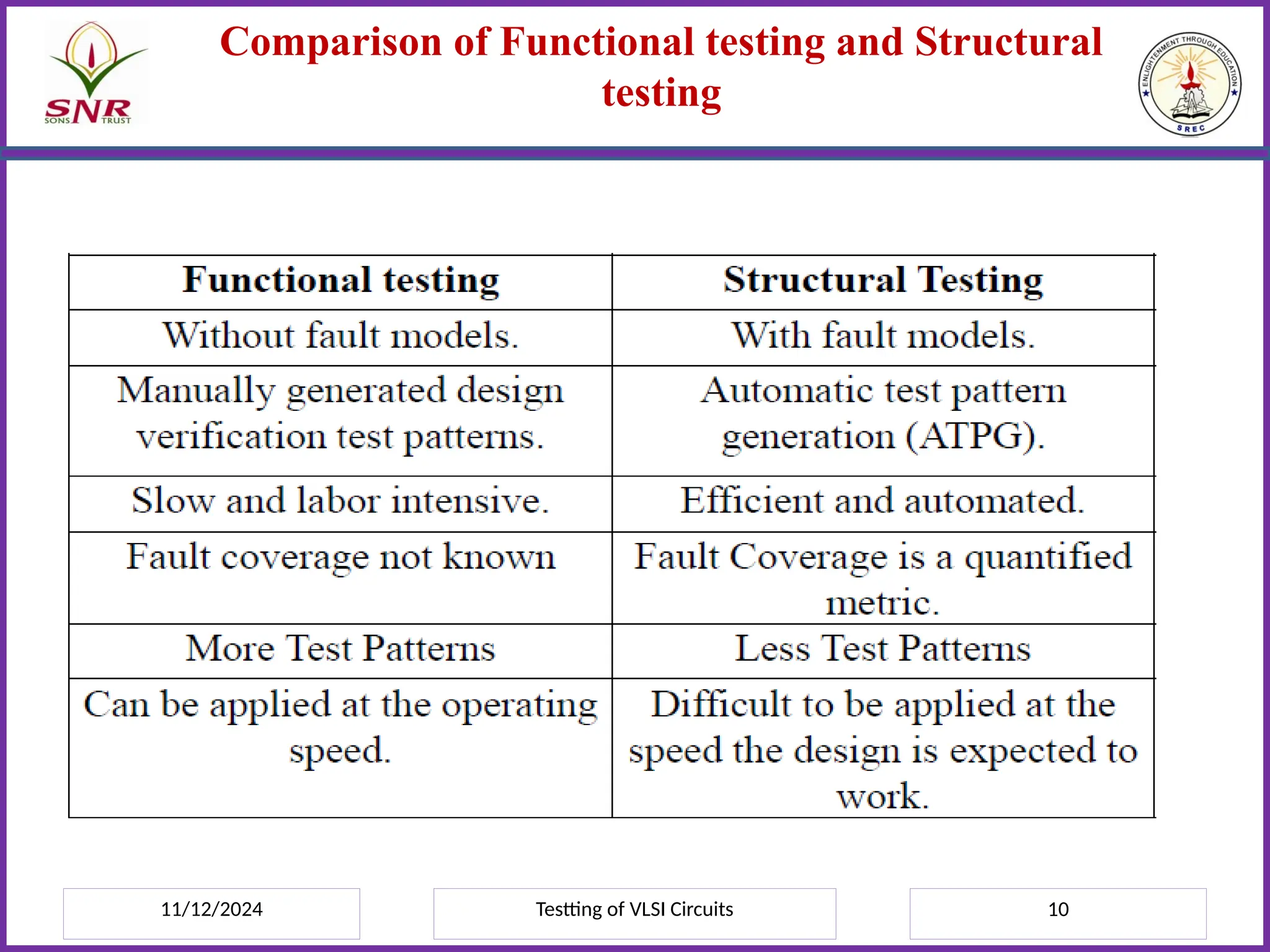

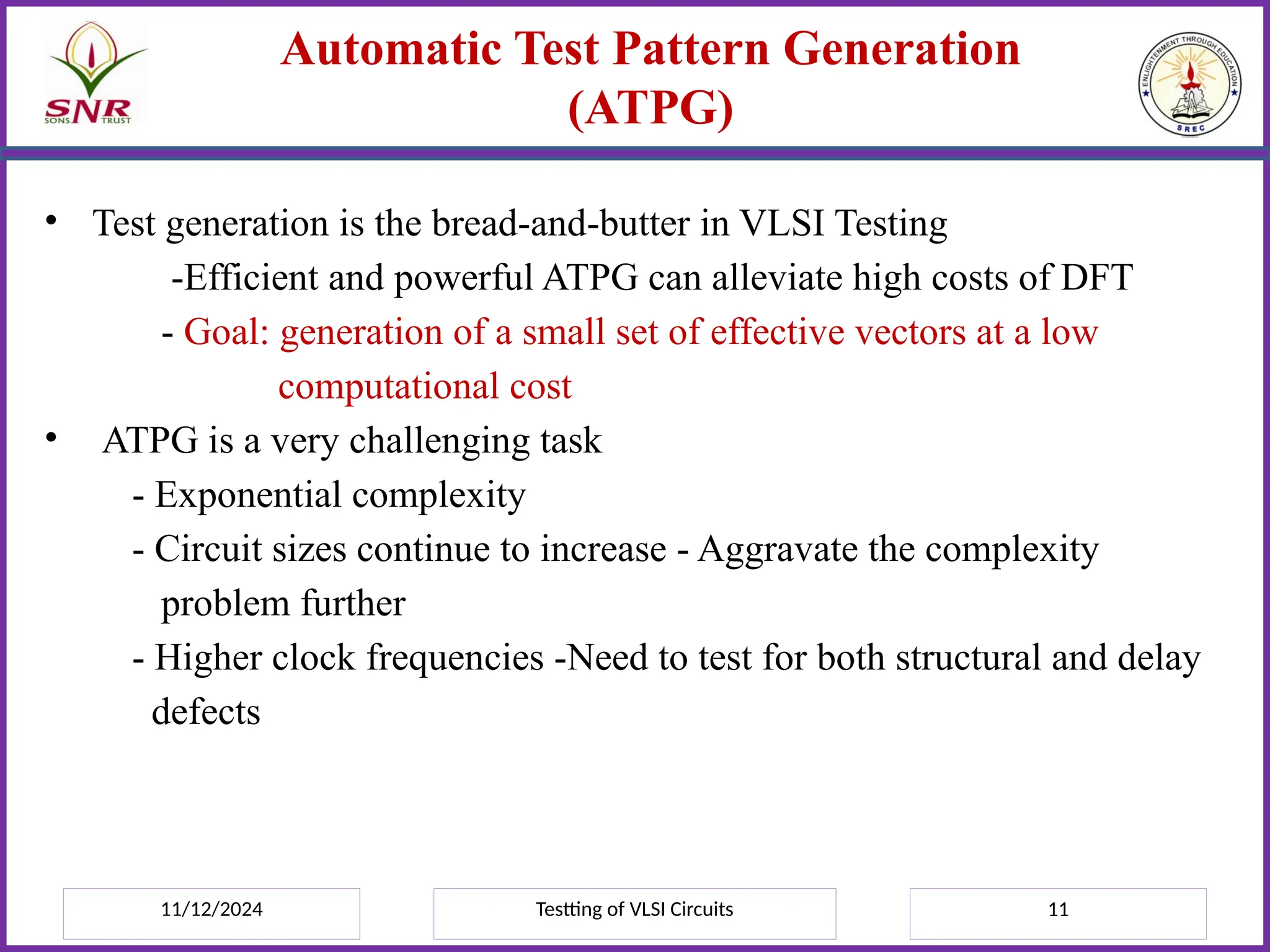

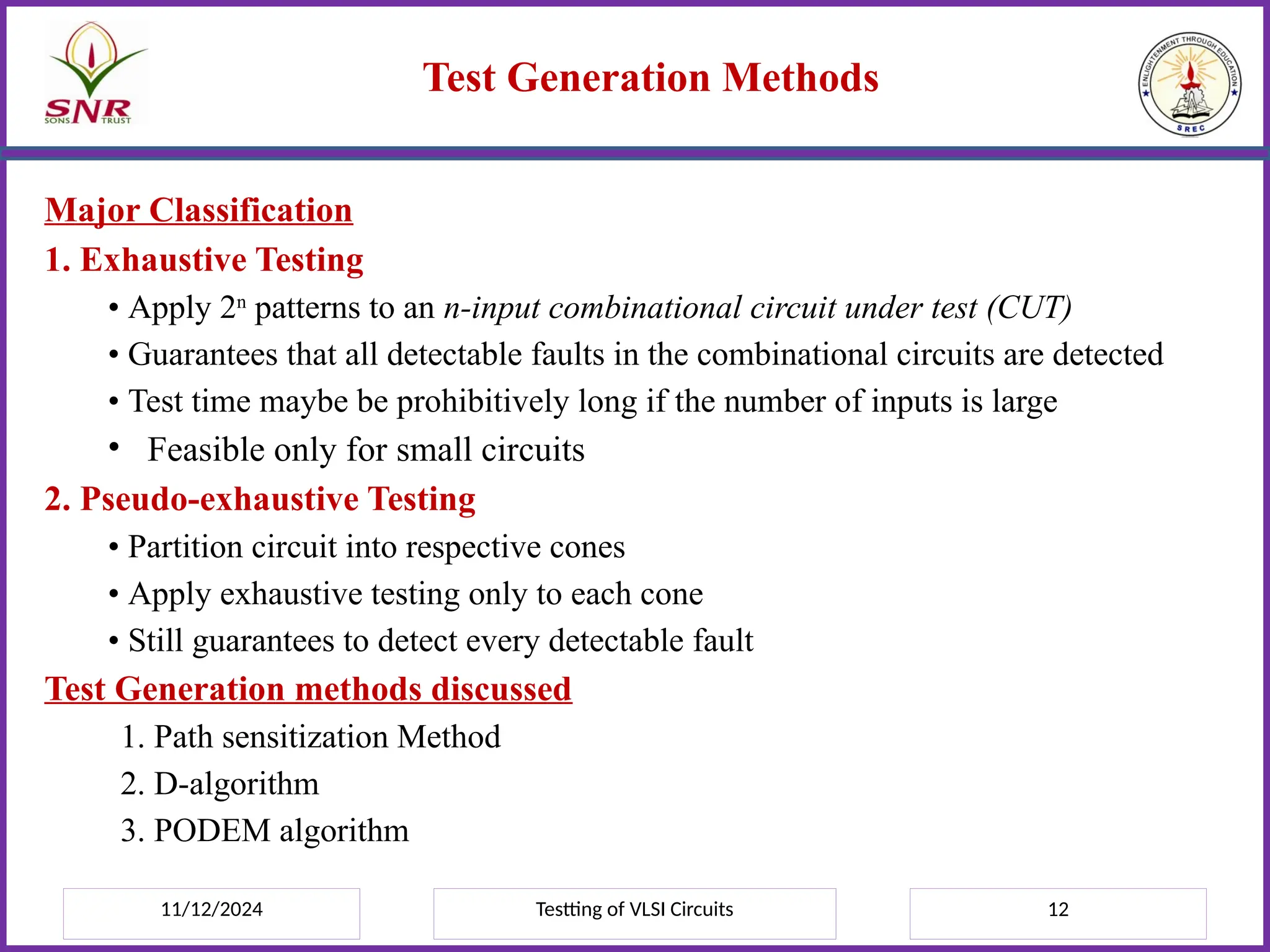

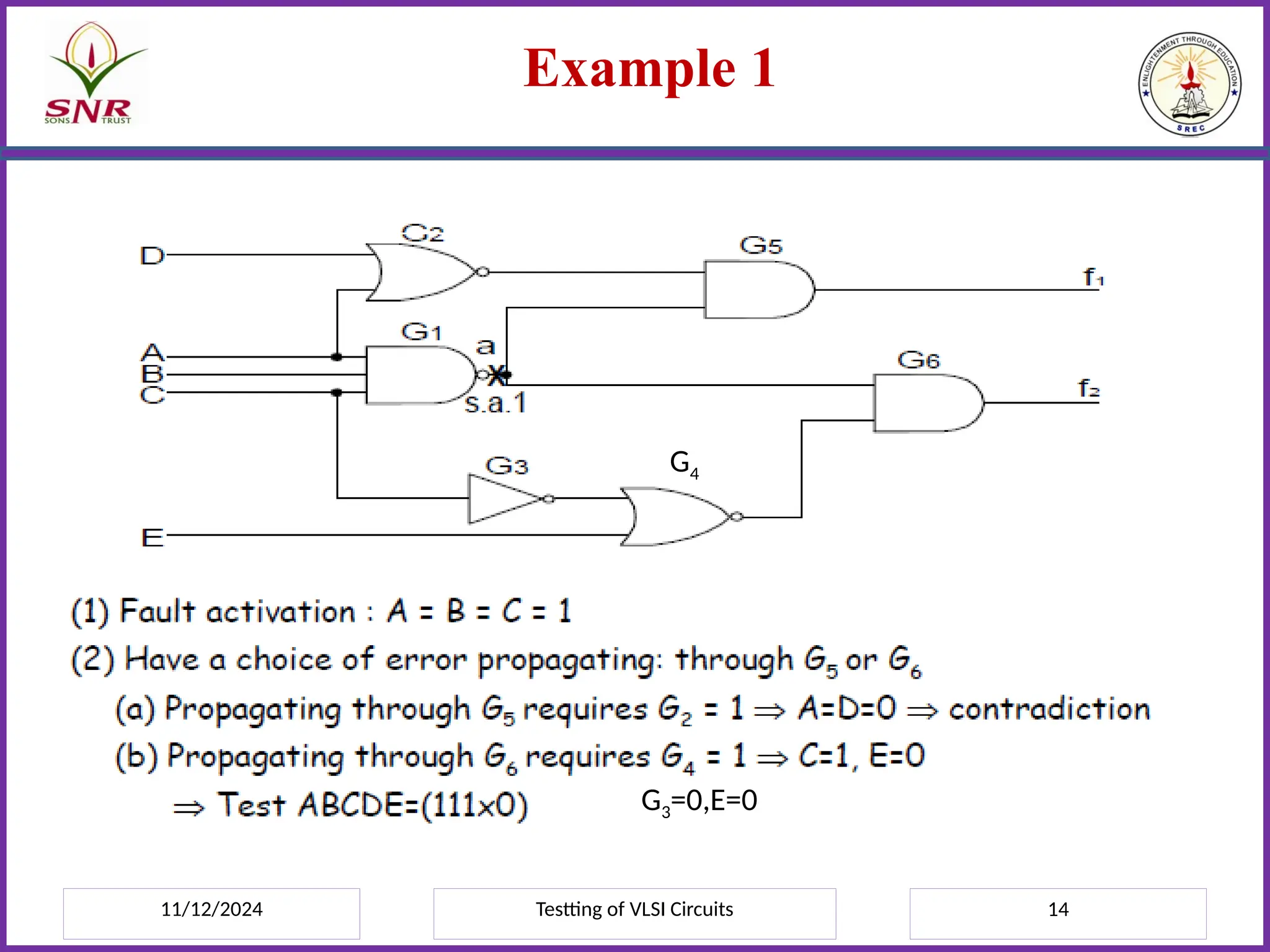

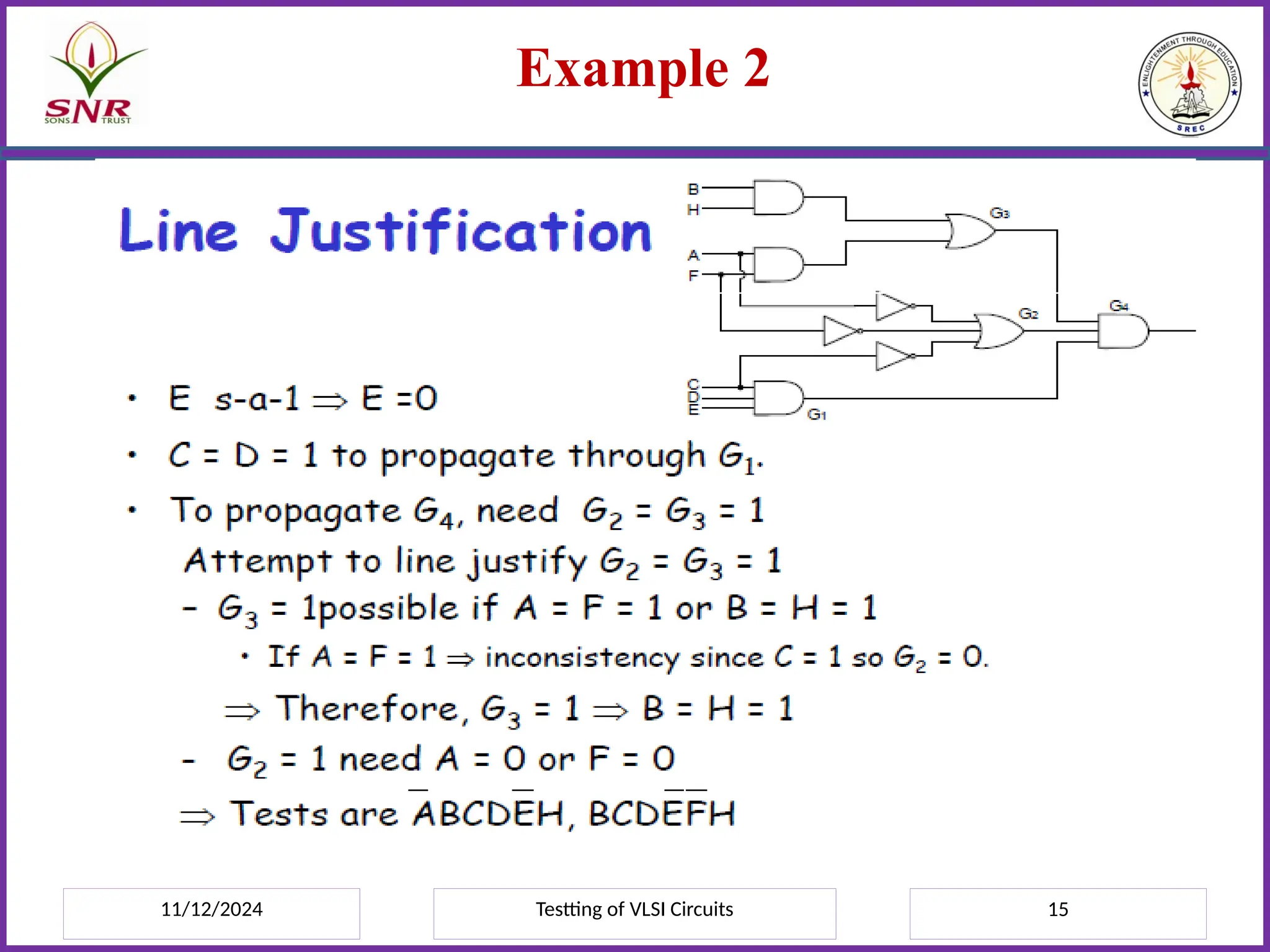

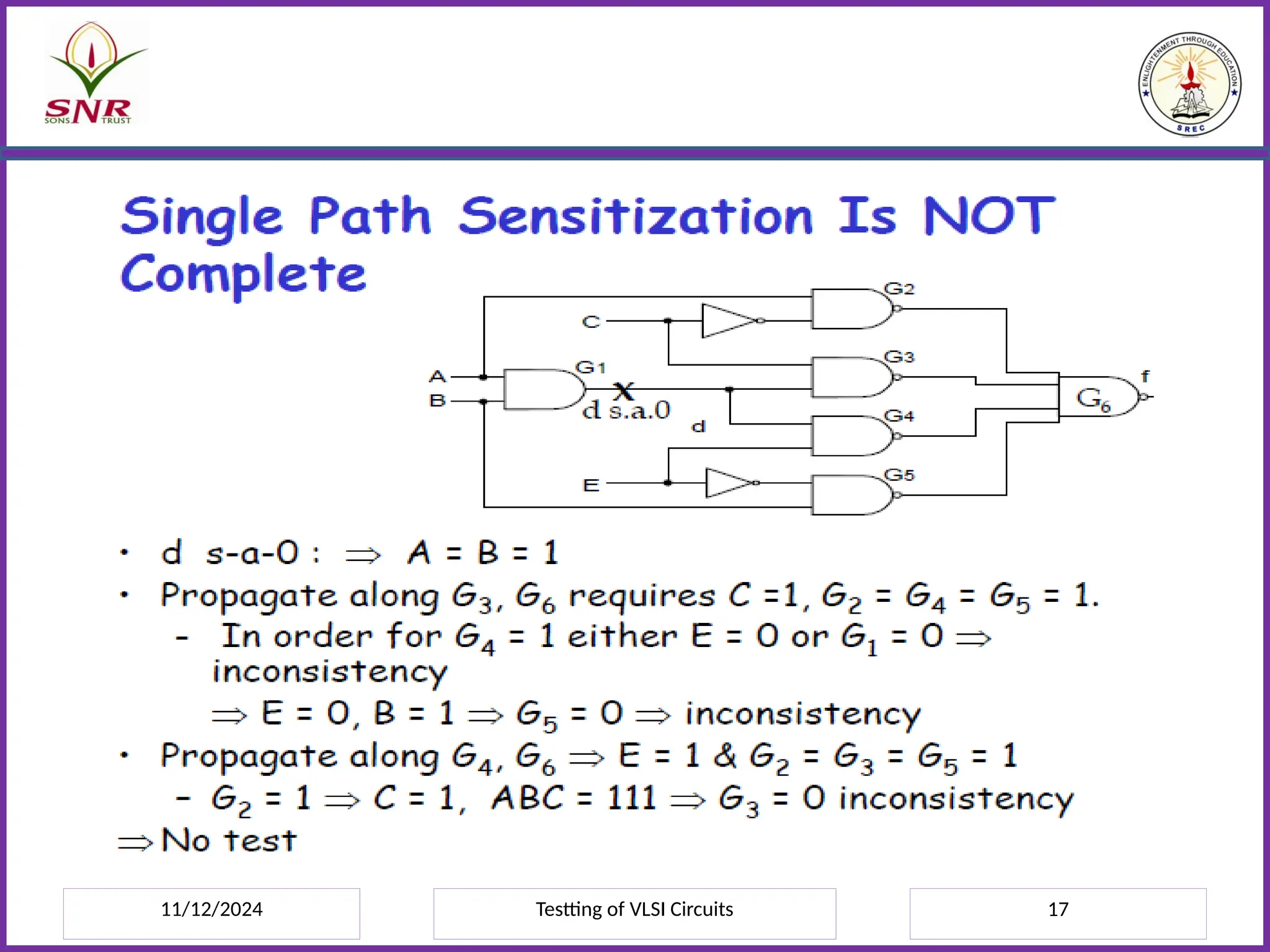

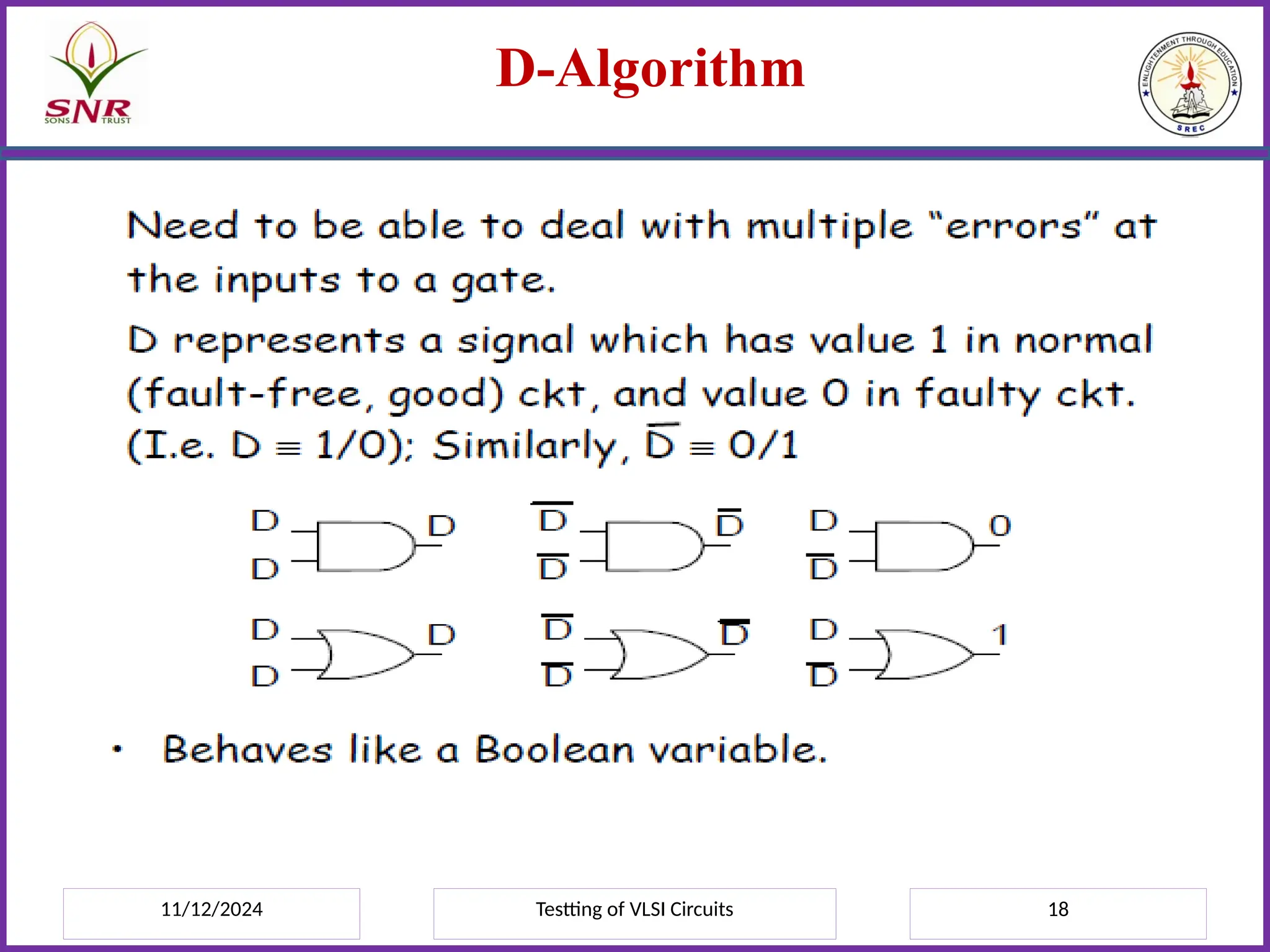

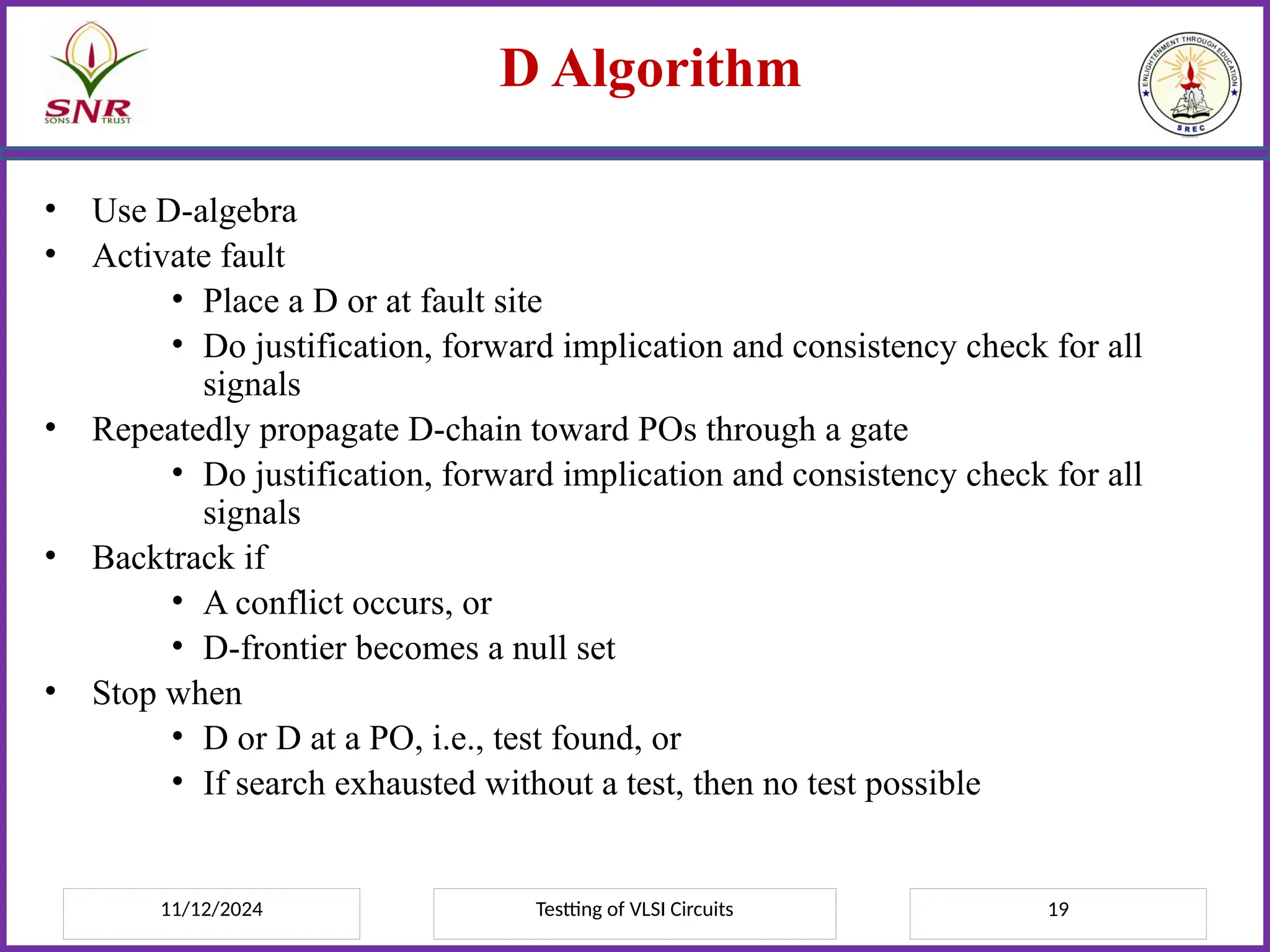

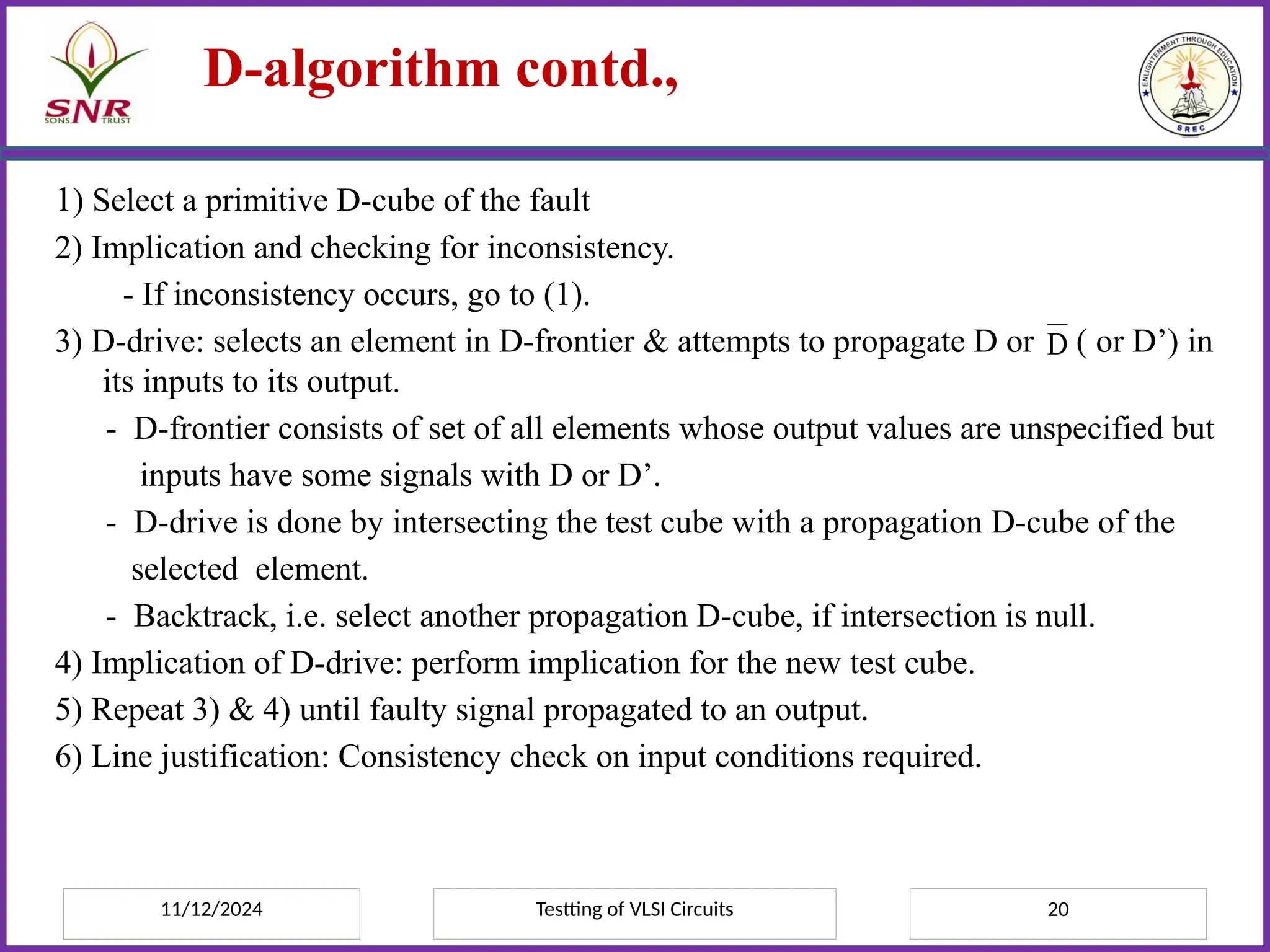

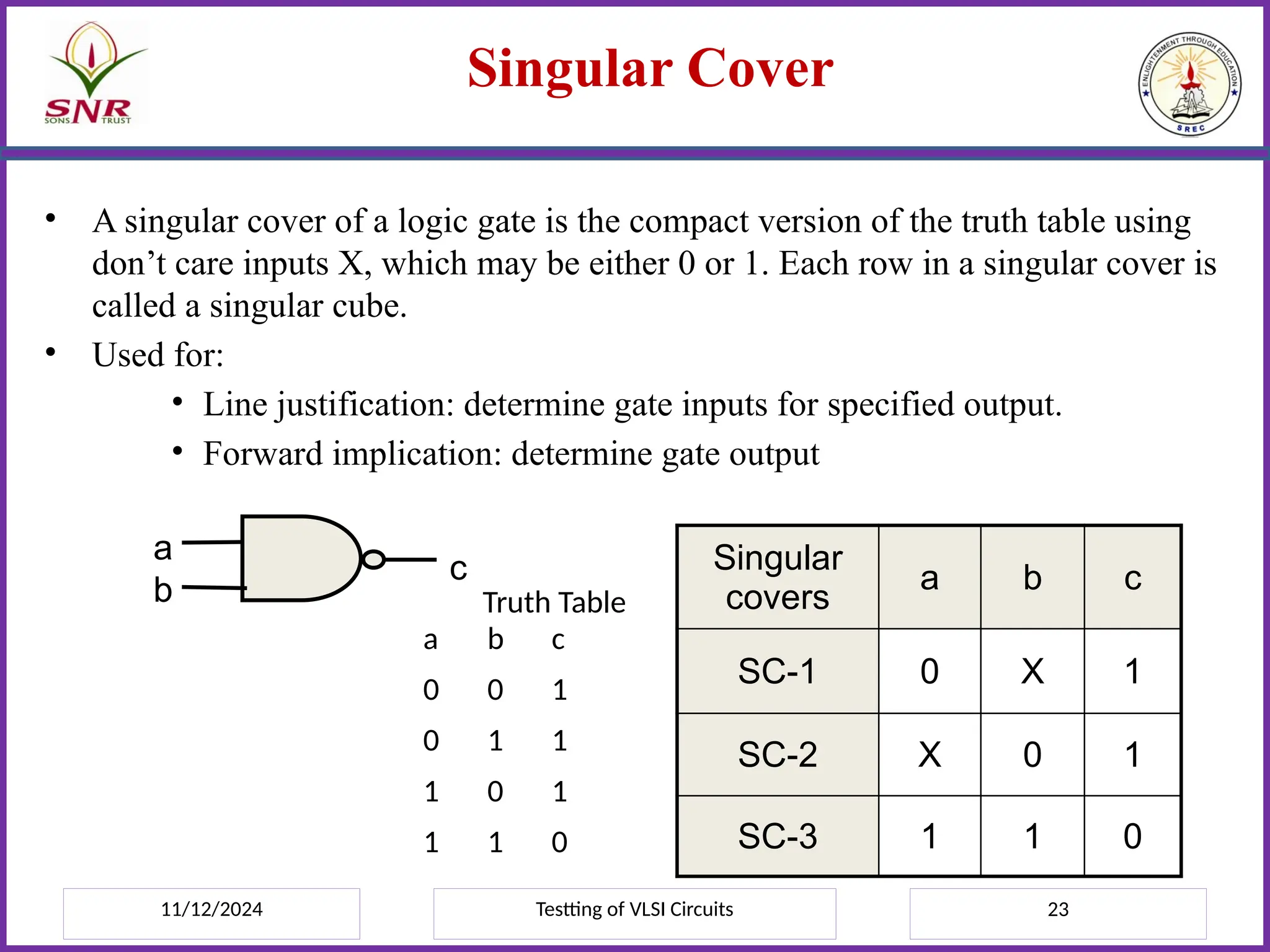

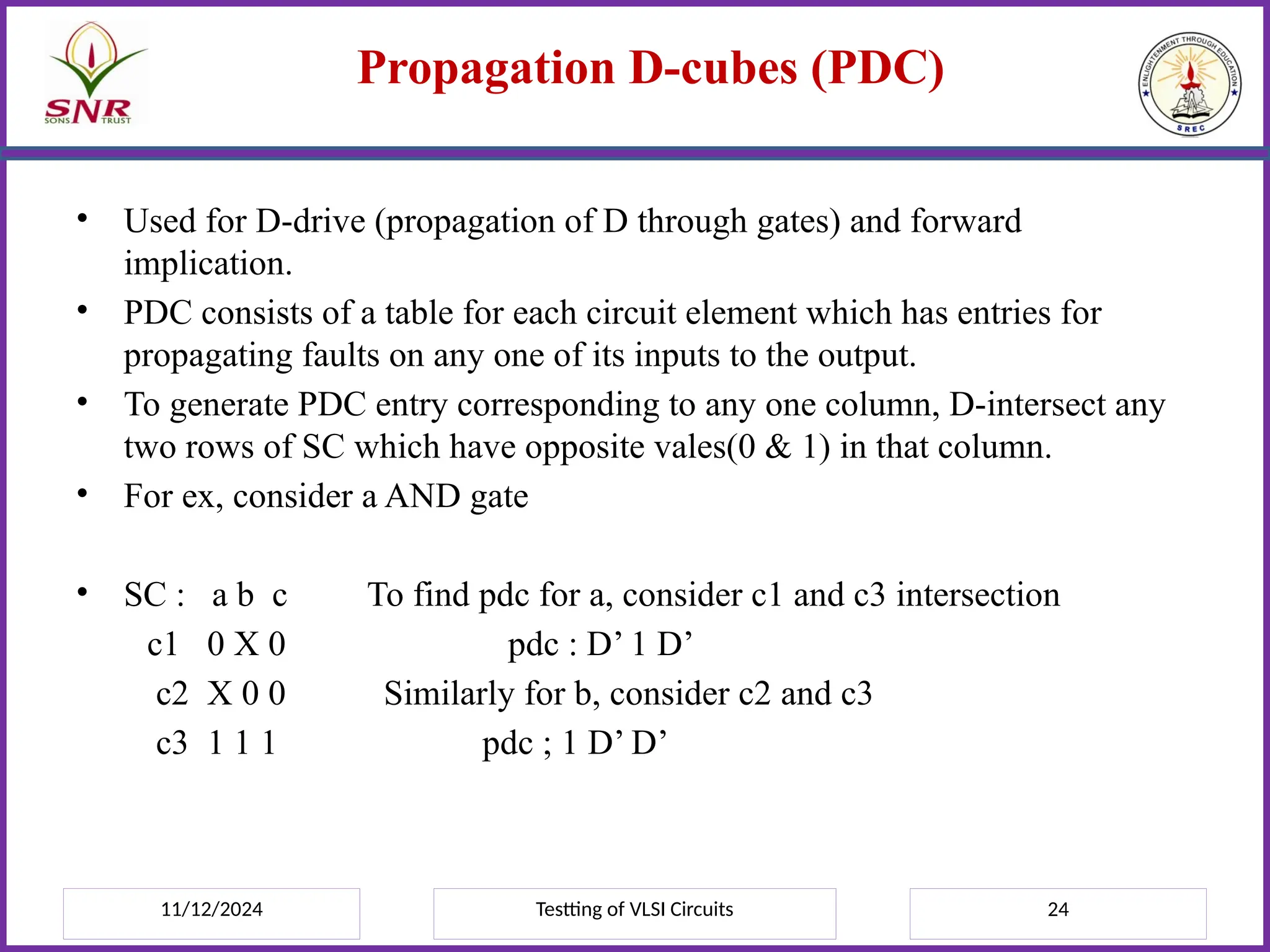

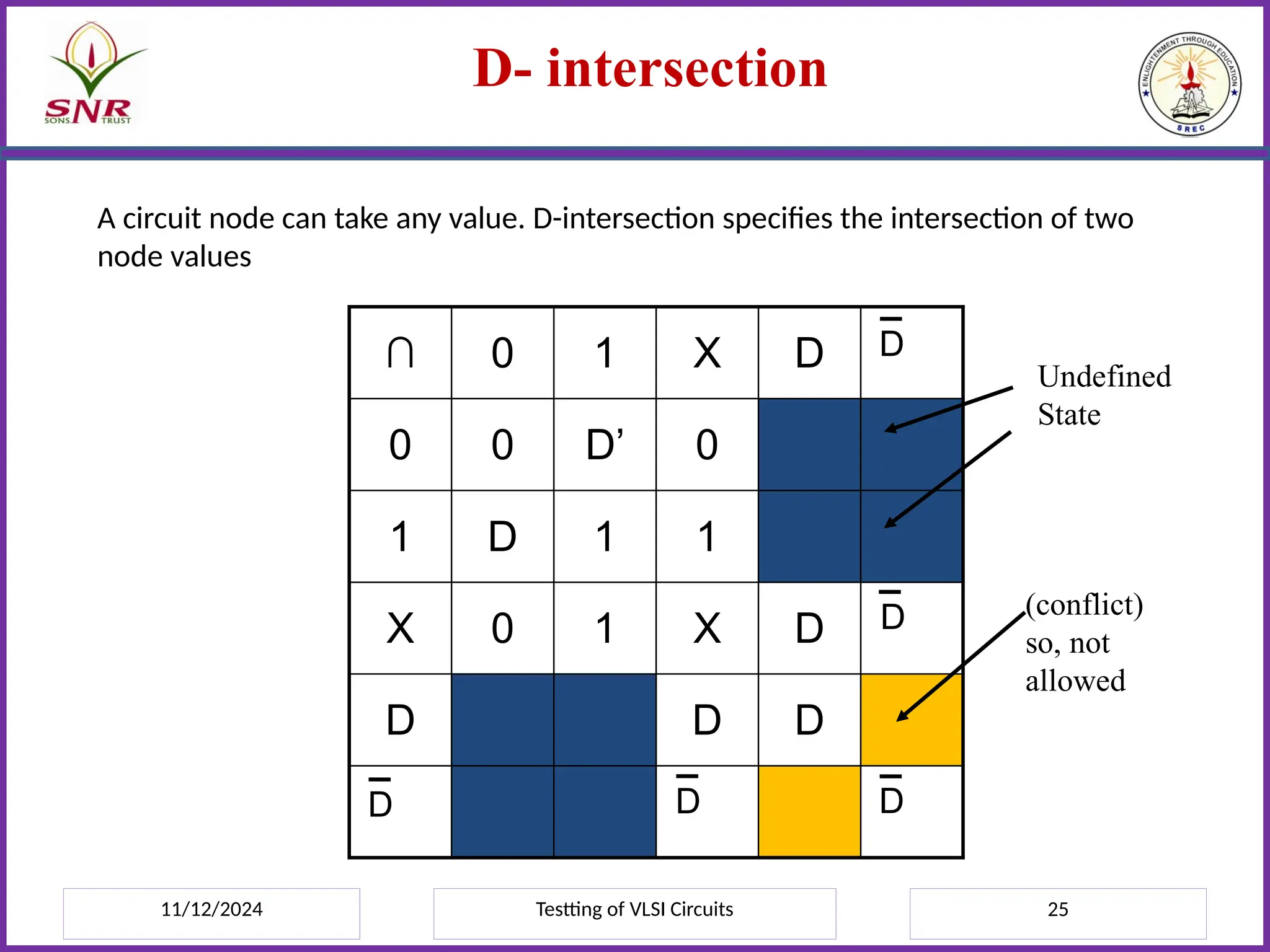

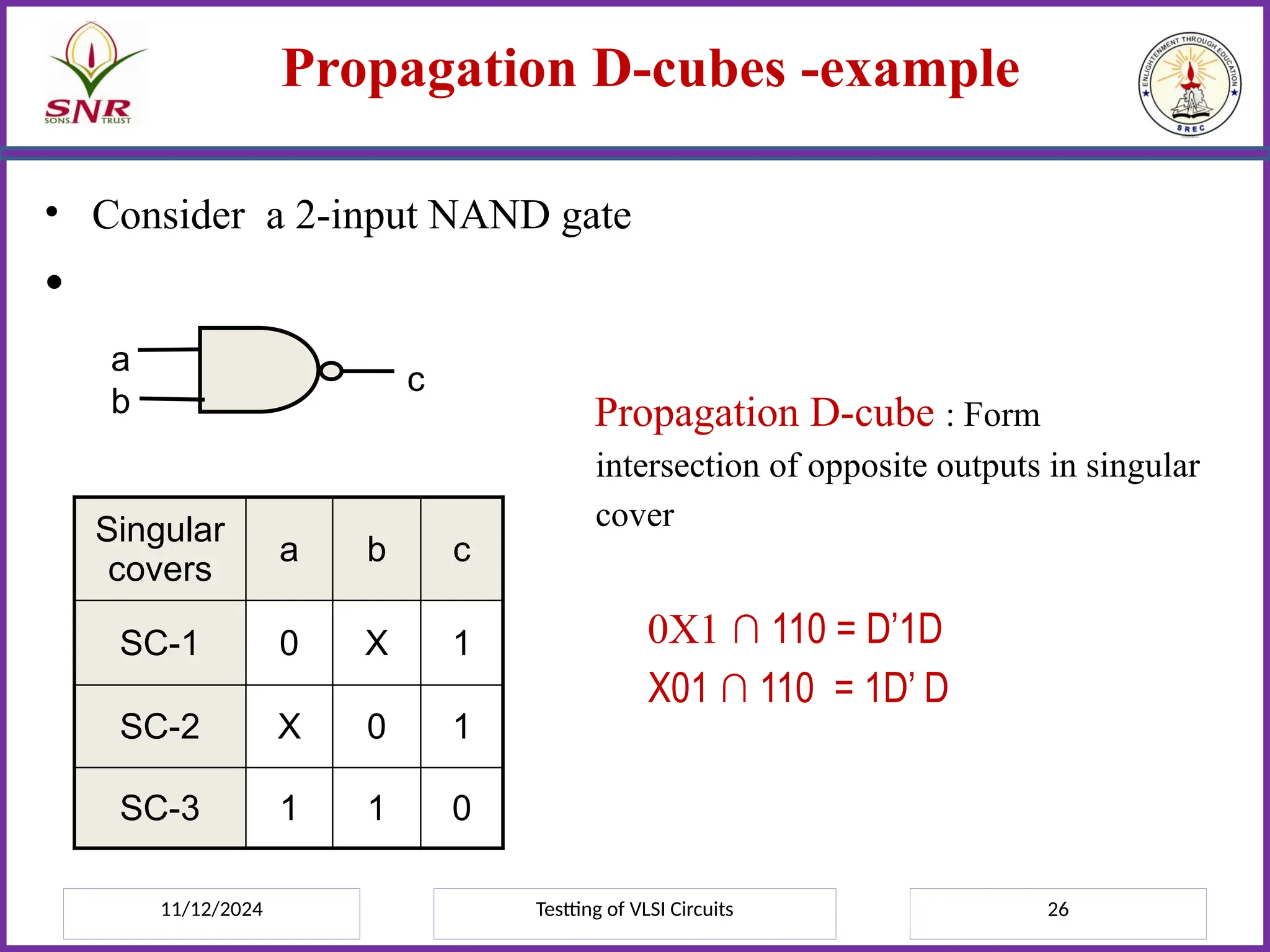

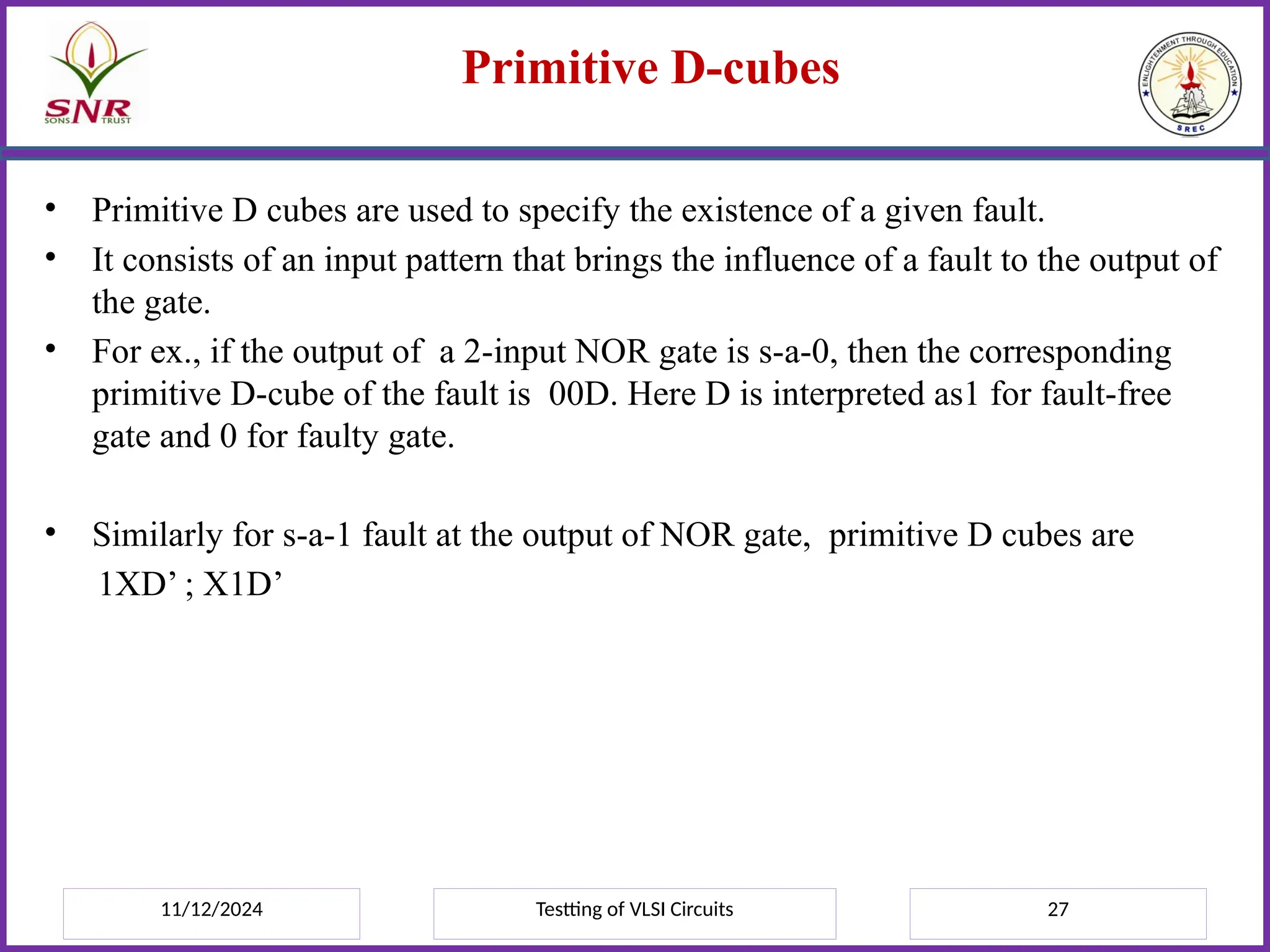

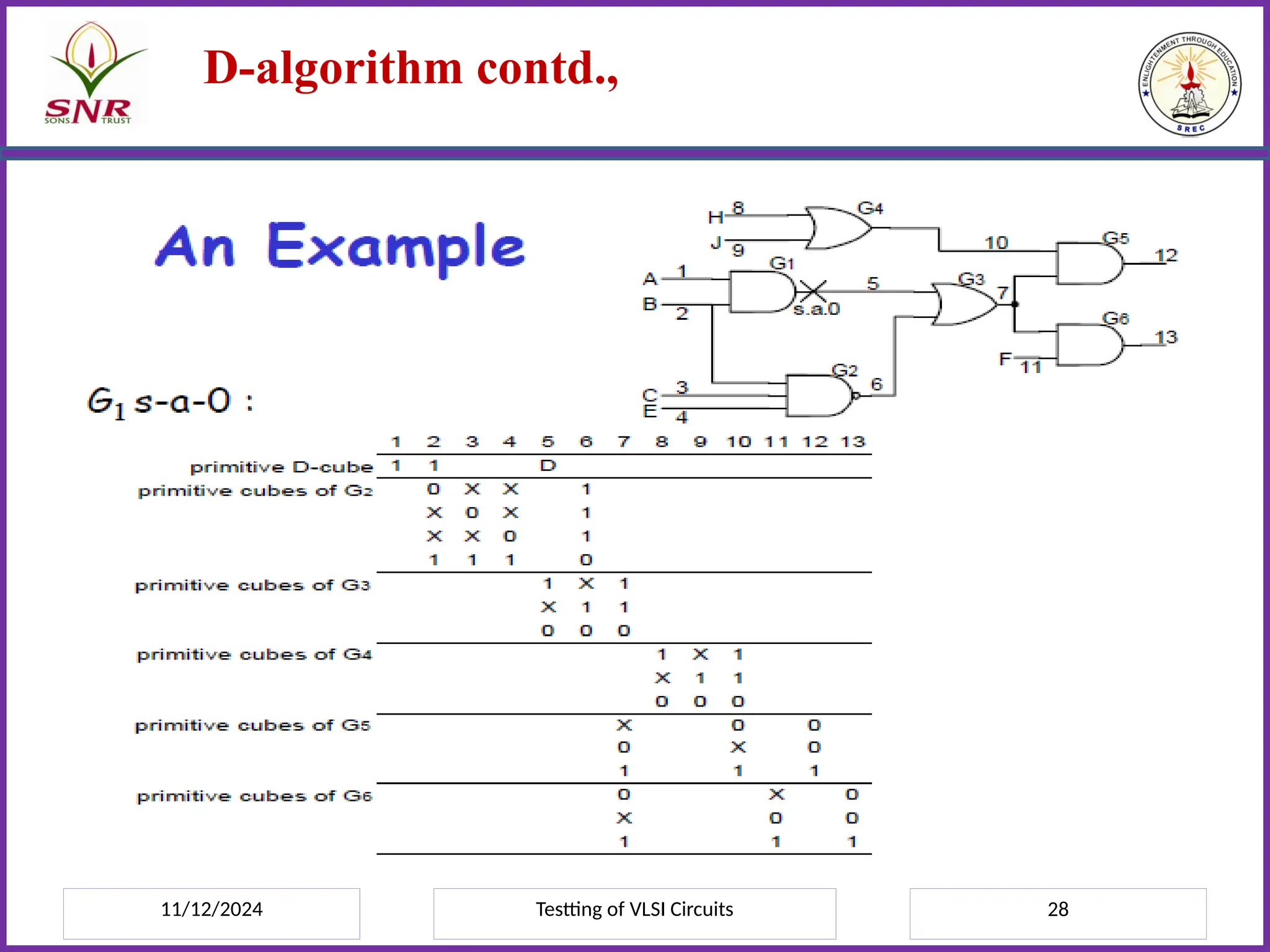

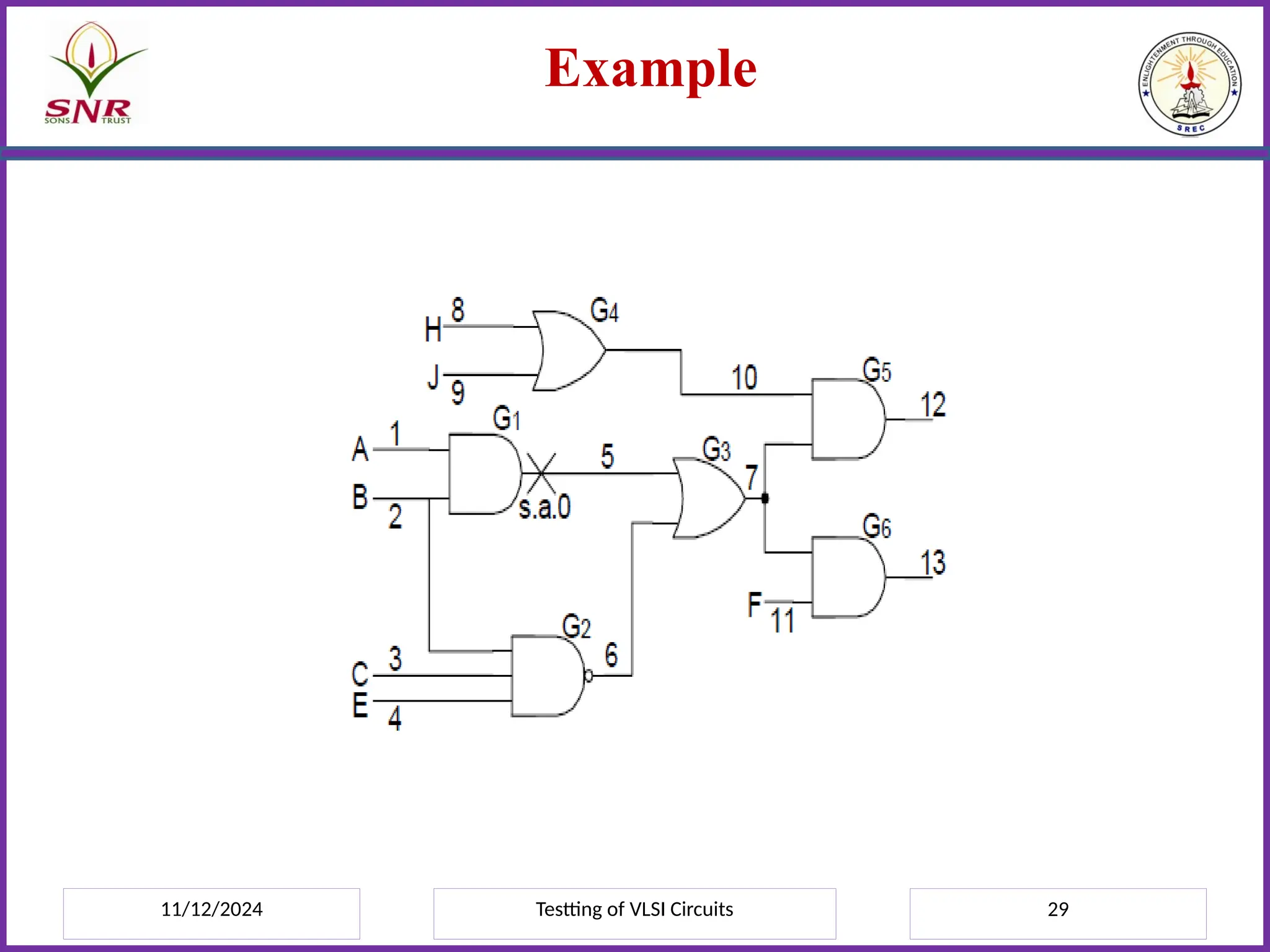

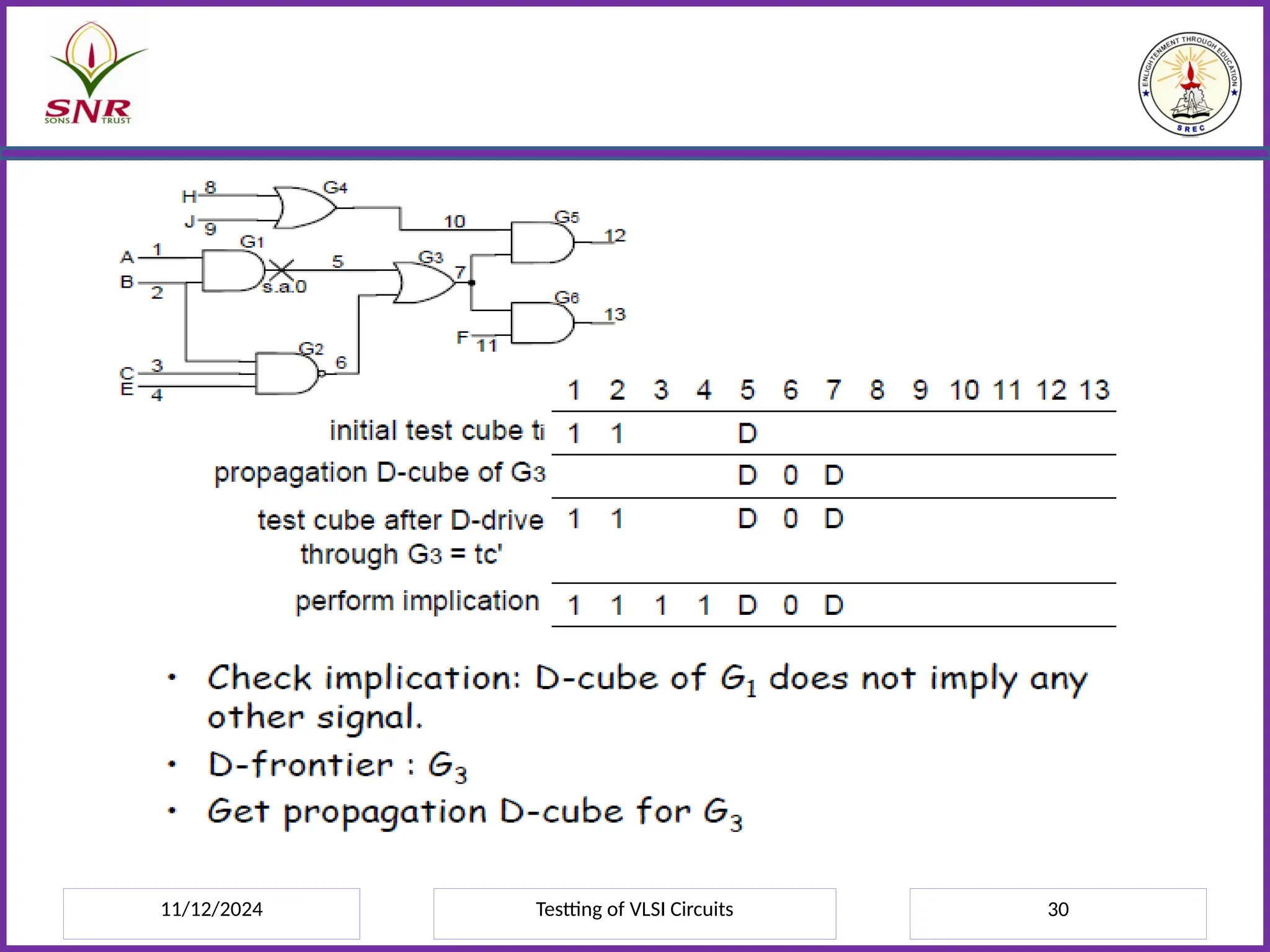

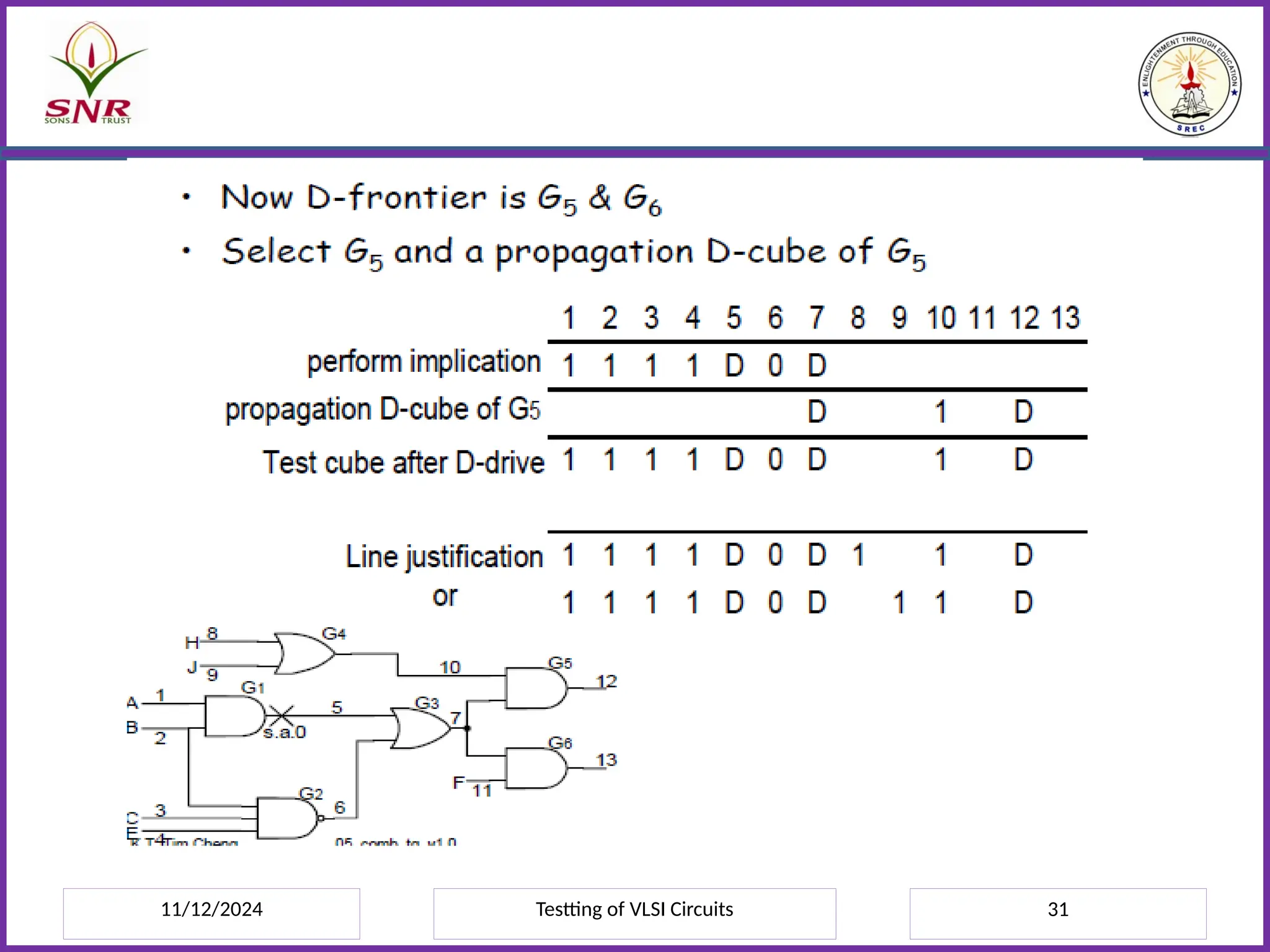

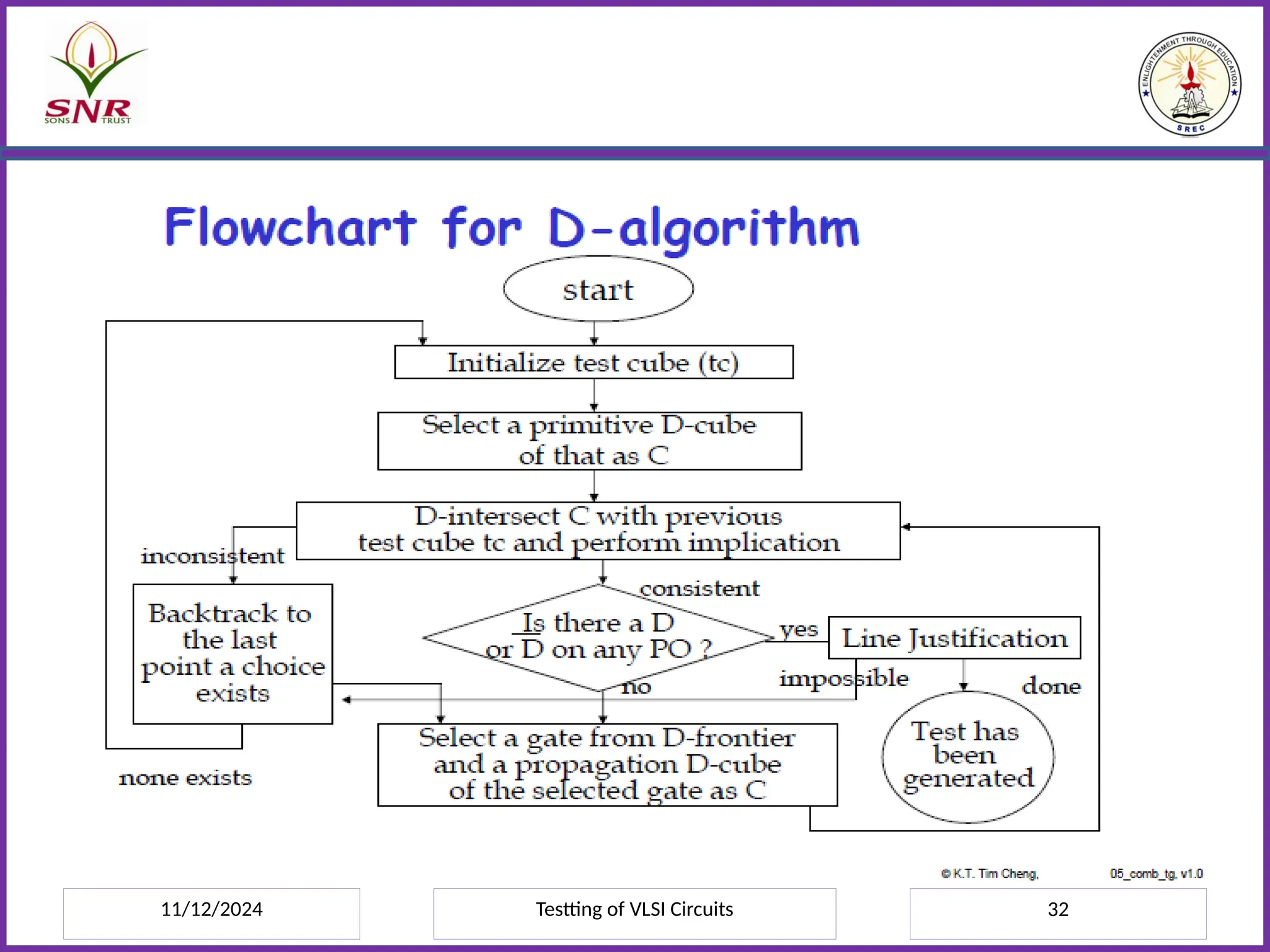

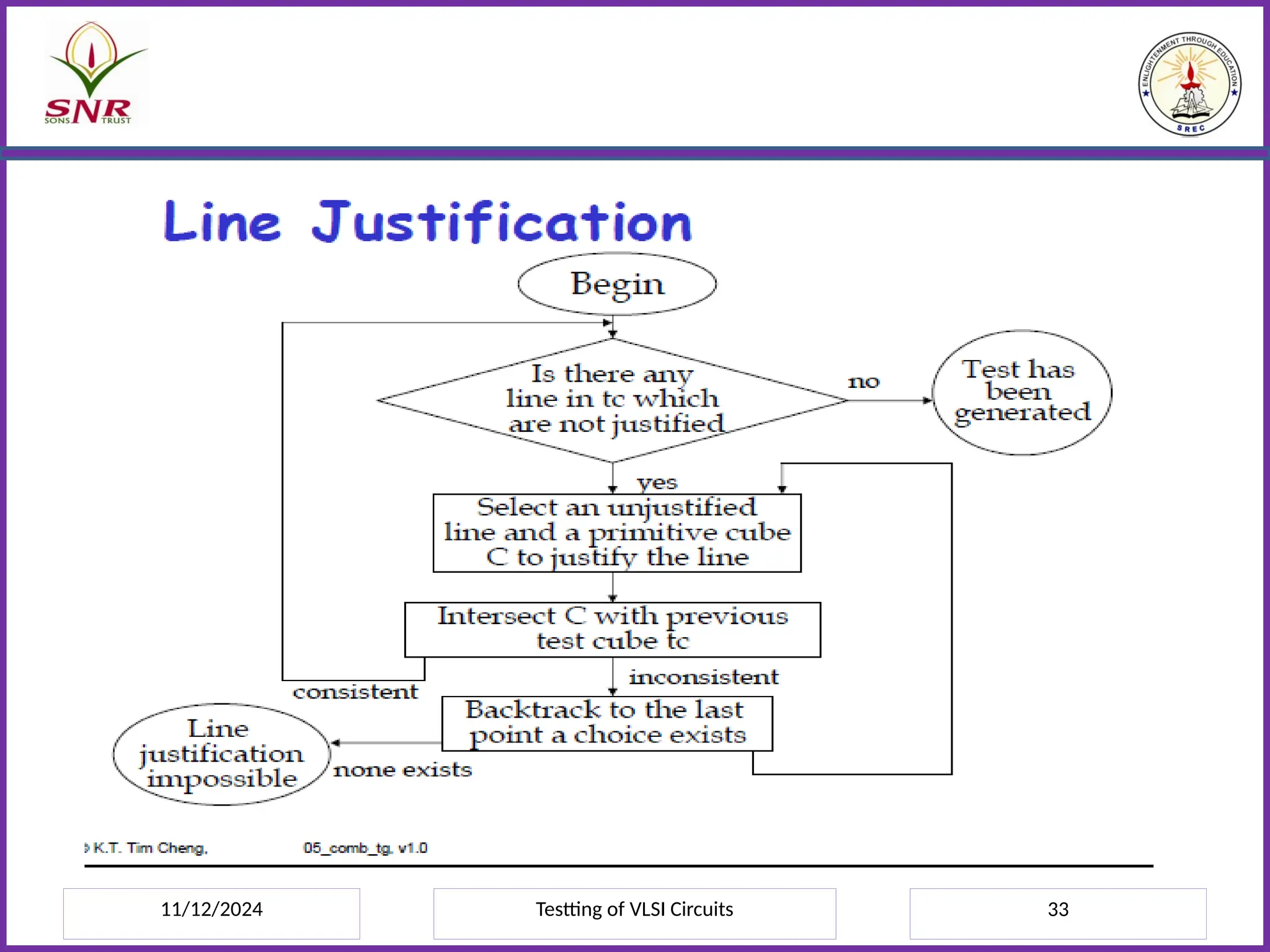

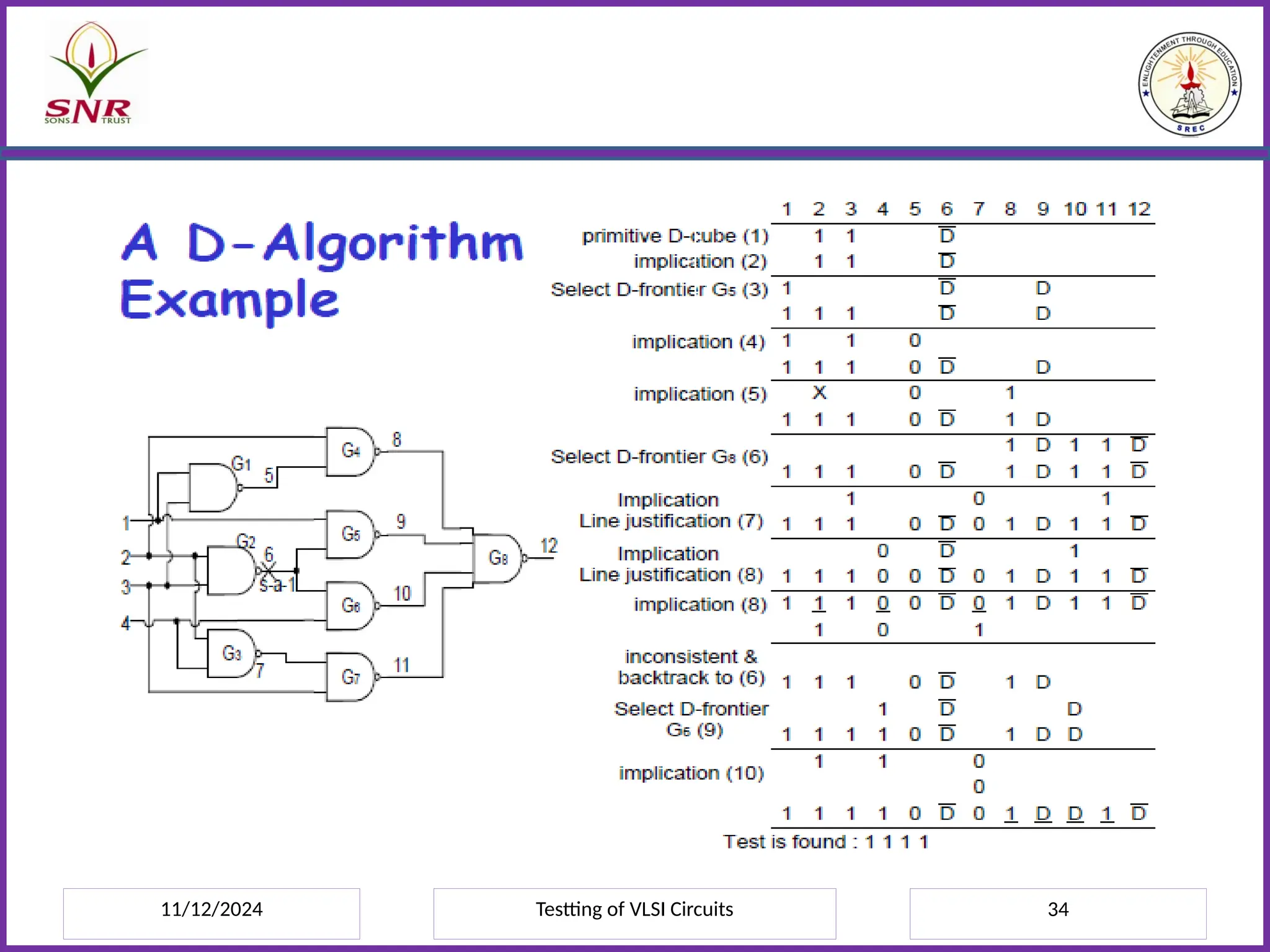

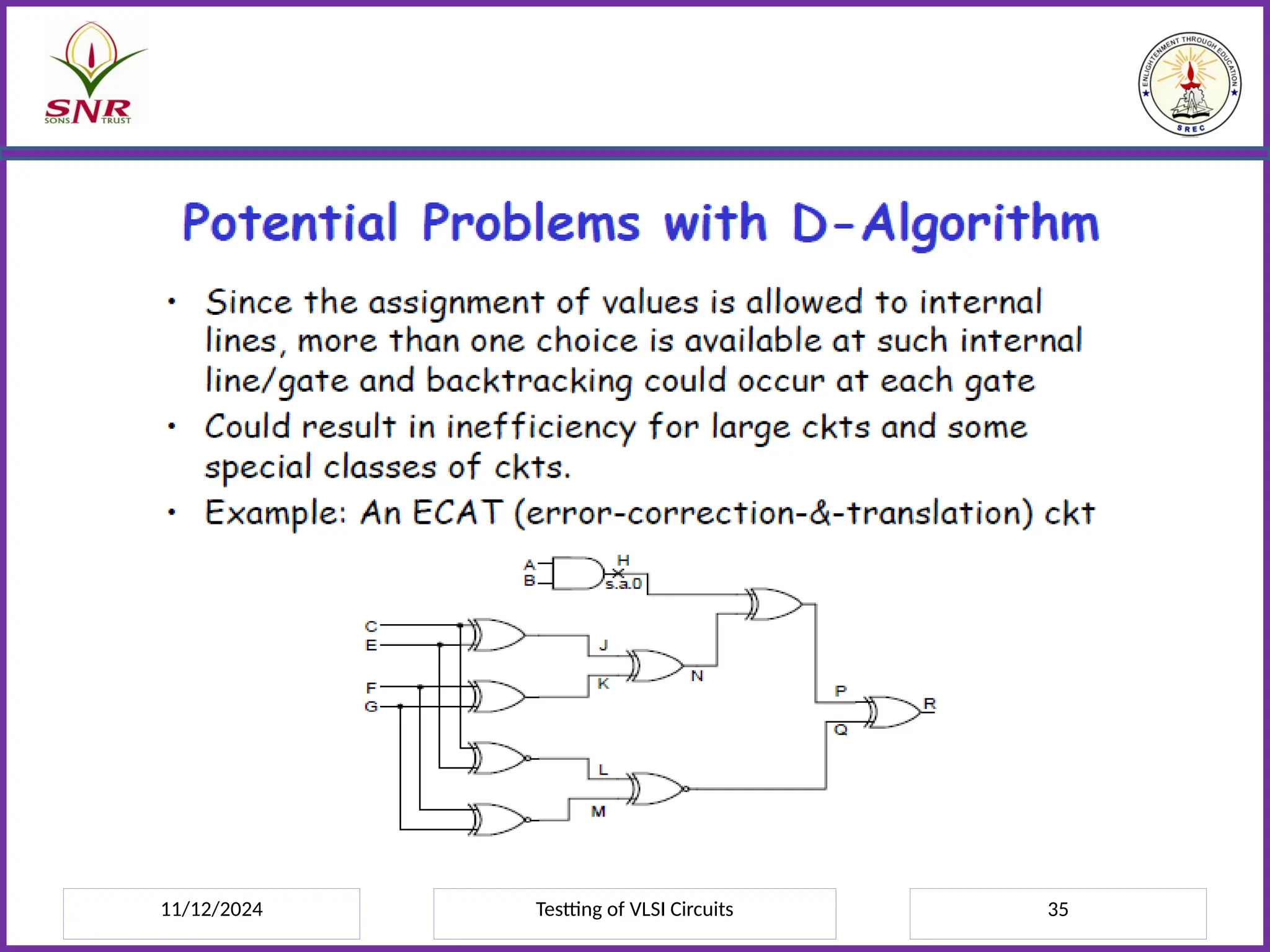

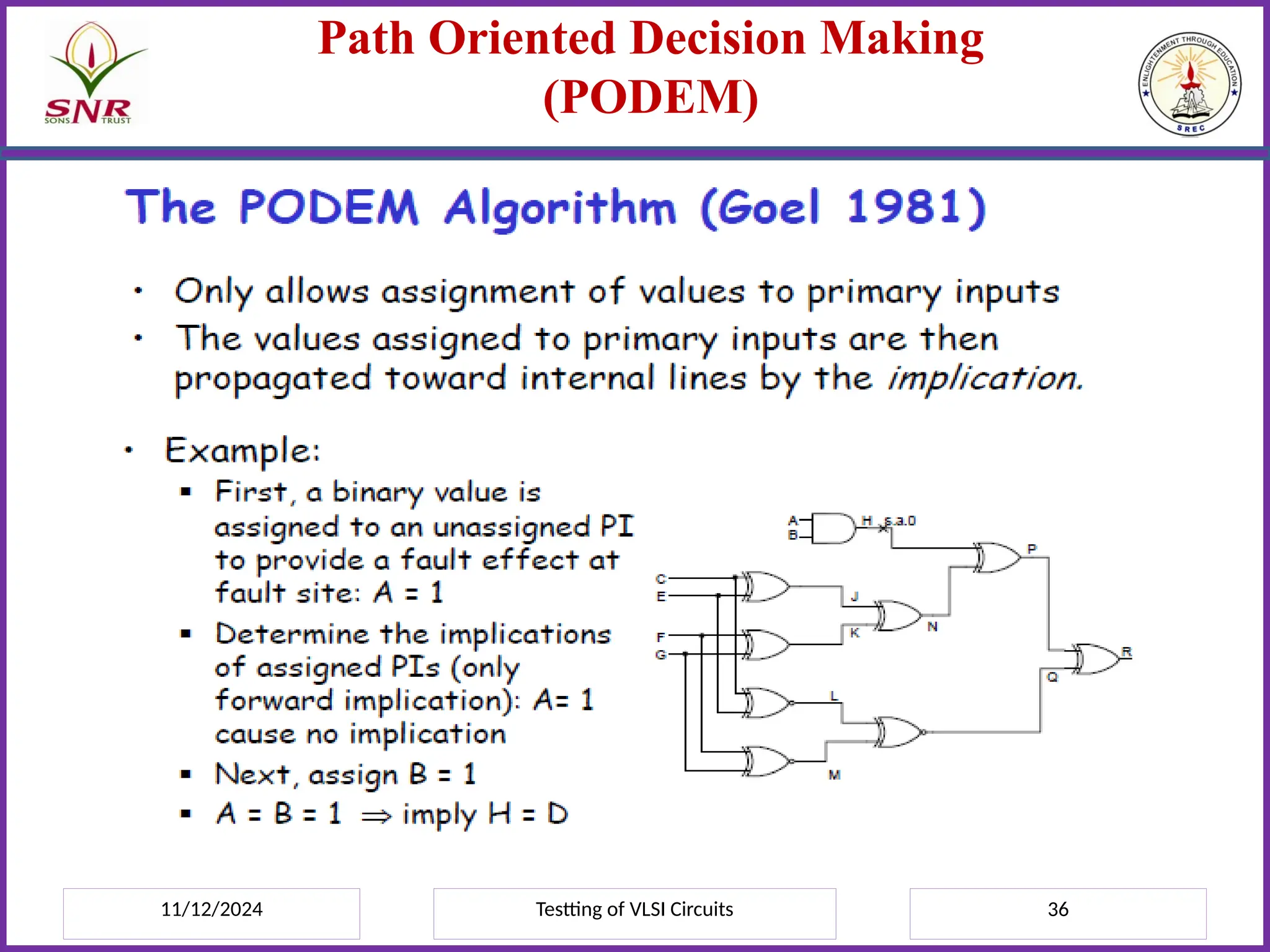

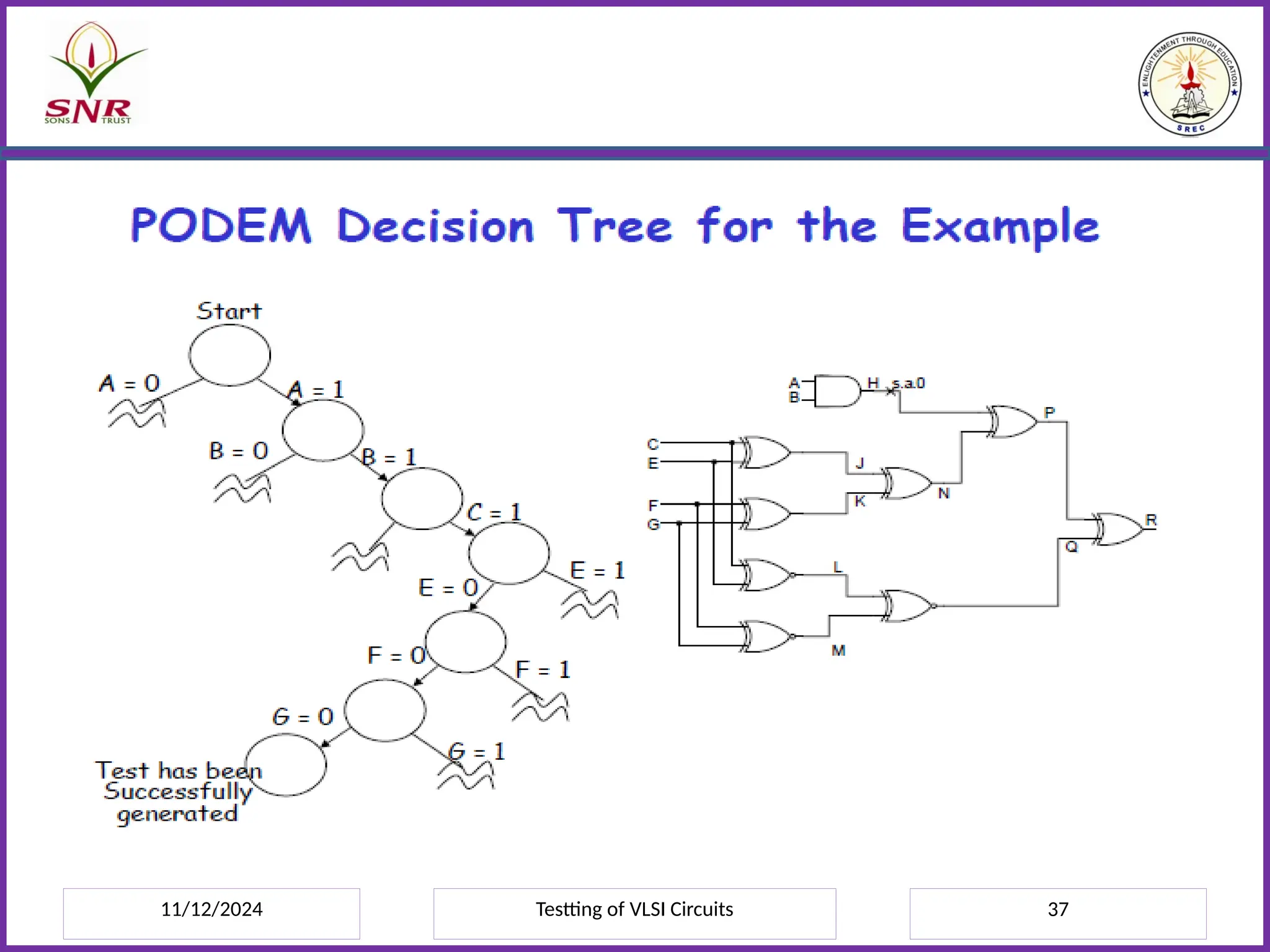

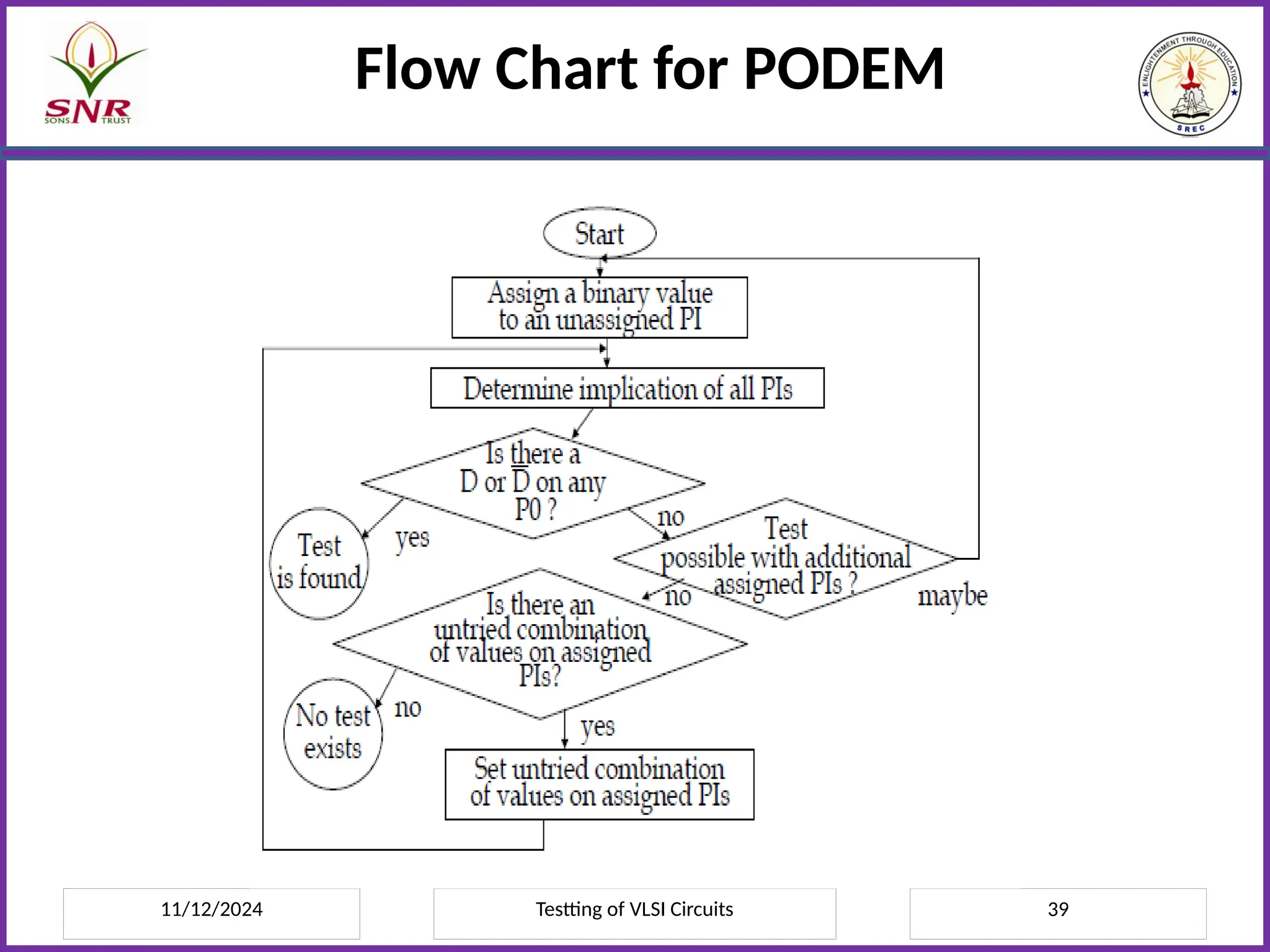

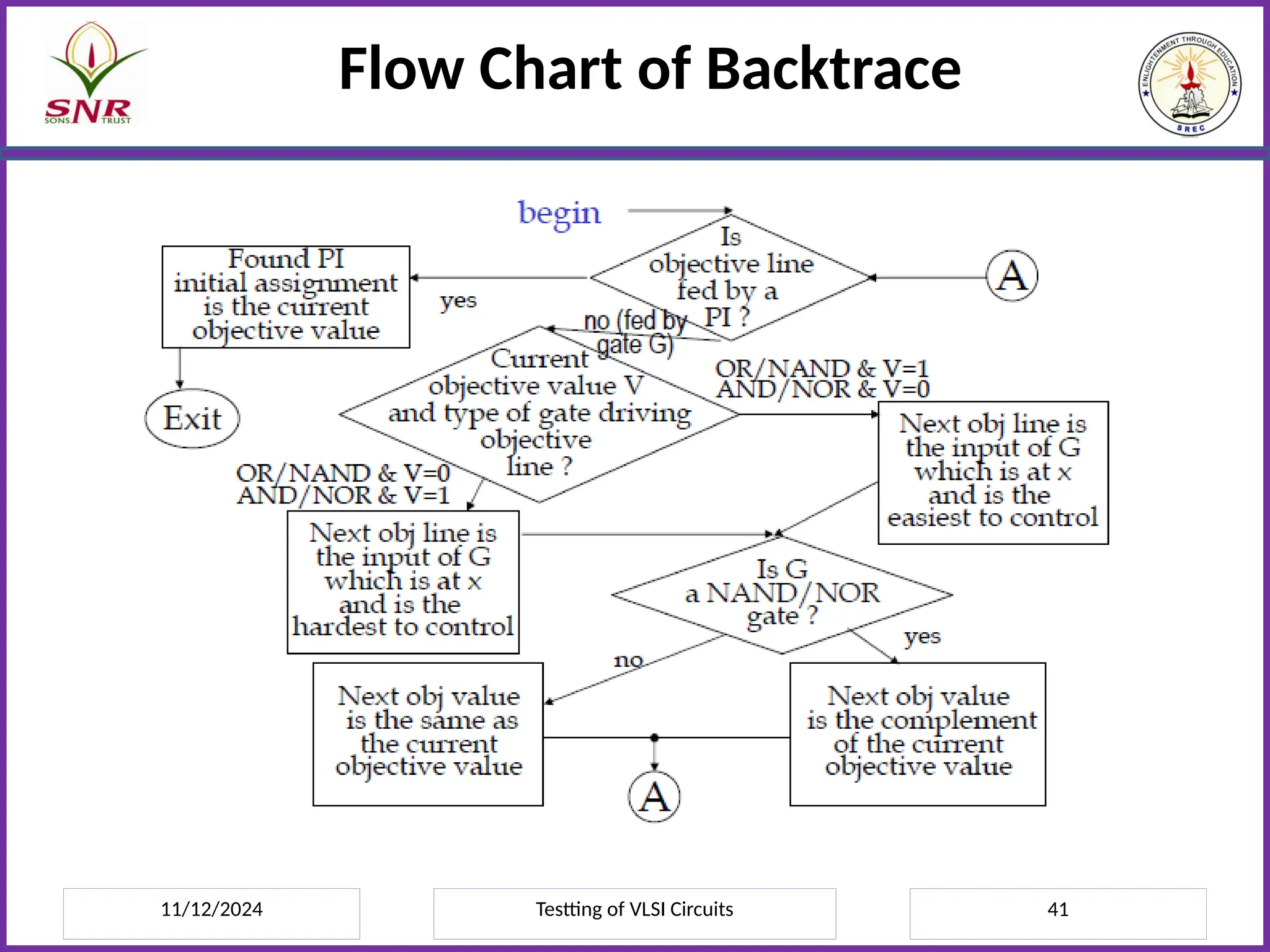

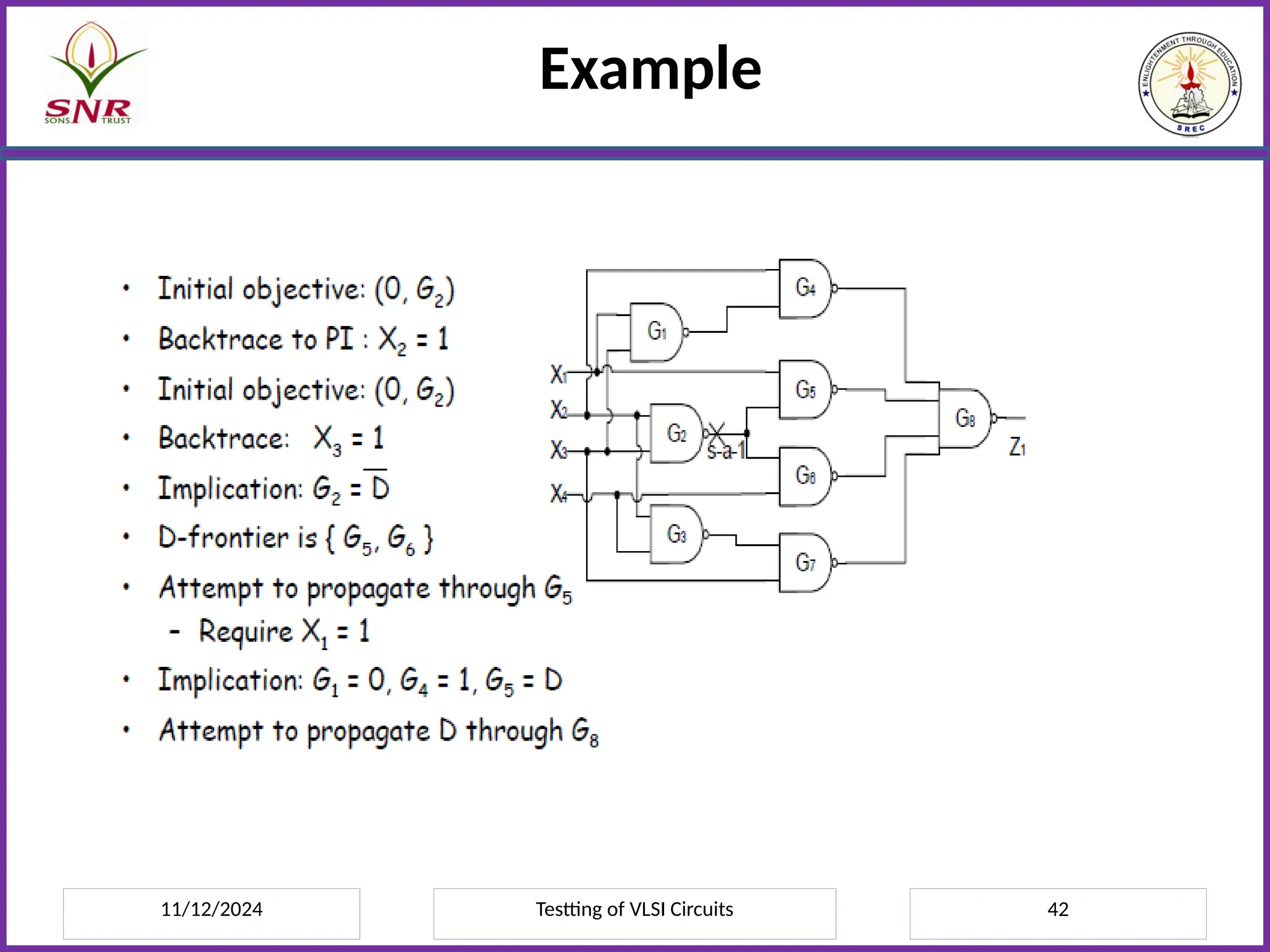

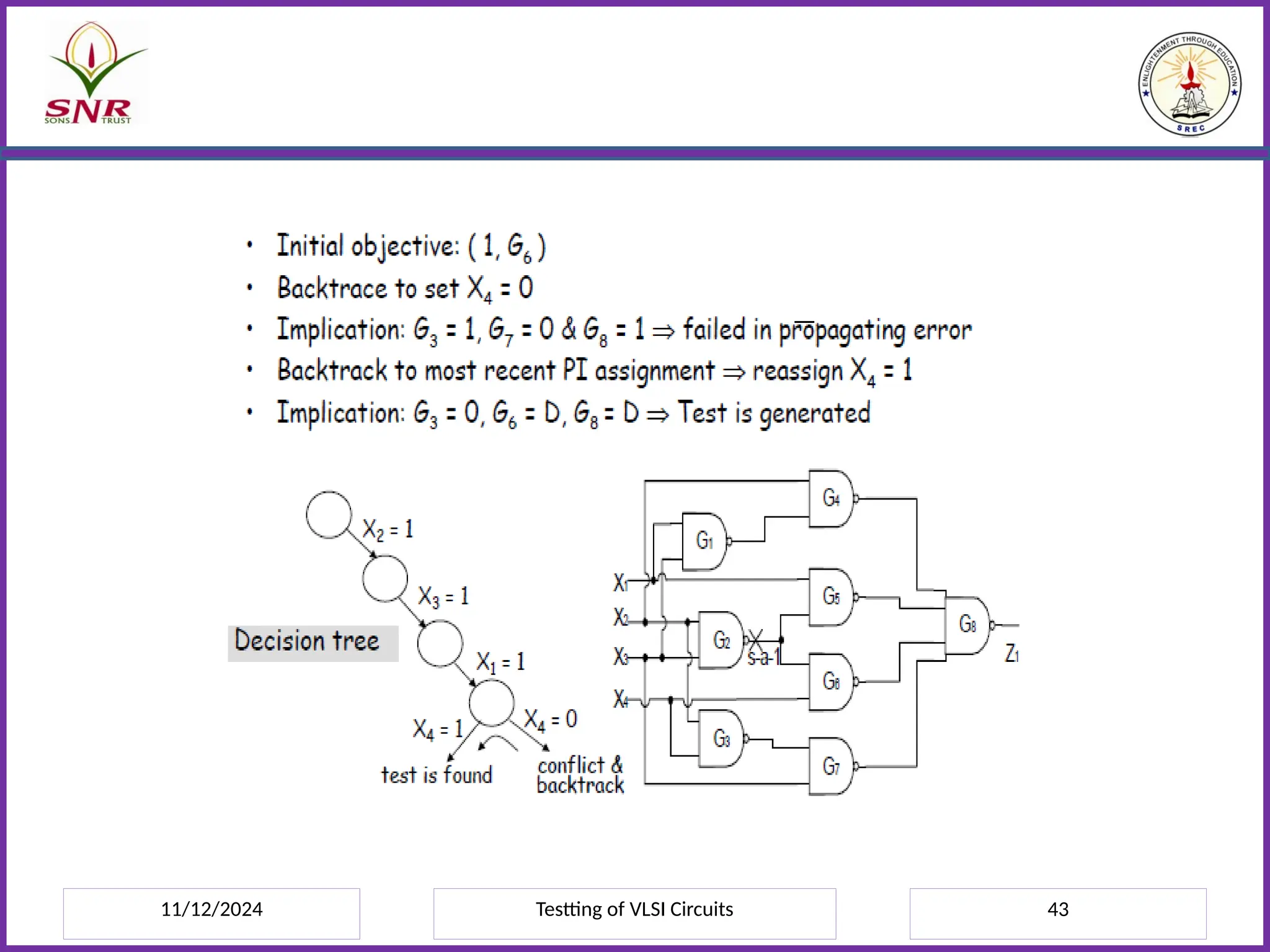

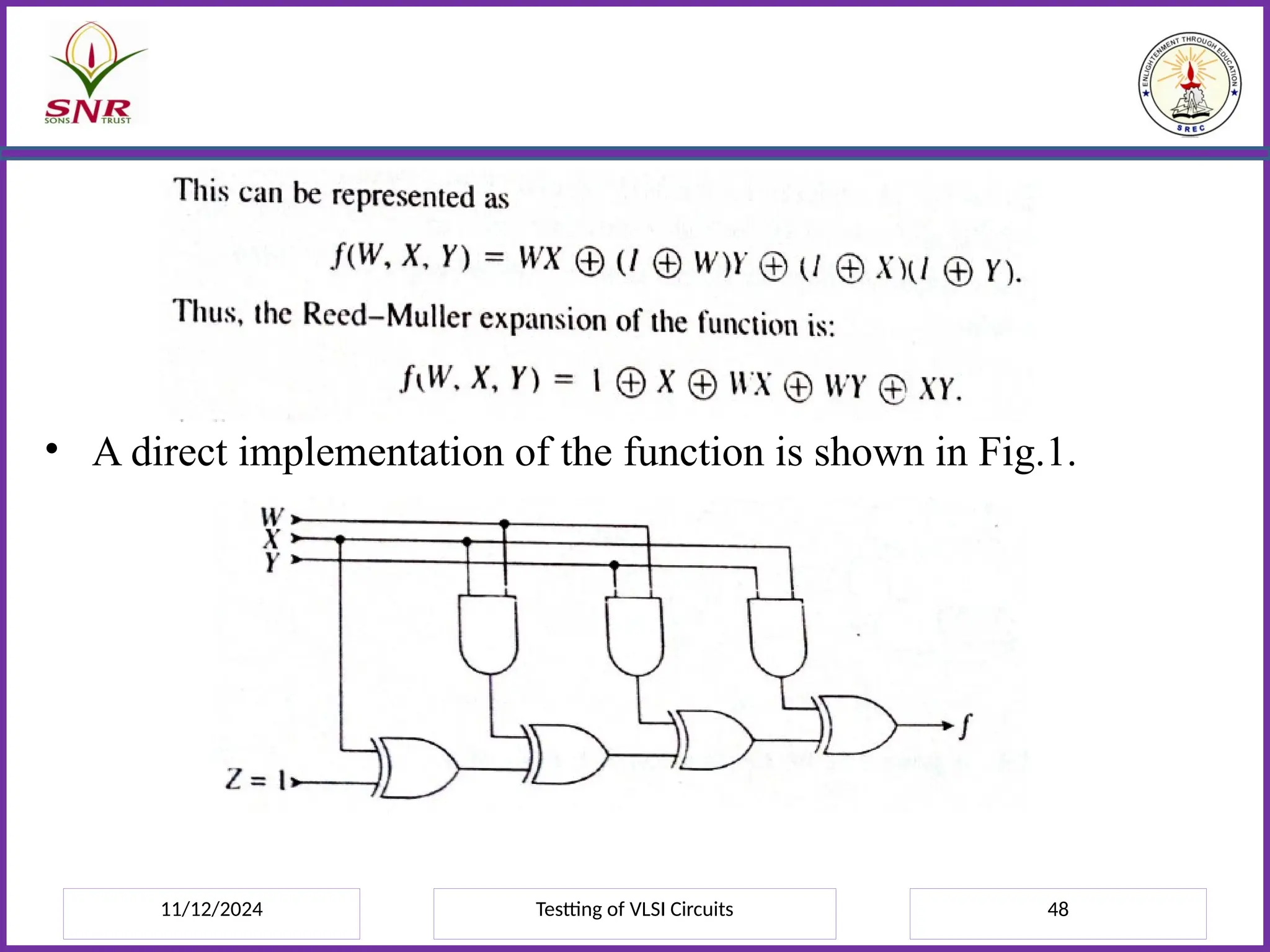

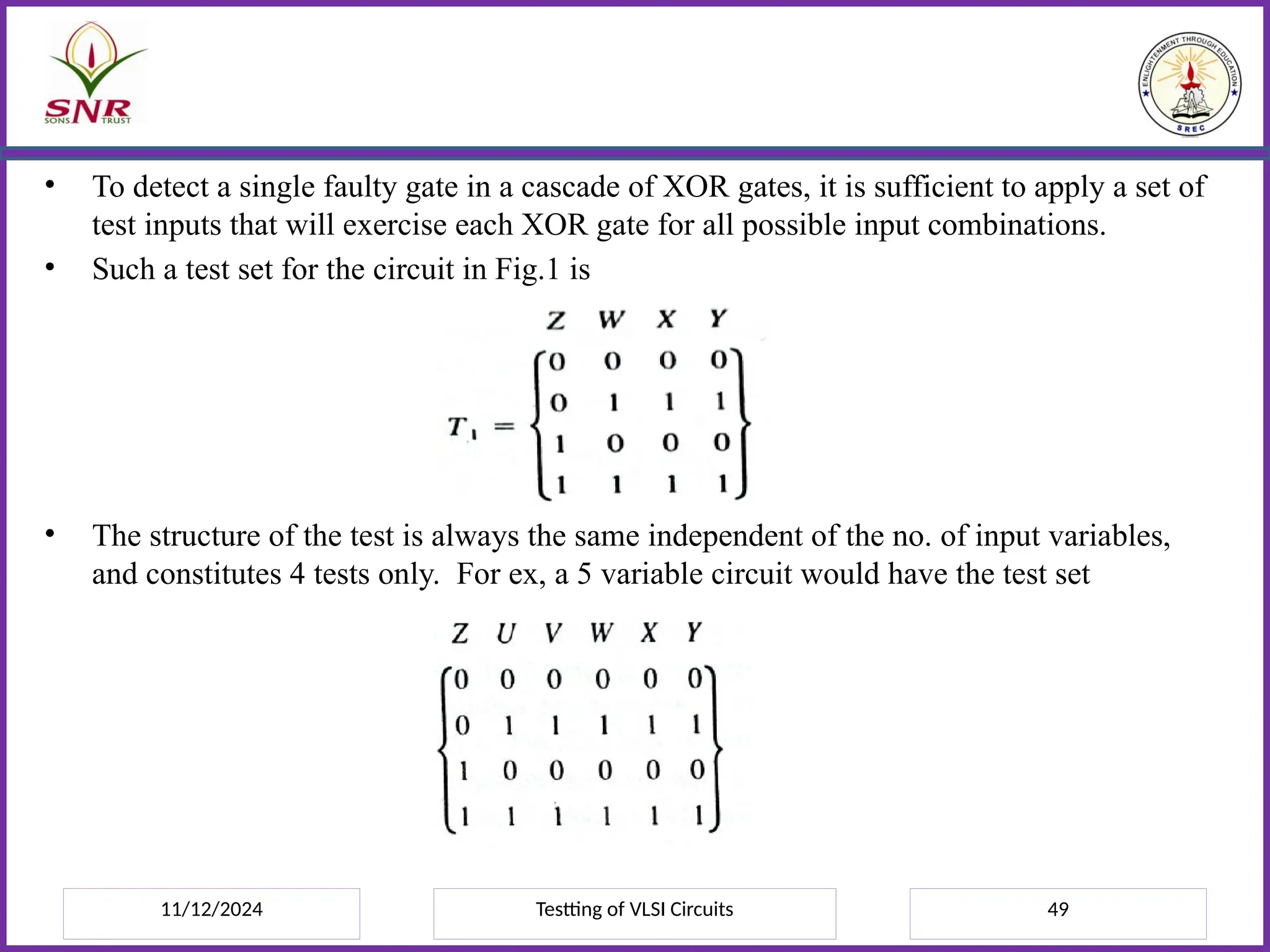

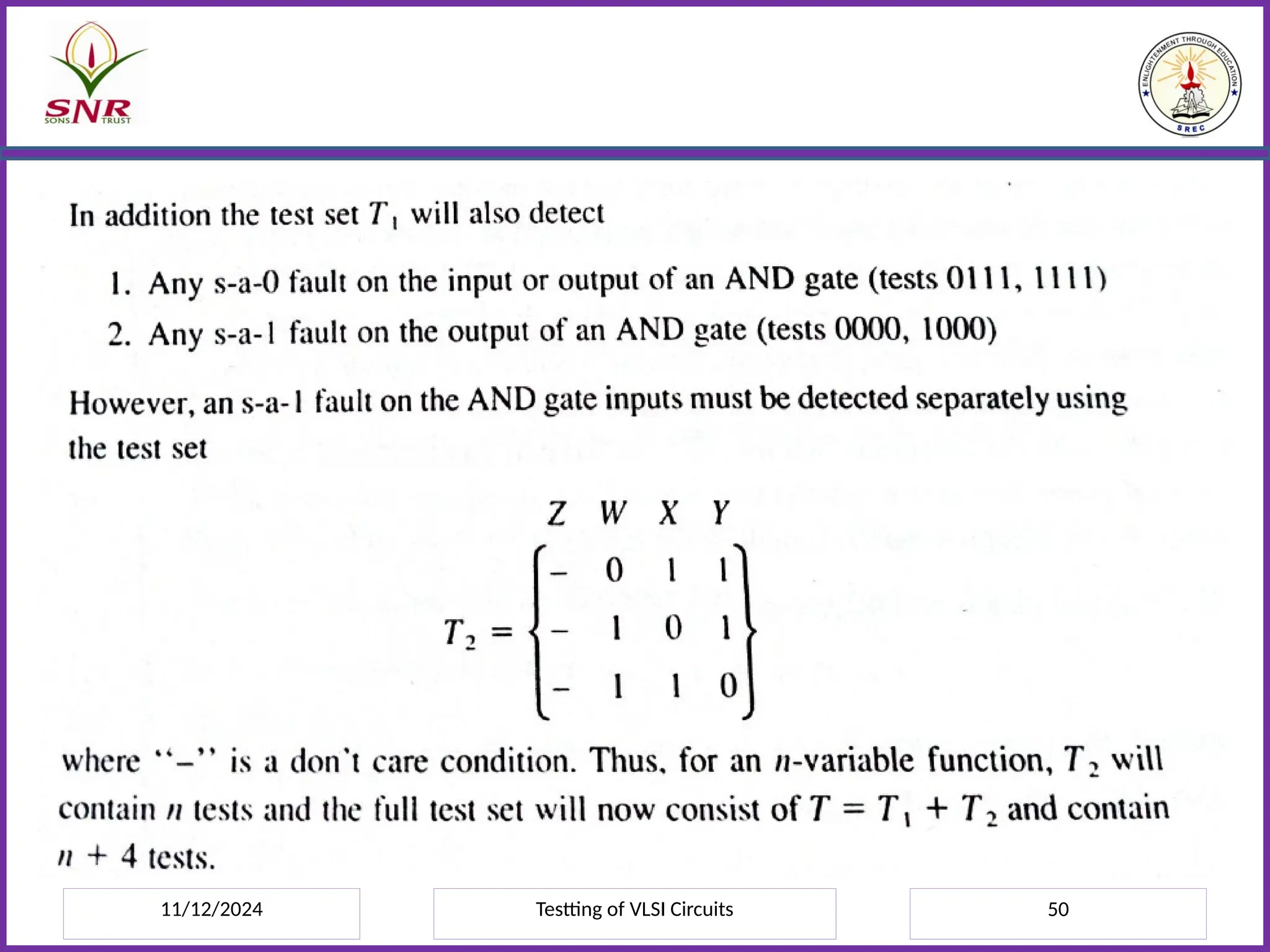

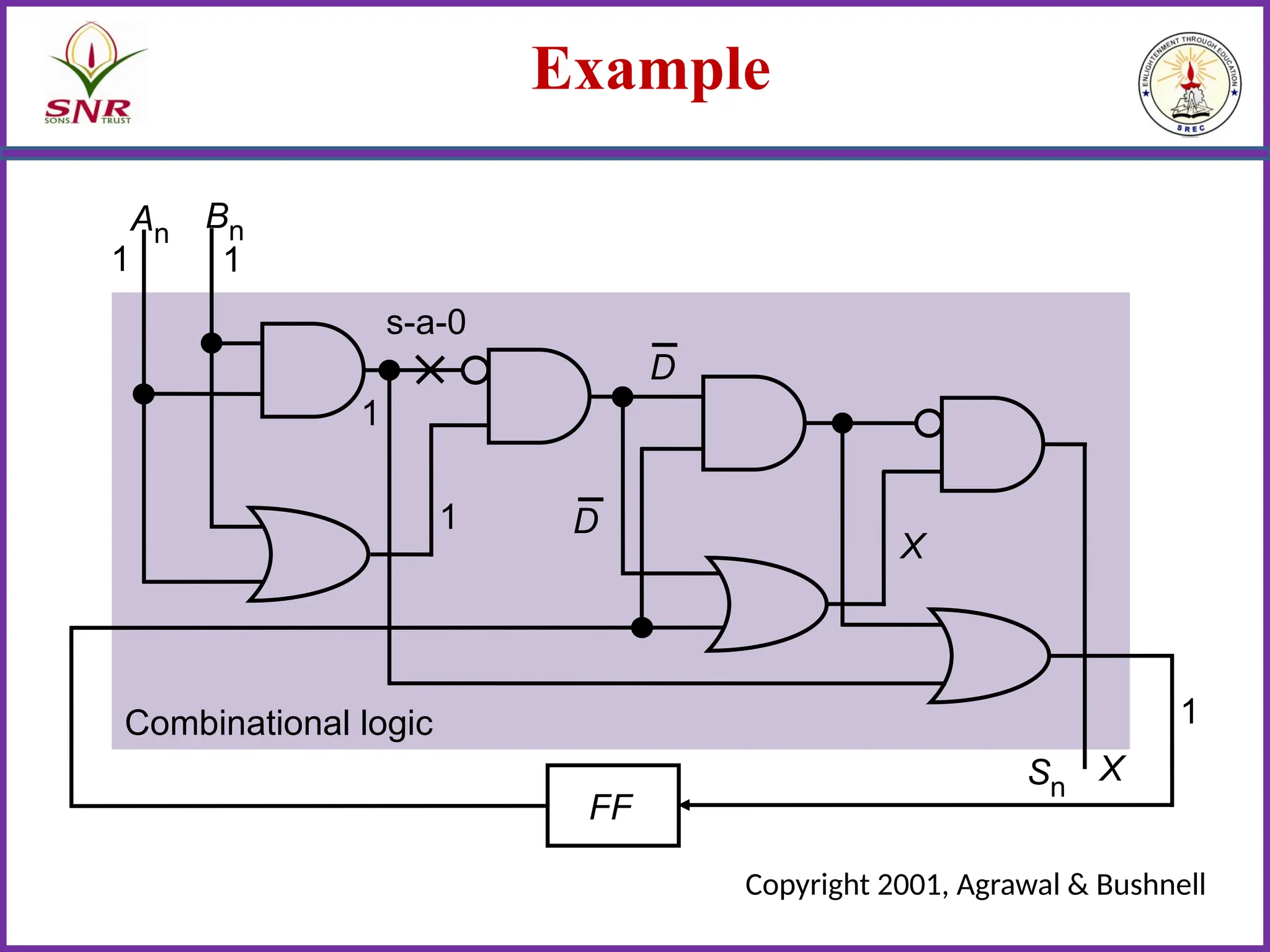

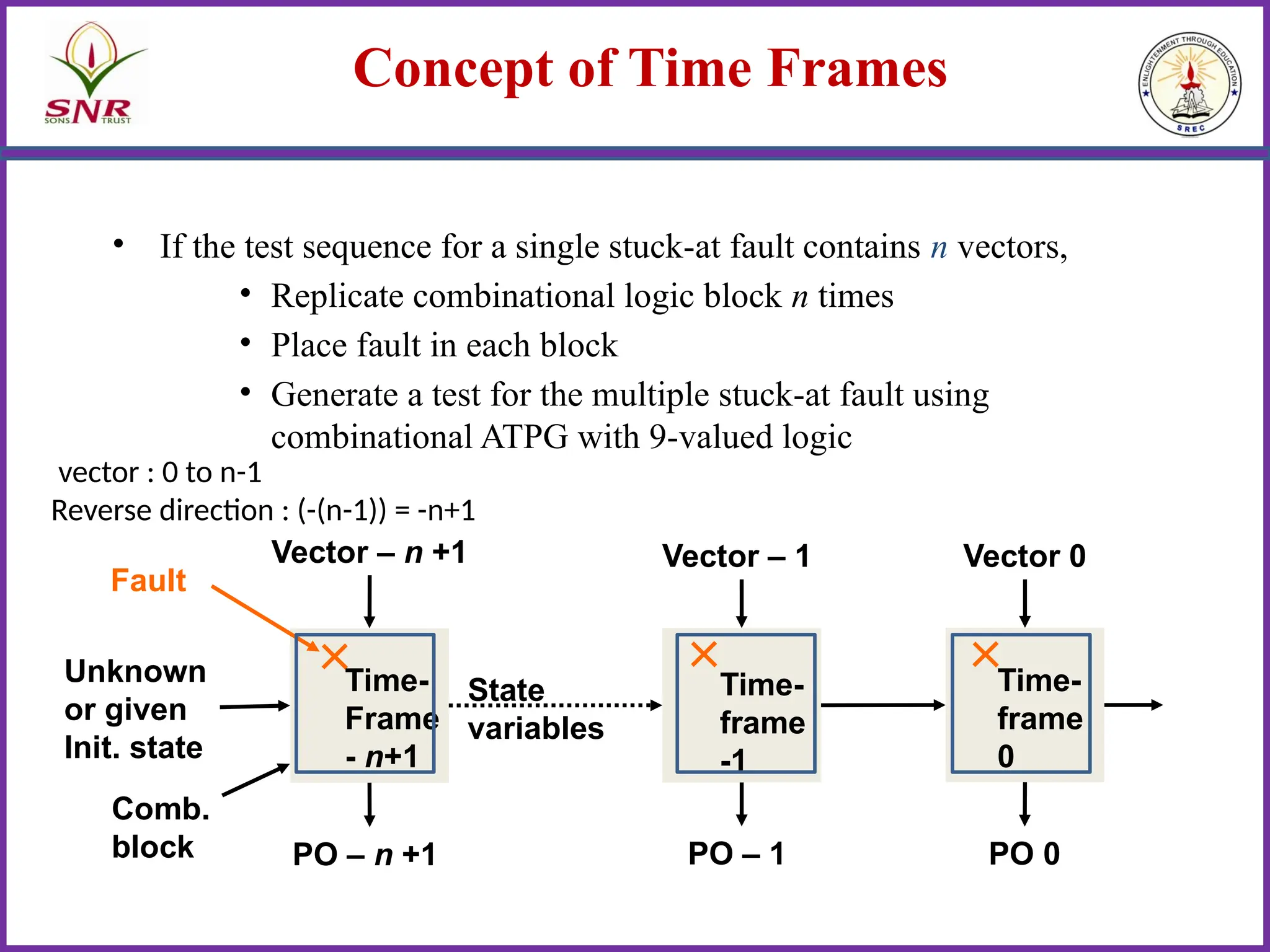

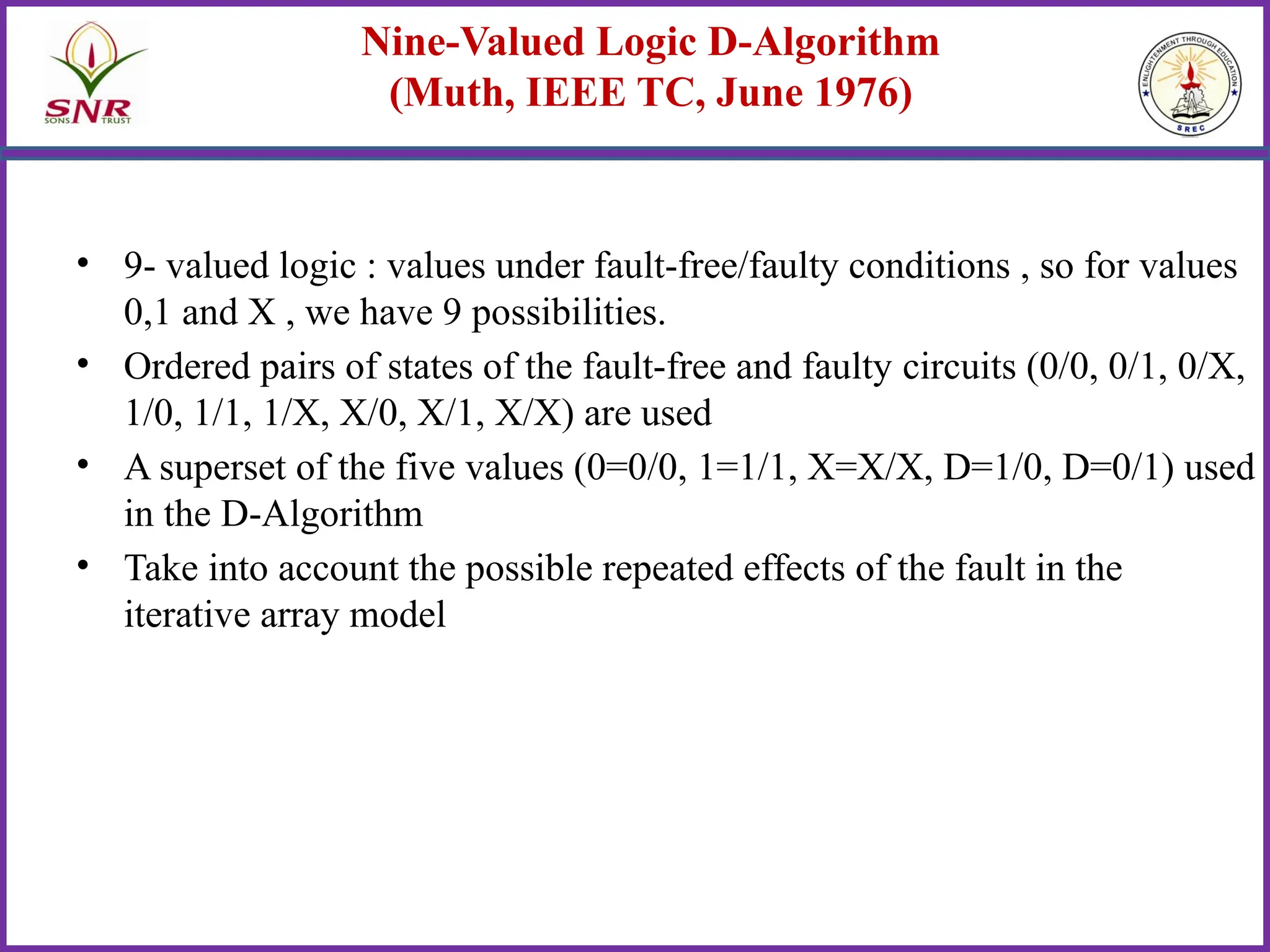

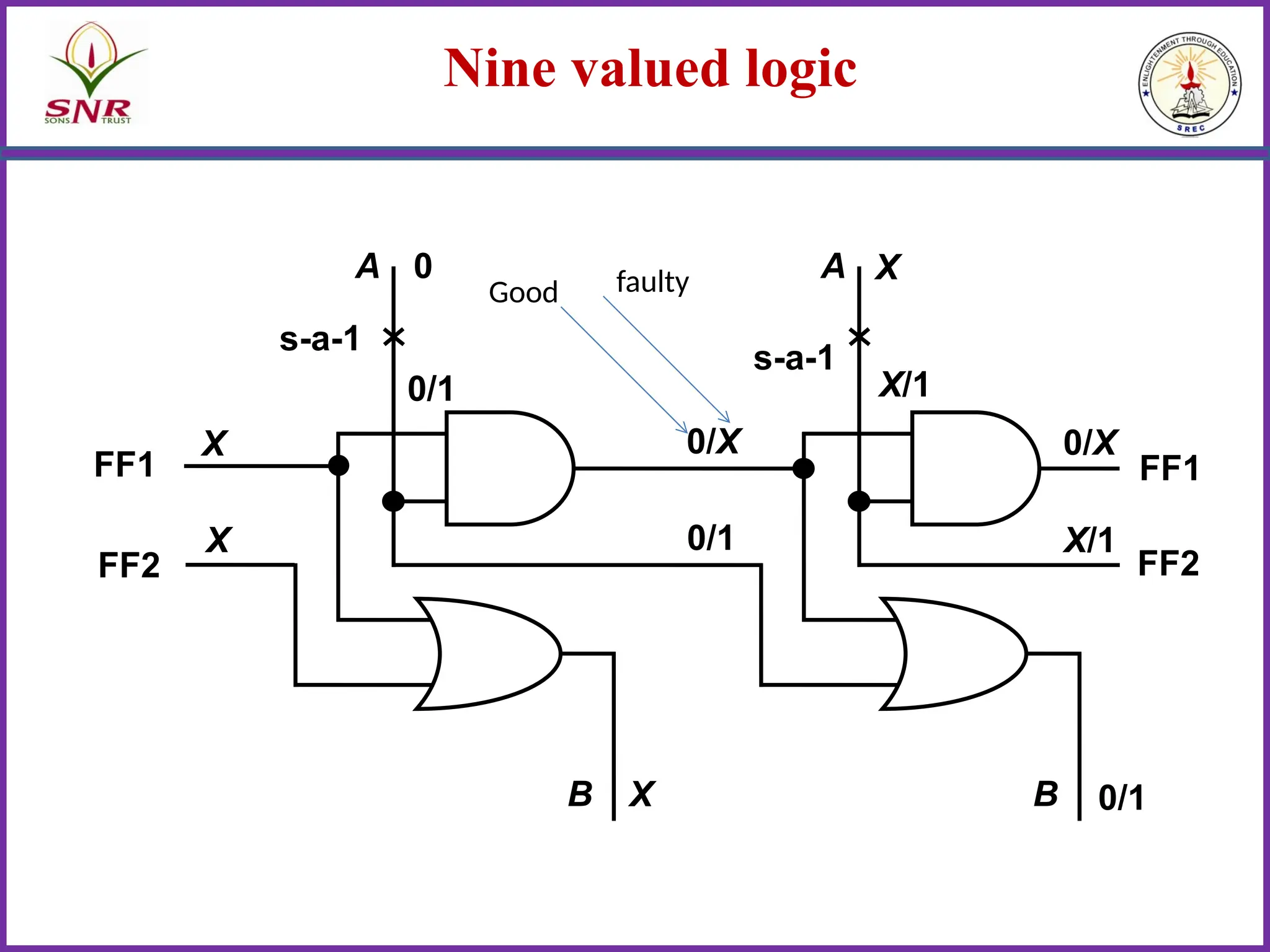

The document discusses VLSI circuit testing, emphasizing the differences between functional and structural testing, the importance of Automatic Test Pattern Generation (ATPG), and various test generation methods including D-algorithm and path sensitization. It highlights the effectiveness of structural testing over functional testing and provides insights into testing combinational and sequential circuits. Additionally, the document addresses the complexities and requirements of ATPG in the context of increasing circuit sizes and clock frequencies.