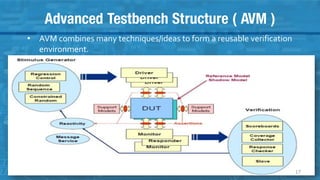

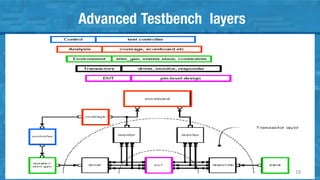

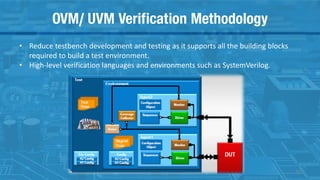

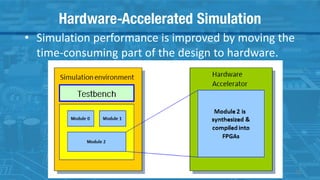

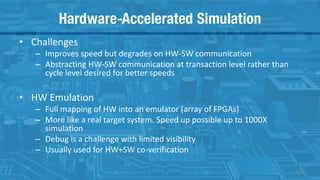

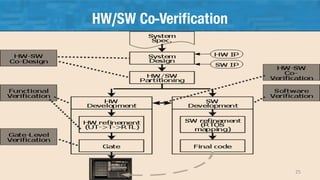

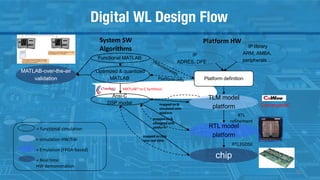

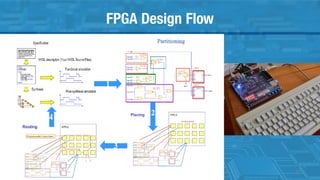

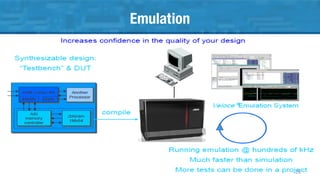

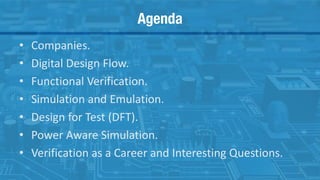

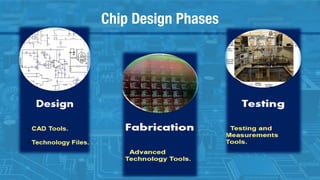

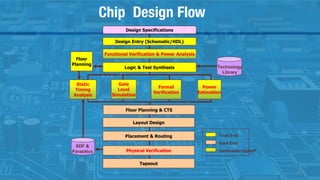

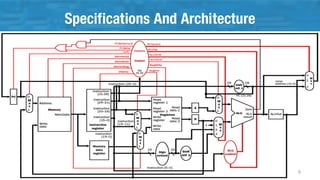

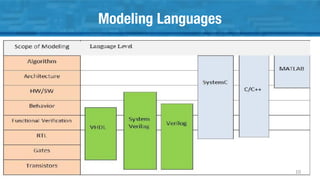

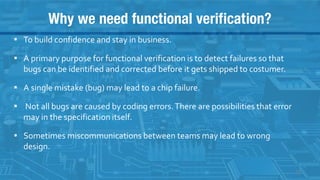

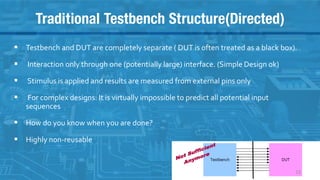

The document discusses functional verification techniques in digital design, emphasizing the importance of detecting and correcting bugs before product delivery. It covers topics such as verification methodologies, testbench structures, and the evolution of verification roles in the industry. Additionally, it explores the career pathways for verification engineers, highlighting the increasing demand and complexity of verification processes.

![Linear Testbench Example

//DUT (Design Under Test)

module adder(a,b,c);

//code start

input [15:0] a;

input [15:0] b;

output [16:0] c;

assign c = a + b;

endmodule

// Testbench Code

module top();

reg [15:0] a;

reg [15:0] b;

wire [16:0] c;

adder DUT(a,b,c); //DUT Instantiation

initial

begin

a = 16'h45; //apply the stimulus

b = 16'h12;

#10

$display("a=%0d,b=%0d,c=%0d",a,b,c);

end

endmodule

16](https://image.slidesharecdn.com/functionalverificationtechniquesew16session-160905204446/85/Functional-verification-techniques-EW16-session-16-320.jpg)