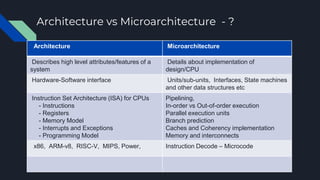

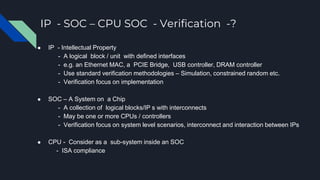

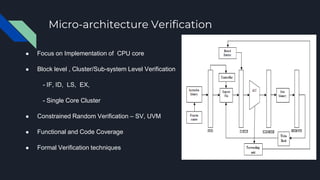

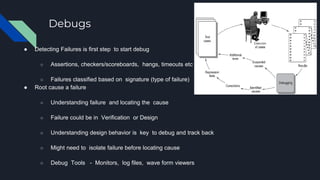

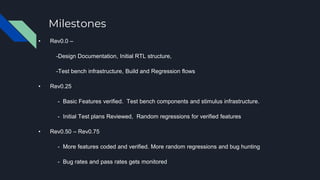

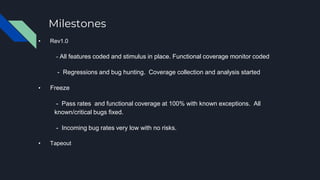

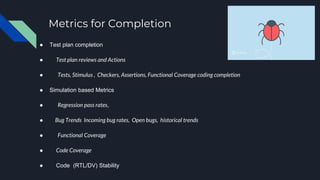

The document discusses CPU verification. It describes verifying at both the architecture and microarchitecture levels. Architecture verification ensures instruction set compliance through random instruction sequences. Microarchitecture verification focuses on implementation details like pipelines and caches using constrained random verification. Milestones track progress through metrics like test plan completion, regression pass rates, functional coverage, and bug trends.