2Sem-MTech-Low Power VLSI Design Homework - Unit1

•

3 likes•6,756 views

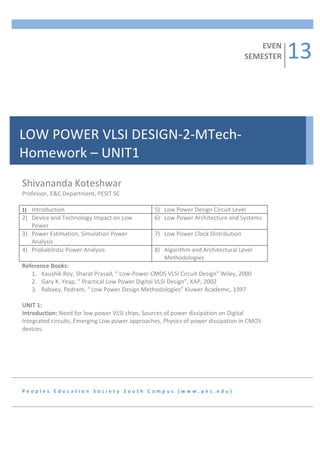

This document outlines the topics and assignments for a Low Power VLSI Design course. The course covers topics like device and technology impacts on low power, power estimation techniques, probabilistic power analysis, low power circuit design, architectures, clock distribution and algorithm/architectural methodologies. It lists reference books and divides the semester into 8 units covering these topics. It also includes a homework assignment dividing a set of paper submission topics and questions among student teams.

Report

Share

Report

Share

Recommended

Low power vlsi design ppt

it is class notes given by Prof. Dr R.Nakkeeran,At Dept. of Electronics engineering, Pondicherry university,India on Low Power Vlsi Design.

Low power embedded system design

Sources of Power Dissipation

Dynamic Power Dissipation

Static Power Dissipation

Power Reduction Techniques

Algorithmic Power Minimization

Architectural Power Minimization

Logic and Circuit Level Power Minimization

Control Logic Power Minimization

System Level Power Management.

Low Power Memory

This presentation illustrates a few techniques to reduce power dissipation crucial in low power memory designs of today!

Analysis of Power Dissipation & Low Power VLSI Chip Design

Low power requirement has become a principal motto in today’s world of electronics

industries. Power dissipation has becoming an important consideration as performance and area for

VLSI Chip design. With reducing the chip size, reduced power consumption and power management

on chip are the key challenges due to increased complexity. Low power chip requirement in the

VLSI industry is main considerable field due to the reduction of chip dimension day by day and

environmental factors. For many designs, optimization of power is important as timing due to the

need to reduce package cost and extended battery life. This paper present various techniques to

reduce the power requirement in various stages of CMOS designing i.e. Dynamic Power

Suppression, Adiabatic Circuits, Logic Design for Low Power, Reducing Glitches, Logic Level

Power Optimization, Standby Mode Leakage Suppression, Variable Body Biasing, Sleep Transistors,

Dynamic Threshold MOS, Short Circuit Power Suppression.

Advanced Low Power Techniques in Chip Design

Faculty Development Program on “Advances in VLSI Design”

BIT College, Bengaluru

Recommended

Low power vlsi design ppt

it is class notes given by Prof. Dr R.Nakkeeran,At Dept. of Electronics engineering, Pondicherry university,India on Low Power Vlsi Design.

Low power embedded system design

Sources of Power Dissipation

Dynamic Power Dissipation

Static Power Dissipation

Power Reduction Techniques

Algorithmic Power Minimization

Architectural Power Minimization

Logic and Circuit Level Power Minimization

Control Logic Power Minimization

System Level Power Management.

Low Power Memory

This presentation illustrates a few techniques to reduce power dissipation crucial in low power memory designs of today!

Analysis of Power Dissipation & Low Power VLSI Chip Design

Low power requirement has become a principal motto in today’s world of electronics

industries. Power dissipation has becoming an important consideration as performance and area for

VLSI Chip design. With reducing the chip size, reduced power consumption and power management

on chip are the key challenges due to increased complexity. Low power chip requirement in the

VLSI industry is main considerable field due to the reduction of chip dimension day by day and

environmental factors. For many designs, optimization of power is important as timing due to the

need to reduce package cost and extended battery life. This paper present various techniques to

reduce the power requirement in various stages of CMOS designing i.e. Dynamic Power

Suppression, Adiabatic Circuits, Logic Design for Low Power, Reducing Glitches, Logic Level

Power Optimization, Standby Mode Leakage Suppression, Variable Body Biasing, Sleep Transistors,

Dynamic Threshold MOS, Short Circuit Power Suppression.

Advanced Low Power Techniques in Chip Design

Faculty Development Program on “Advances in VLSI Design”

BIT College, Bengaluru

POWER CONSUMPTION AT CIRCUIT OR LOGIC LEVEL IN CIRCUIT

its a brief description about power consumption in circuit and reduction techniques.

Low Power Design Approach in VLSI

The low power has been the main concern for the VLSI industry with the technology scaling in CMOS process from 130 nm to 22nm. The presentation here gives a brief idea about the several low power VLSI techniques being used in VLSI circuits to reduce the power and delay. for any query feel free to visit us at: http://www.siliconmentor.com/

Adiabatic logic or clock powered logic

It is based on low power technique. One of these techniques are adiabatic logic. This presentation is simple seminar presentation at college.

Low Power Adiabatic Logic Design

Adiabatic describe the thermodynamic processes in which there is no energy exchange with the environment, and therefore very less dissipated energy loss. These circuits are low power circuits which use reversible logic to conserve energy. Adiabatic logic works with the concept of switching activities which reduces the power by giving stored energy back to the supply. The main design changes are focused on power clock which plays the vital role in the principle of operation. This has been used because many adiabaticcircuits use a combined power supply and clock, or a power clock (Four Phase).To achieve this, the power supply of adiabatic logic circuits have used time varying voltage charging signal, in contrast to traditional non-adiabatic systems that have generally used constant voltage charging from a fixed-voltage power supply. Thereby the circuit topology and operation of the circuit has been changed so that the source current of CMOS transistor change its direction and goes back to the supply(Recovery) when the power clock falls from VDD to zero. Power efficient blocks can be designed by using adiabatic logic which can be used in combinational and sequential circuits. The simulation of the designs is done using a backend tool called MENTOR GRAPHICS in 130nm technology

Low power electronic design

Low Power Electronic design is basically compromised with power aware digital system designs techniques. Especially VLSI power architecture with advanced power reduction techniques are discussed in details here

Power Gating

Power gating is the main power reduction techniques for the static power. As long as technology scaling is taking place, static power becomes paramount important factor to the VLSI designs.Therefore Power gating is the recent power reduction technique that is actively in research areas.

Low Power VLSI Design

Low Power VLSI design architecture for EDA (Electronic Design Automation) and Modern Power Estimation, Reduction and Fixing technologies including clock gating and power gating

Embedded Systems Power Management

A review of basic concepts on power consumptions on VLSI architectures and techniques to reduce energy wastage both at architectural and system level

Power Gating Based Ground Bounce Noise Reduction

As low power circuits are most popular the decrease in supply voltage leads to increase in leakage power with respect to the technology scaling. So for removing this kind of leakages and to provide a better power efficiency many power gating techniques are used. But the leakage due to ground connection to the active part of the circuit is very high rather than all other leakages. As it is mainly due to the back EMF of the ground connection it was called it as ground bounce noise. To reduce this noise different methodologies are designed. In this paper the design of such an efficient technique related to ground bounce noise reduction using power gating circuits and comparing the results using DSCH and Microwind low power tools. In this paper the analysis of adders such as full adders using different types of power gated circuits using low power VLSI design techniques and to present the comparison results between different power gating methods.

Low Power VLSI Designs

Low power electronic designs are the gateway to advanced designs in the future

Power Dissipation of VLSI Circuits and Modern Techniques of Designing Low Pow...

This paper focus on the various sources of power dissipation in modern VLSI circuits. This paper also discuss the importance of designing low power VLSI circuits along with various techniques of power reduction and its advantages and disadvantages. It is basically a comparative study between various power reduction techniques in modern VLSI circuits.

Low power in vlsi with upf basics part 1

With Increase in Portable devices, VLSI chips has to consider about Power usages in VLSI silicon chips. So Power Aware design and verification is so important in Industry. To get basic knowledge on Low Power Design and Verification with UPF basics Go through this Slides.

IRJET- High Efficiency Bridge-Less Battery Charger for Light Electric Veh...

https://irjet.net/archives/V7/i2/IRJET-V7I2543.pdf

More Related Content

What's hot

POWER CONSUMPTION AT CIRCUIT OR LOGIC LEVEL IN CIRCUIT

its a brief description about power consumption in circuit and reduction techniques.

Low Power Design Approach in VLSI

The low power has been the main concern for the VLSI industry with the technology scaling in CMOS process from 130 nm to 22nm. The presentation here gives a brief idea about the several low power VLSI techniques being used in VLSI circuits to reduce the power and delay. for any query feel free to visit us at: http://www.siliconmentor.com/

Adiabatic logic or clock powered logic

It is based on low power technique. One of these techniques are adiabatic logic. This presentation is simple seminar presentation at college.

Low Power Adiabatic Logic Design

Adiabatic describe the thermodynamic processes in which there is no energy exchange with the environment, and therefore very less dissipated energy loss. These circuits are low power circuits which use reversible logic to conserve energy. Adiabatic logic works with the concept of switching activities which reduces the power by giving stored energy back to the supply. The main design changes are focused on power clock which plays the vital role in the principle of operation. This has been used because many adiabaticcircuits use a combined power supply and clock, or a power clock (Four Phase).To achieve this, the power supply of adiabatic logic circuits have used time varying voltage charging signal, in contrast to traditional non-adiabatic systems that have generally used constant voltage charging from a fixed-voltage power supply. Thereby the circuit topology and operation of the circuit has been changed so that the source current of CMOS transistor change its direction and goes back to the supply(Recovery) when the power clock falls from VDD to zero. Power efficient blocks can be designed by using adiabatic logic which can be used in combinational and sequential circuits. The simulation of the designs is done using a backend tool called MENTOR GRAPHICS in 130nm technology

Low power electronic design

Low Power Electronic design is basically compromised with power aware digital system designs techniques. Especially VLSI power architecture with advanced power reduction techniques are discussed in details here

Power Gating

Power gating is the main power reduction techniques for the static power. As long as technology scaling is taking place, static power becomes paramount important factor to the VLSI designs.Therefore Power gating is the recent power reduction technique that is actively in research areas.

Low Power VLSI Design

Low Power VLSI design architecture for EDA (Electronic Design Automation) and Modern Power Estimation, Reduction and Fixing technologies including clock gating and power gating

Embedded Systems Power Management

A review of basic concepts on power consumptions on VLSI architectures and techniques to reduce energy wastage both at architectural and system level

Power Gating Based Ground Bounce Noise Reduction

As low power circuits are most popular the decrease in supply voltage leads to increase in leakage power with respect to the technology scaling. So for removing this kind of leakages and to provide a better power efficiency many power gating techniques are used. But the leakage due to ground connection to the active part of the circuit is very high rather than all other leakages. As it is mainly due to the back EMF of the ground connection it was called it as ground bounce noise. To reduce this noise different methodologies are designed. In this paper the design of such an efficient technique related to ground bounce noise reduction using power gating circuits and comparing the results using DSCH and Microwind low power tools. In this paper the analysis of adders such as full adders using different types of power gated circuits using low power VLSI design techniques and to present the comparison results between different power gating methods.

Low Power VLSI Designs

Low power electronic designs are the gateway to advanced designs in the future

Power Dissipation of VLSI Circuits and Modern Techniques of Designing Low Pow...

This paper focus on the various sources of power dissipation in modern VLSI circuits. This paper also discuss the importance of designing low power VLSI circuits along with various techniques of power reduction and its advantages and disadvantages. It is basically a comparative study between various power reduction techniques in modern VLSI circuits.

Low power in vlsi with upf basics part 1

With Increase in Portable devices, VLSI chips has to consider about Power usages in VLSI silicon chips. So Power Aware design and verification is so important in Industry. To get basic knowledge on Low Power Design and Verification with UPF basics Go through this Slides.

IRJET- High Efficiency Bridge-Less Battery Charger for Light Electric Veh...

https://irjet.net/archives/V7/i2/IRJET-V7I2543.pdf

What's hot (19)

POWER CONSUMPTION AT CIRCUIT OR LOGIC LEVEL IN CIRCUIT

POWER CONSUMPTION AT CIRCUIT OR LOGIC LEVEL IN CIRCUIT

Power Dissipation of VLSI Circuits and Modern Techniques of Designing Low Pow...

Power Dissipation of VLSI Circuits and Modern Techniques of Designing Low Pow...

IRJET- High Efficiency Bridge-Less Battery Charger for Light Electric Veh...

IRJET- High Efficiency Bridge-Less Battery Charger for Light Electric Veh...

Viewers also liked

Clock Gating

Clock Gating is the major acenario of dynamic power reduction in VLSI designs of SOC, MPSOC,ASIC, SOPC.

Vlsi power estimation

VLSI power estimation is vital component of the modern electronic designs. Rapid changes in the advanced electronic infrastructure may causes the power to become paramount important in the VLSI designs.

Semiconductor industry for IoT Entrepreneurs

Semiconductor industry for IoT Entrepreneurs

Talk in IISc IIOT Class participants- "4 WEEKS IoT Technologies”

Viewers also liked (17)

Design of 16 bit low power processor using clock gating technique 2-3

Design of 16 bit low power processor using clock gating technique 2-3

Book Summary - What got you here wont get you there!

Book Summary - What got you here wont get you there!

Similar to 2Sem-MTech-Low Power VLSI Design Homework - Unit1

Optimal Capacitor Placement in Distribution System using Fuzzy Techniques

To improve the overall efficiency of power system,

the performance of distribution system must be improved. It

is done by installing shunt capacitors in radial distribution

system. The problem of capacitor allocation in electric

distribution systems involves maximizing “energy and peak

power (demand) loss reductions” by means of capacitor

installations. As a result power factor of distribution system

improves. There is also lots of saving in terms of money. A 10

bus radial distribution system is taken as the model. Then a

load flow programs is executed on MATLAB. Then by using

load flow data & fuzzy techniques the determination of suitable

location of capacitor placement and its size is done. Shunt

capacitors to be placed at the nodes of the system will be

represented as reactive power injections. Fuzzy techniques have

advantages of simplicity, less computations & fast results. The

same techniques can be applied to complex distribution systems

& dynamic loads.

International Journal of Engineering Inventions (IJEI)

International Journal of Engineering Inventions (IJEI)International Journal of Engineering Inventions www.ijeijournal.com

www.ijeijournal.comA Literature Survey on Energy Efficient MAC Protocols For WSN

https://www.irjet.net/archives/V4/i3/IRJET-V4I3626.pdf

High performance novel dual stack gating technique for reduction of ground bo...

Abstract The development of digital integrated circuits is challenged by higher power consumption. The combination of higher clock speeds, greater functional integration, and smaller process geometries has contributed to significant growth in power density. Today leakage power has become an increasingly important issue in processor hardware and software design. So to reduce the leakages in the circuit many low power strategies are identified and experiments are carried out. But the leakage due to ground connection to the active part of the circuit is very higher than all other leakages. As it is mainly due to the back EMF of the ground connection we are calling it as ground bounce noise. To reduce this noise, different methodologies are designed. In this paper, a number of critical considerations in the sleep transistor design and implementation includes header or footer switch selection, sleep transistor distribution choices and sleep transistor gate length, width and body bias optimization for area, leakage and efficiency. Novel dual stack technique is proposed that reduces not only the leakage power but also dynamic power. The previous techniques are summarized and compared with this new approach and comparison of both the techniques is done with the help of Digital Schematic( DSCH ) and Microwind low power tools. Stacking power gating technique has been analyzed and the conditions for the important design parameters (Minimum ground bounce noise) have been derived. The Monte-Carlo simulation is performed in Microwind to calculate the values of all the needed parameters for comparison. Index Terms: Ground Bounce Noise ,Power gating schemes ,Static power dissipation, Dynamic power dissipation, Power gating parameters, Sleep transistors, Novel dual stack approach, Transistor leakage power

IMPLEMENTATION OF LOW POWER ADIABATIC SRAM

In the featuring VLSI era, compact electronic devices are popular. The reliability and durability of such compact devices relies on low power utilization. The purpose of this project was to implement a low power adiabatic Static Random Access Memory (SRAM), with the following objectives - To reduce the power waste by means of stepwise charging using tank capacitors which is an adiabatic way of generating power

clock. This method is capable of recuperating the electrical energy back to the source. Further to examine the Static Noise Margin (SNM) – a parameter which gives detailed information about the cell stability – in

contrast with conventional 6T, 7T and 8T topologies of SRAM under 180 nm technology. Finally, SNM variations with respect to process parameters are also discussed. All the implementations and analysis were made using CADENCE tool and MATLAB tool.

IMPLEMENTATION OF LOW POWER ADIABATIC SRAM

In the featuring VLSI era, compact electronic devices are popular. The reliability and durability of such compact devices relies on low power utilization. The purpose of this project was to implement a low power adiabatic Static Random Access Memory (SRAM), with the following objectives - To reduce the power waste by means of stepwise charging using tank capacitors which is an adiabatic way of generating power

clock. This method is capable of recuperating the electrical energy back to the source. Further to examine the Static Noise Margin (SNM) – a parameter which gives detailed information about the cell stability – in contrast with conventional 6T, 7T and 8T topologies of SRAM under 180 nm technology. Finally, SNM

variations with respect to process parameters are also discussed. All the implementations and analysis were made using CADENCE tool and MATLAB tool.

IMPLEMENTATION OF LOW POWER ADIABATIC SRAM

In the featuring VLSI era, compact electronic devices are popular. The reliability and durability of such compact devices relies on low power utilization. The purpose of this project was to implement a low power adiabatic Static Random Access Memory (SRAM), with the following objectives - To reduce the power waste by means of stepwise charging using tank capacitors which is an adiabatic way of generating power clock. This method is capable of recuperating the electrical energy back to the source. Further to examine the Static Noise Margin (SNM) – a parameter which gives detailed information about the cell stability – in contrast with conventional 6T, 7T and 8T topologies of SRAM under 180 nm technology. Finally, SNM variations with respect to process parameters are also discussed. All the implementations and analysis were made using CADENCE tool and MATLAB tool.

L24093097

IJERA (International journal of Engineering Research and Applications) is International online, ... peer reviewed journal. For more detail or submit your article, please visit www.ijera.com

IRJET- An Enhanced Cluster (CH-LEACH) based Routing Scheme for Wireless Senso...

https://www.irjet.net/archives/V6/i3/IRJET-V6I3275.pdf

IRJET- Fitness Function as Trust Value using to Efficient Multipath Routi...

https://www.irjet.net/archives/V6/i5/IRJET-V6I5914.pdf

Lb2418671870

IJERA (International journal of Engineering Research and Applications) is International online, ... peer reviewed journal. For more detail or submit your article, please visit www.ijera.com

Dc31712719

IJERA (International journal of Engineering Research and Applications) is International online, ... peer reviewed journal. For more detail or submit your article, please visit www.ijera.com

Wireless Sensor Grids Energy Efficiency Enrichment Using Quorum Techniques

IOSR Journal of Computer Engineering (IOSR-JCE) vol.17 issue.1 version.6

Using the CC2430 and TIMAC for low-power wireless sensor applications: A powe...

Study on how to achieve low-power operations with a CC2430 based TIMAC beacon network. From TI’s Q2 2008 Analog Applications Journal

Seminar 12-11-19

Presentation Slides by Pipat Methavanitpong about the author for Seminar class Nov 19, 2012 at Kunieda-Isshiki Laboratory, Tokyo Institute of Technology.

Similar to 2Sem-MTech-Low Power VLSI Design Homework - Unit1 (20)

Optimal Capacitor Placement in Distribution System using Fuzzy Techniques

Optimal Capacitor Placement in Distribution System using Fuzzy Techniques

International Journal of Engineering Inventions (IJEI)

International Journal of Engineering Inventions (IJEI)

A Literature Survey on Energy Efficient MAC Protocols For WSN

A Literature Survey on Energy Efficient MAC Protocols For WSN

High performance novel dual stack gating technique for reduction of ground bo...

High performance novel dual stack gating technique for reduction of ground bo...

IRJET- An Enhanced Cluster (CH-LEACH) based Routing Scheme for Wireless Senso...

IRJET- An Enhanced Cluster (CH-LEACH) based Routing Scheme for Wireless Senso...

IRJET- Fitness Function as Trust Value using to Efficient Multipath Routi...

IRJET- Fitness Function as Trust Value using to Efficient Multipath Routi...

Wireless Sensor Grids Energy Efficiency Enrichment Using Quorum Techniques

Wireless Sensor Grids Energy Efficiency Enrichment Using Quorum Techniques

Using the CC2430 and TIMAC for low-power wireless sensor applications: A powe...

Using the CC2430 and TIMAC for low-power wireless sensor applications: A powe...

More from Dr. Shivananda Koteshwar

Aurinko Open Day (Pre KG to 10th Grade)

Open Day Presentation for Aurinko Academy (Pre KG to 10th Grade)

BELAKUBE METHODOLOGY

We have developed an open source methodology called “Belakube” which helps teachers and volunteers alike to engage with kids (K1 to K10) and offer supplementary education

Social Entrepreneurship

National e Conference on Social Entrepreneurship - Issues and Challenges sponsored by AICTE and organized by MS Ramaiah Institue of Technology

Innovation in GCC - Global Capability Center

Presentation in MIT-ID

The presentation covers the summary of GCC in India, the journey of Offshore center to GCC, and adding one more dimension to Thinking to bring back "R" in R&D.

Corporate Expectation from a MBA Graduate

Knowledge Skills Attitude required to land a job in the corporate world for freshers from MBA colleges

Introduction to consultancy for MBA Freshers

Introduction to consultancy for MBA Freshers

Amity Global Business School

Bachelor of Design (BDes)

BDes course in India. What/how part is answered

Aurinko, India's first Design Preparatory School

Understanding scale Clean tech and Agritech verticals

Understanding Scale Up Challenges and know hows in CleanTech and AgriTech vertical

Guest talk in IISC CCE Class

Evolution and Advancement in Chipsets

AliensFest 4.0 in Gitam University, Hyderabad: 5000+ Students from 150 colleges across India, 50+ Prototypes, 50+ Experts, 100+ Companies, 25 Workshops, 1 Hackathon, 10 Technology Experience Zones, Technology Launchpad, 50+ Stalls in Expo.

TOPIC: Evolution and Advancement in Chipsets and opportunities for students in it

Engaging Today's kids

Talk to all Head Masters of Government schools and Block Education Officer (BEO) in Hoskote, Karnataka

Nurturing Innovative Minds

CFAL Mangalore

Makers Fete Talk to Teachers of HighSchool

NITI ATAL Menter of Change

Creating those dots

CFAL Mangalore

Makers Fete Talk to Students of HighSchool

https://www.makeatcfal.com/makers-fete

More from Dr. Shivananda Koteshwar (20)

Understanding scale Clean tech and Agritech verticals

Understanding scale Clean tech and Agritech verticals

IoT product business plan creation for entrepreneurs and intrepreneurs

IoT product business plan creation for entrepreneurs and intrepreneurs

ASIC SoC Verification Challenges and Methodologies

ASIC SoC Verification Challenges and Methodologies

Recently uploaded

The French Revolution Class 9 Study Material pdf free download

The French Revolution, which began in 1789, was a period of radical social and political upheaval in France. It marked the decline of absolute monarchies, the rise of secular and democratic republics, and the eventual rise of Napoleon Bonaparte. This revolutionary period is crucial in understanding the transition from feudalism to modernity in Europe.

For more information, visit-www.vavaclasses.com

A Survey of Techniques for Maximizing LLM Performance.pptx

A Survey of Techniques for Maximizing LLM Performance

Synthetic Fiber Construction in lab .pptx

Synthetic fiber production is a fascinating and complex field that blends chemistry, engineering, and environmental science. By understanding these aspects, students can gain a comprehensive view of synthetic fiber production, its impact on society and the environment, and the potential for future innovations. Synthetic fibers play a crucial role in modern society, impacting various aspects of daily life, industry, and the environment. ynthetic fibers are integral to modern life, offering a range of benefits from cost-effectiveness and versatility to innovative applications and performance characteristics. While they pose environmental challenges, ongoing research and development aim to create more sustainable and eco-friendly alternatives. Understanding the importance of synthetic fibers helps in appreciating their role in the economy, industry, and daily life, while also emphasizing the need for sustainable practices and innovation.

"Protectable subject matters, Protection in biotechnology, Protection of othe...

Protectable subject matters, Protection in biotechnology, Protection of other biological materials, Ownership and period of protection

CACJapan - GROUP Presentation 1- Wk 4.pdf

Macroeconomics- Movie Location

This will be used as part of your Personal Professional Portfolio once graded.

Objective:

Prepare a presentation or a paper using research, basic comparative analysis, data organization and application of economic information. You will make an informed assessment of an economic climate outside of the United States to accomplish an entertainment industry objective.

Model Attribute Check Company Auto Property

In Odoo, the multi-company feature allows you to manage multiple companies within a single Odoo database instance. Each company can have its own configurations while still sharing common resources such as products, customers, and suppliers.

Best Digital Marketing Institute In NOIDA

Safalta Digital marketing institute in Noida, provide complete applications that encompass a huge range of virtual advertising and marketing additives, which includes search engine optimization, virtual communication advertising, pay-per-click on marketing, content material advertising, internet analytics, and greater. These university courses are designed for students who possess a comprehensive understanding of virtual marketing strategies and attributes.Safalta Digital Marketing Institute in Noida is a first choice for young individuals or students who are looking to start their careers in the field of digital advertising. The institute gives specialized courses designed and certification.

for beginners, providing thorough training in areas such as SEO, digital communication marketing, and PPC training in Noida. After finishing the program, students receive the certifications recognised by top different universitie, setting a strong foundation for a successful career in digital marketing.

Francesca Gottschalk - How can education support child empowerment.pptx

Francesca Gottschalk from the OECD’s Centre for Educational Research and Innovation presents at the Ask an Expert Webinar: How can education support child empowerment?

Introduction to AI for Nonprofits with Tapp Network

Dive into the world of AI! Experts Jon Hill and Tareq Monaur will guide you through AI's role in enhancing nonprofit websites and basic marketing strategies, making it easy to understand and apply.

Mule 4.6 & Java 17 Upgrade | MuleSoft Mysore Meetup #46

Mule 4.6 & Java 17 Upgrade | MuleSoft Mysore Meetup #46

Event Link:-

https://meetups.mulesoft.com/events/details/mulesoft-mysore-presents-exploring-gemini-ai-and-integration-with-mulesoft/

Agenda

● Java 17 Upgrade Overview

● Why and by when do customers need to upgrade to Java 17?

● Is there any immediate impact to upgrading to Mule Runtime 4.6 and beyond?

● Which MuleSoft products are in scope?

For Upcoming Meetups Join Mysore Meetup Group - https://meetups.mulesoft.com/mysore/

YouTube:- youtube.com/@mulesoftmysore

Mysore WhatsApp group:- https://chat.whatsapp.com/EhqtHtCC75vCAX7gaO842N

Speaker:-

Shubham Chaurasia - https://www.linkedin.com/in/shubhamchaurasia1/

Priya Shaw - https://www.linkedin.com/in/priya-shaw

Organizers:-

Shubham Chaurasia - https://www.linkedin.com/in/shubhamchaurasia1/

Giridhar Meka - https://www.linkedin.com/in/giridharmeka

Priya Shaw - https://www.linkedin.com/in/priya-shaw

Shyam Raj Prasad-

https://www.linkedin.com/in/shyam-raj-prasad/

A Strategic Approach: GenAI in Education

Artificial Intelligence (AI) technologies such as Generative AI, Image Generators and Large Language Models have had a dramatic impact on teaching, learning and assessment over the past 18 months. The most immediate threat AI posed was to Academic Integrity with Higher Education Institutes (HEIs) focusing their efforts on combating the use of GenAI in assessment. Guidelines were developed for staff and students, policies put in place too. Innovative educators have forged paths in the use of Generative AI for teaching, learning and assessments leading to pockets of transformation springing up across HEIs, often with little or no top-down guidance, support or direction.

This Gasta posits a strategic approach to integrating AI into HEIs to prepare staff, students and the curriculum for an evolving world and workplace. We will highlight the advantages of working with these technologies beyond the realm of teaching, learning and assessment by considering prompt engineering skills, industry impact, curriculum changes, and the need for staff upskilling. In contrast, not engaging strategically with Generative AI poses risks, including falling behind peers, missed opportunities and failing to ensure our graduates remain employable. The rapid evolution of AI technologies necessitates a proactive and strategic approach if we are to remain relevant.

Chapter -12, Antibiotics (One Page Notes).pdf

This is a notes for the D.Pharm students and related to the antibiotic drugs.

Normal Labour/ Stages of Labour/ Mechanism of Labour

Normal labor is also termed spontaneous labor, defined as the natural physiological process through which the fetus, placenta, and membranes are expelled from the uterus through the birth canal at term (37 to 42 weeks

Operation Blue Star - Saka Neela Tara

Operation “Blue Star” is the only event in the history of Independent India where the state went into war with its own people. Even after about 40 years it is not clear if it was culmination of states anger over people of the region, a political game of power or start of dictatorial chapter in the democratic setup.

The people of Punjab felt alienated from main stream due to denial of their just demands during a long democratic struggle since independence. As it happen all over the word, it led to militant struggle with great loss of lives of military, police and civilian personnel. Killing of Indira Gandhi and massacre of innocent Sikhs in Delhi and other India cities was also associated with this movement.

MASS MEDIA STUDIES-835-CLASS XI Resource Material.pdf

mass media studies

CBSE

Full Book

for class 11th

2024.06.01 Introducing a competency framework for languag learning materials ...

http://sandymillin.wordpress.com/iateflwebinar2024

Published classroom materials form the basis of syllabuses, drive teacher professional development, and have a potentially huge influence on learners, teachers and education systems. All teachers also create their own materials, whether a few sentences on a blackboard, a highly-structured fully-realised online course, or anything in between. Despite this, the knowledge and skills needed to create effective language learning materials are rarely part of teacher training, and are mostly learnt by trial and error.

Knowledge and skills frameworks, generally called competency frameworks, for ELT teachers, trainers and managers have existed for a few years now. However, until I created one for my MA dissertation, there wasn’t one drawing together what we need to know and do to be able to effectively produce language learning materials.

This webinar will introduce you to my framework, highlighting the key competencies I identified from my research. It will also show how anybody involved in language teaching (any language, not just English!), teacher training, managing schools or developing language learning materials can benefit from using the framework.

Recently uploaded (20)

The French Revolution Class 9 Study Material pdf free download

The French Revolution Class 9 Study Material pdf free download

A Survey of Techniques for Maximizing LLM Performance.pptx

A Survey of Techniques for Maximizing LLM Performance.pptx

"Protectable subject matters, Protection in biotechnology, Protection of othe...

"Protectable subject matters, Protection in biotechnology, Protection of othe...

Francesca Gottschalk - How can education support child empowerment.pptx

Francesca Gottschalk - How can education support child empowerment.pptx

Introduction to AI for Nonprofits with Tapp Network

Introduction to AI for Nonprofits with Tapp Network

Mule 4.6 & Java 17 Upgrade | MuleSoft Mysore Meetup #46

Mule 4.6 & Java 17 Upgrade | MuleSoft Mysore Meetup #46

Normal Labour/ Stages of Labour/ Mechanism of Labour

Normal Labour/ Stages of Labour/ Mechanism of Labour

MASS MEDIA STUDIES-835-CLASS XI Resource Material.pdf

MASS MEDIA STUDIES-835-CLASS XI Resource Material.pdf

2024.06.01 Introducing a competency framework for languag learning materials ...

2024.06.01 Introducing a competency framework for languag learning materials ...

2Sem-MTech-Low Power VLSI Design Homework - Unit1

- 1. 13 EVEN SEMESTER LOW POWER VLSI DESIGN-‐2-‐MTech-‐ Homework – UNIT1 Shivananda Koteshwar Professor, E&C Department, PESIT SC 1) Introduction 5) Low Power Design Circuit Level 2) Device and Technology Impact on Low 6) Low Power Architecture and Systems Power 3) Power Estimation, Simulation Power 7) Low Power Clock Distribution Analysis 4) Probabilistic Power Analysis 8) Algorithm and Architectural Level Methodologies Reference Books: 1. Kaushik Roy, Sharat Prasad, “ Low-‐Power CMOS VLSI Circuit Design” Wiley, 2000 2. Gary K. Yeap, “ Practical Low Power Digital VLSI Design”, KAP, 2002 3. Rabaey, Pedram, “ Low Power Design Methodologies” Kluwer Academic, 1997 UNIT 1: Introduction: Need for low power VLSI chips, Sources of power dissipation on Digital Integrated circuits, Emerging Low power approaches, Physics of power dissipation in CMOS devices. P e o p l e s E d u c a t i o n S o c i e t y S o u t h C a m p u s ( w w w . p e s . e d u )

- 2. Low Power VLSI Design (2nd Semester) UNIT 1 HW v1.0 Paper Submission Team 1 Need for Low Power VLSI Chips Subramanya / Ravindra 2 Failure Mechanism with Temperature Shivukumar / Amaranath increase 3 Ultra Low Power Device and Applications Sagar / Akshay 4 VI Characteristics of Inverter and Passgate Santosh / Ajit 5 Low/High Vt Cells and MTCMOS Cells Nitin / Zowresh 6 Cooling strategies in a chip Swatishree / Chaitra 7 Packaging techniques and +/- of each Geetanjali / Harshitaa 8 Sources of Power Dissipation Rajshekhar / Vinayak 9 Scaling and different parameters Sandeep / Muralidhar Questions to be answered by all (All are 6marks questions unless specified otherwise) 1. What are the sources of power dissipation in digital ICs ? 2. With usual notation derive the equation for short circuit power dissipation in a CMOS inverter (10m) 3. Discuss the techniques to reduce power dissipation (10m) 4. Write an explanatory notes on physics of power dissipation in MOSFET devices? 5. Explain the need for Low Power VLSI Design 6. Discuss about the dynamic dissipation in CMOS 7. A 32 bit off chip bus operating at 5V and 66MHz clock rate is driving a capacitance of 25pF/bit. Each bit is estimated to have a toggling probability of 0.25 at each clock cycle. What is the power dissipation in operating the bus 8. Explain the basic principle of Low Power Design 9. Derive the most important equation for power dissipation in digital VLSI circuits taking into account the charging and discharging of capacitance in CMOS circuits 10. Explain the effects of input signal slope and output loading capacitance on short circuit current Shivoo Koteshwar’s Notes 2 shivoo@pes.edu