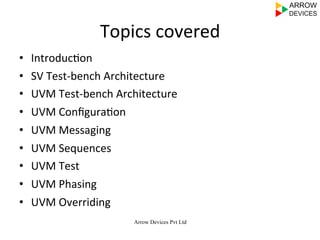

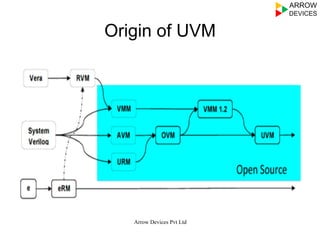

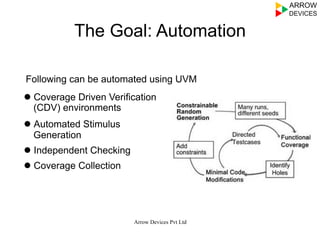

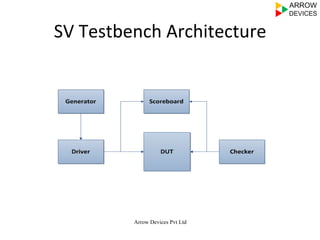

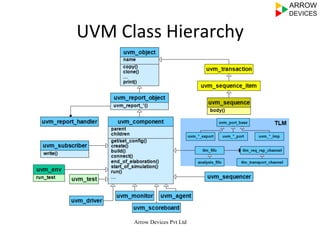

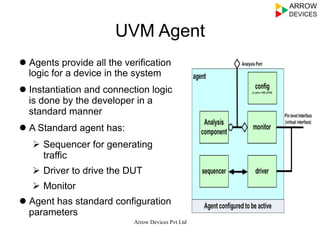

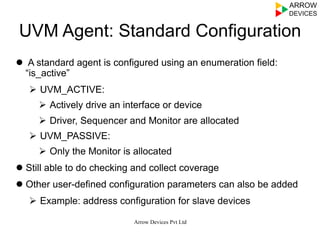

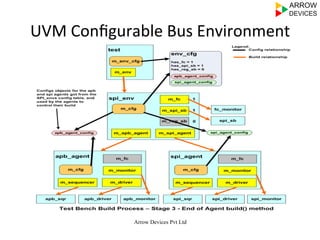

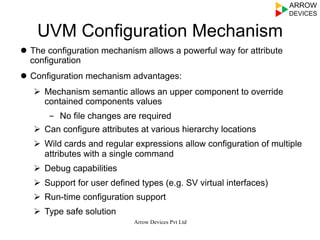

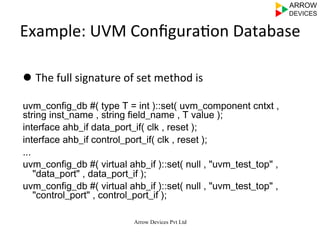

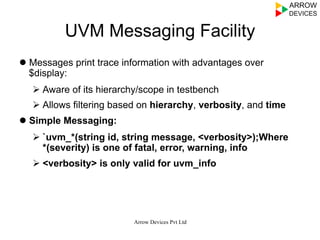

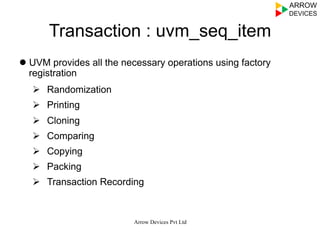

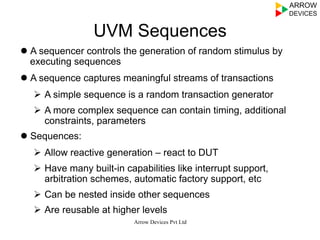

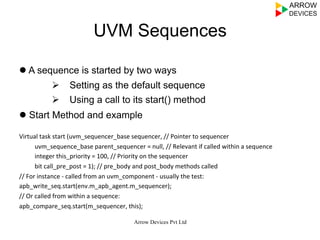

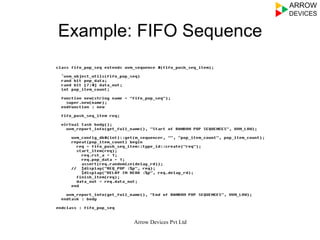

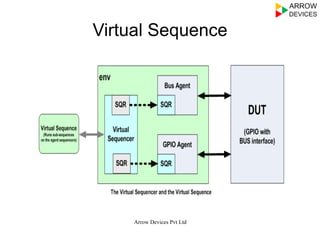

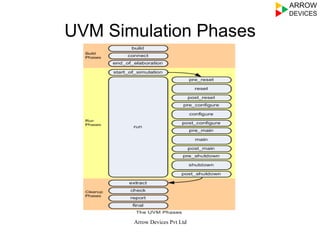

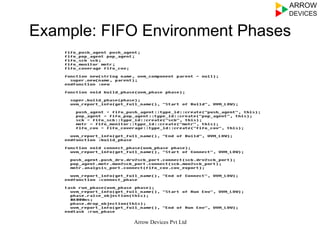

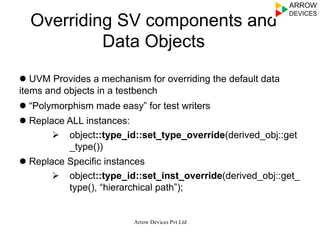

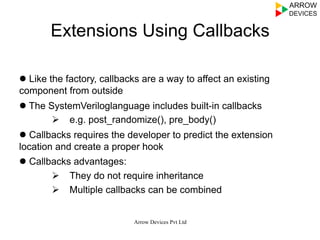

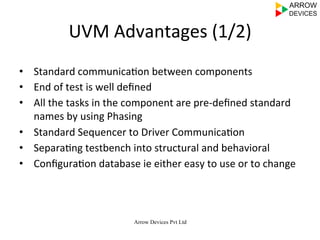

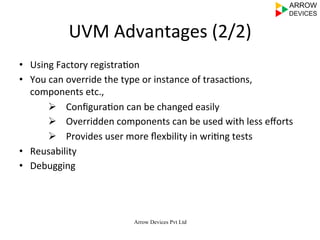

The document outlines the Universal Verification Methodology (UVM) protocol, detailing its architecture, components, and automation capabilities in SystemVerilog test-benches. Key topics include the UVM configuration mechanism, messaging, sequencing, test execution, and advantages such as reusability, standard communication, and flexible component override capabilities. The document serves as a comprehensive guide for utilizing UVM for efficient and organized verification processes.