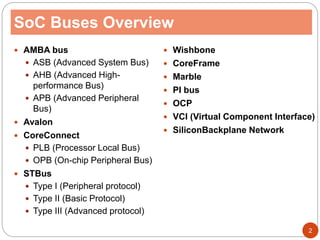

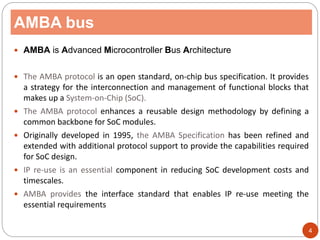

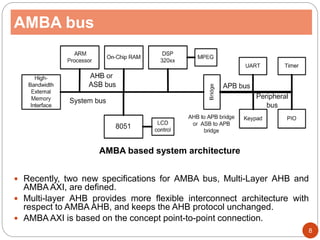

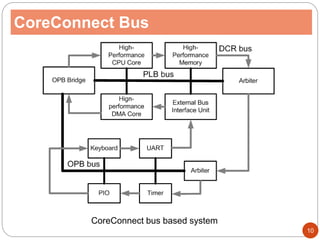

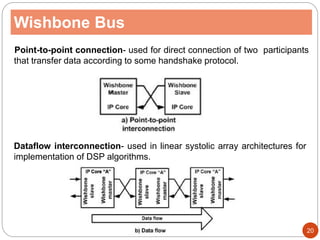

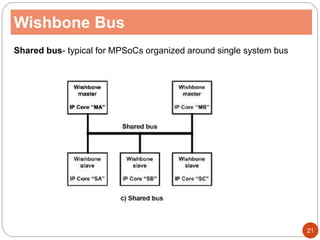

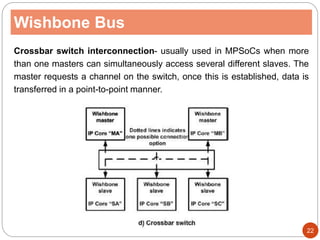

The document discusses various on-chip bus architectures used for system-on-chip designs. It describes buses such as AMBA, CoreConnect, STBus, Wishbone and others. For each bus, it provides details on the bus hierarchy, protocols, and how they enable connection and data transfer between functional blocks in a system-on-chip.