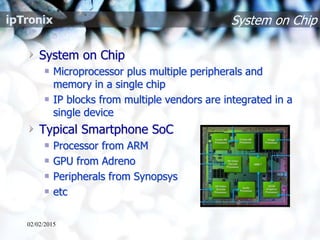

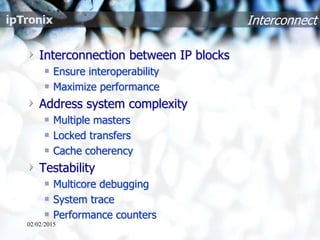

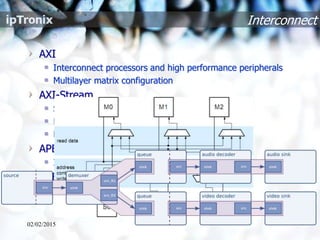

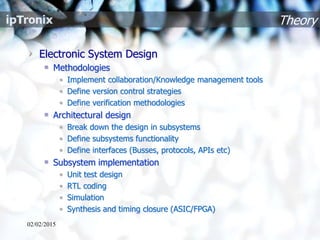

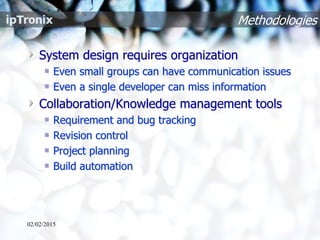

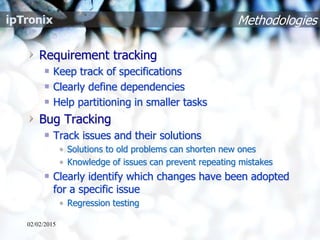

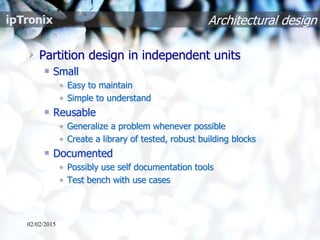

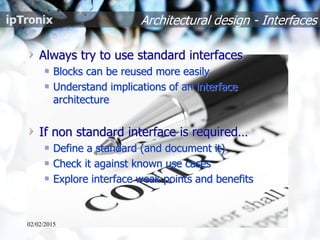

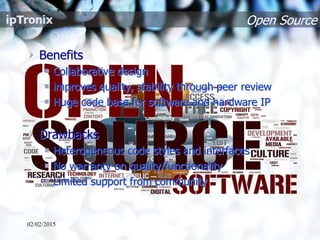

The document discusses system level design methodologies. It recommends implementing collaboration tools for large teams, defining version control strategies, and verification methodologies. For architectural design, it advises breaking the design into subsystems, defining each subsystem's functionality and interfaces. It also discusses collaboration tools, version control, verification approaches, documentation best practices, and considering open source solutions.