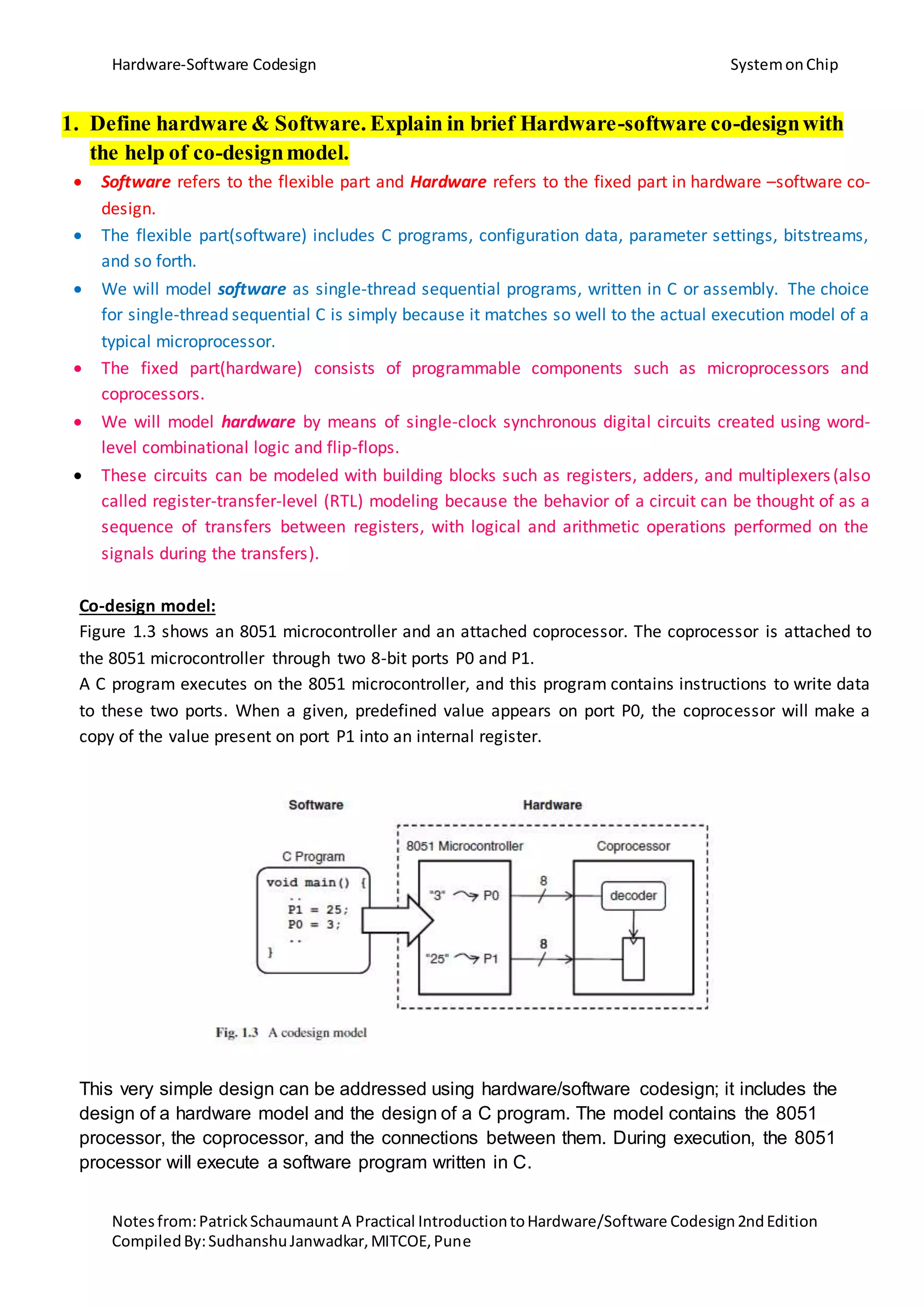

The document is a practical introduction to hardware/software codesign, defining key concepts such as hardware, software, and their integration in a single design effort. It discusses driving factors influencing codesign, including performance, energy efficiency, and design complexity, as well as abstraction levels used in electronic system design. Additionally, it contrasts hardware and software design paradigms, covering aspects of concurrency and parallelism.