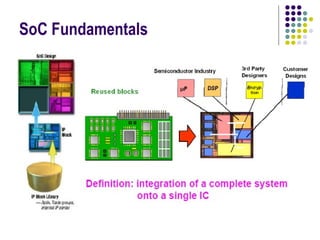

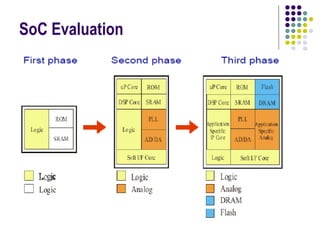

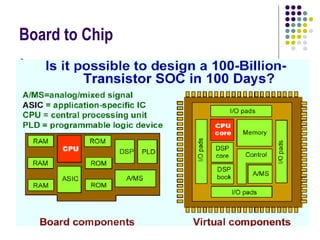

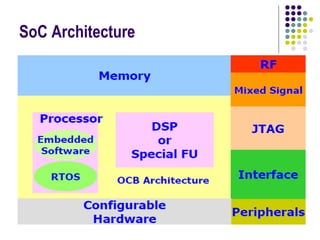

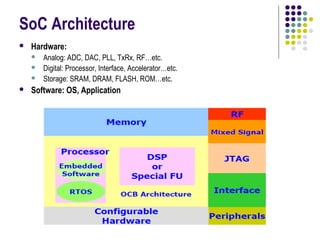

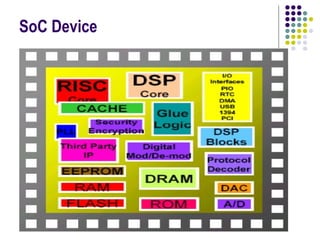

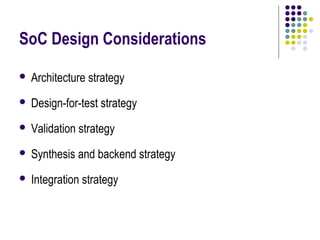

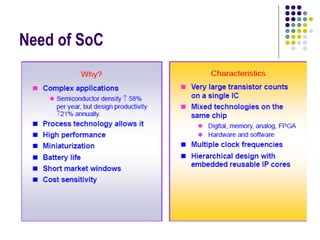

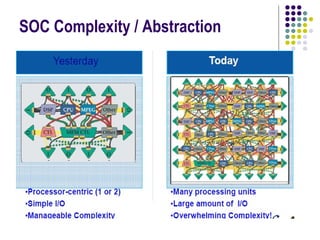

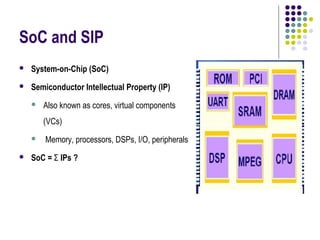

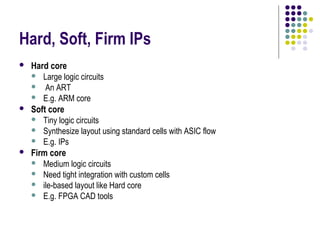

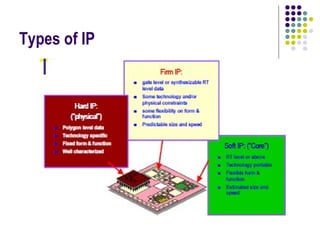

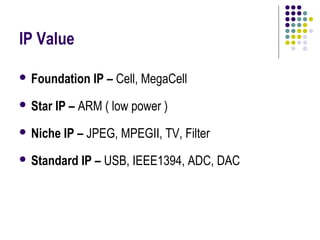

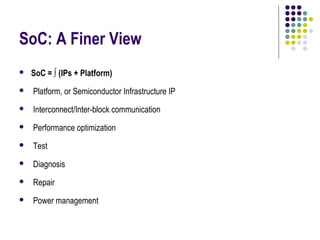

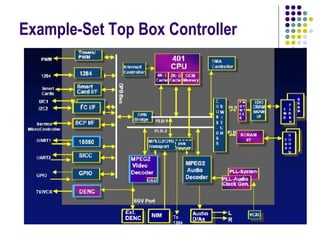

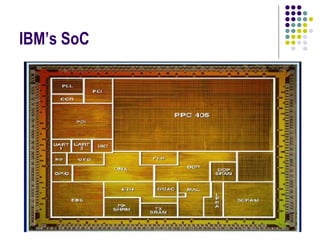

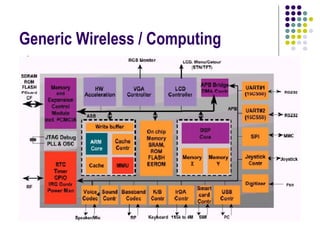

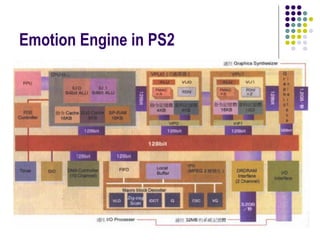

This document provides an overview of system on chip (SoC) design. It discusses that a SoC integrates all components of an electronic system onto a single chip, including digital, analog and radio frequency functions. The SoC design process involves identifying user needs and integrating various intellectual property blocks. It describes the SoC design flow, fundamentals like using soft and hard IP cores, and considerations like architecture strategy and validation. Key aspects covered include SoC architecture, on-chip buses to connect IP cores, and examples of commercial SoCs.