The document provides a comprehensive overview of various System-on-Chip (SoC) bus architectures, including AMBA, PI bus, IBM CoreConnect, ST bus, and others. It details the principles of bus protocols, bus-based design approaches, and specific implementations such as AXI and AHB, highlighting their features and performance characteristics. Additionally, the document discusses the importance of bus arbitration, interoperability, and power management in modern SoC designs.

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Bus protocol

the type and order of data being sent;

how the sending device indicates that it has

finished sending the information;

the data compression method used, if any;

how the receiving device acknowledges

successful reception of the information; and

how arbitration is performed to resolve

contention on the bus and in what priority,

and the type of error checking to be used.

4

[Flynn 2011]](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-4-2048.jpg)

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Bus-based approach

5

[Flynn 2011]

Possible

hierarchy of

buses to optimize

system-level

performance and

cost

Cores or IPs

• Format

conversion

• Segmentation

• Buffering

Address

Data

Control

Power

A bus might

deliver power to

peripherals](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-5-2048.jpg)

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Bus architectures

Unified or split (address and data)

Simple with request acknowledgement

signals

Bus with arbitration support

Tenured split bus (bus is occupied only

during associated address or data cycles)

6

[Flynn 2011]

Memory access time

for the first word](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-6-2048.jpg)

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Bus Architectures

Technology AMBA

AXI

(AMBA 3) CoreConnect

Smart

Interconnect

IP Nexus

Company ARM ARM IBM Sonics Fulcrum**

Core type Soft/hard Soft/hard Soft Soft Hard

Architecture Bus

Unidirectional

channels Bus Bus

NOC using

direct switch

Bus width 8 - 1024 8 - 1024 32/64/128 16 8 - 128

Frequency 200 MHz 400 MHz*

100 - 400

MHz 300 MHz 1 GHz

Maximum

BW (GB/s) 3 6.4* 2.5 - 24 4.8 72

Minimum

latency (ns) 5 2.5* 15 n/a 2

7

[Flynn 2011]

* As implemented in the ARM PL330 high-speed controller.

**Fulcrum was acquired by Intel in 2011](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-7-2048.jpg)

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Advance Microcontroller Bus Architecture (AMBA)

Develped by ARM in 1996

Distinct busses in AMBA specification:

1. Advanced High performance Bus (AHB)

2. Advanced Peripheral Bus (APB)

3. [Advanced System Bus (ASB) – designed for

lower performance systems, outdated]

AXI - Advanced

Extensible

Interface

(since AMBA 3)

[Flynn 2011]

ARM](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-9-2048.jpg)

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Zync-7000 AP SoC interfaces and signals

19

[Crockett, Zync book 2014, p192]

GP – General Purpose

HP – High Performance

ACP – 64-bit

Accelerator Coherency

Port for asynchronous

cache-coherent access](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-19-2048.jpg)

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Zync-7000

Zynq-7000 devices

are equipped with

dual-core ARM

Cortex-A9

processors

integrated with

28nm Artix-7 or

Kintex®-7 based

programmable

logic

[Xilinx Web]

20](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-20-2048.jpg)

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Zynq-7000 AP SoC

21

[Zynq-7000 All

Programmable SoC

Technical Reference

Manual UG585

(v1.11) September

27, 2016]](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-21-2048.jpg)

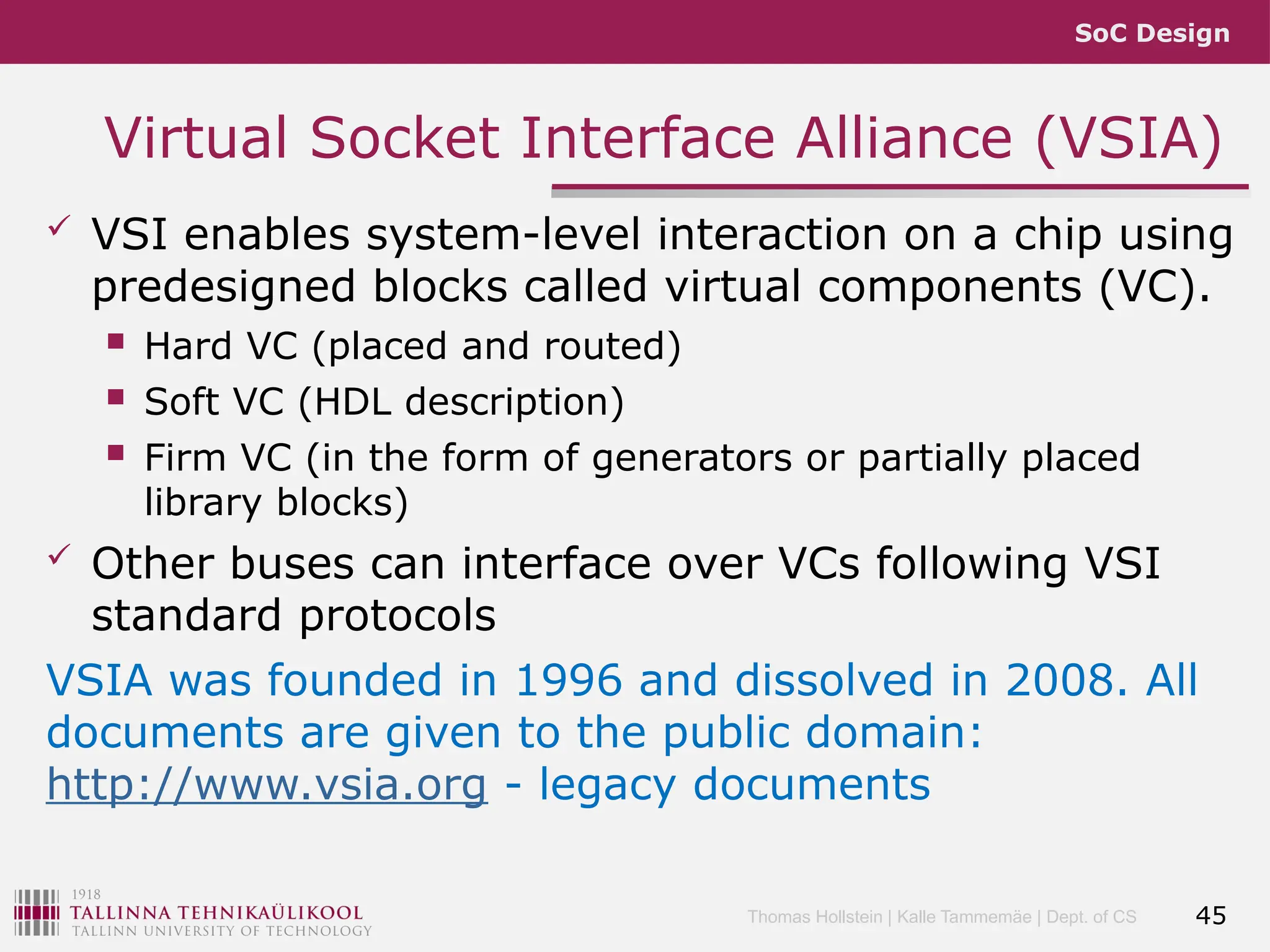

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Multiple request multiple data possible

Reduced chip area by configuring into the OCP interfaces only those

features needed by the communicating cores.

Simplified system verification and testing by providing built-in test

mechanisms

Protocols for cache coherence

Open Core Protocol International Partnership (OCP-IP)

Source: Prashant D.

Karandikar, Texas

Instruments Inc

[OCP Specification3.0]](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-43-2048.jpg)

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Avalon Multi-Mastering

47

Example multi master system

that permits bus transfers

between two masters and two

slaves

[Simultaneous Multi-Mastering

with the Avalon Bus, Application

note 184, Altera 2002]

Avalon Bus Control Signals:

• Master Request Slave (MRS)

• Master Select Granted (MSG)

• Wait](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-47-2048.jpg)

![SoC Design

Thomas Hollstein | Kalle Tammemäe | Dept. of CS

Summary

48

[https://en.wikipedia.org/wiki/Bus_(computing)]

PC Express

x 4

x 16

x 1

x 16

Conventional

32-bit PCI](https://image.slidesharecdn.com/16258031-240829100739-5ecb0e55/75/Commercial-and-Open-SoC-buses_AMBA_OCP-ppt-48-2048.jpg)