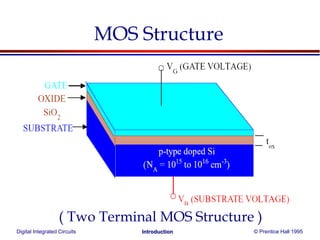

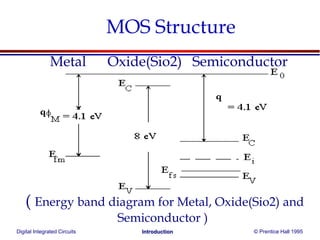

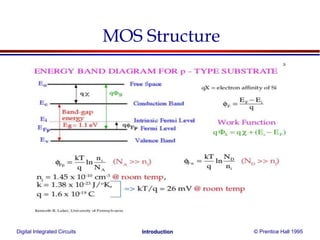

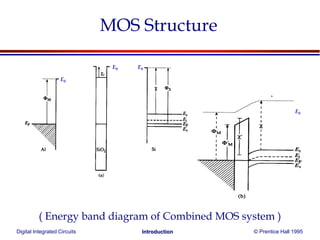

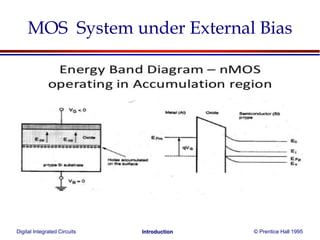

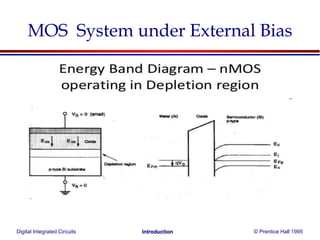

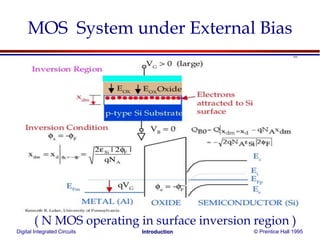

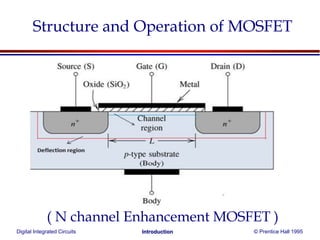

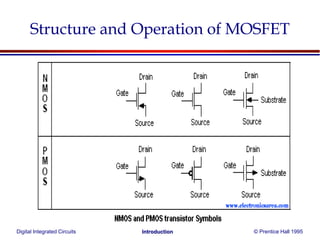

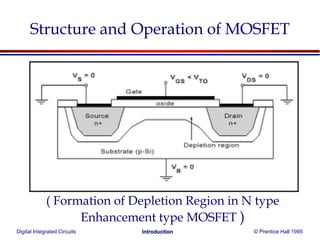

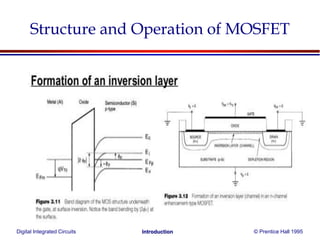

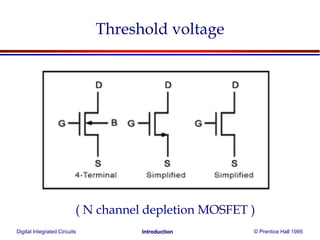

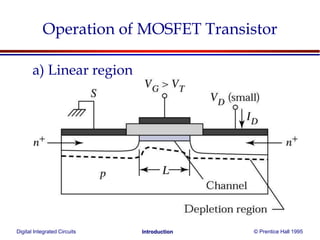

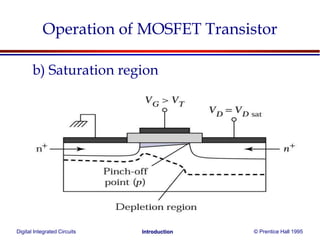

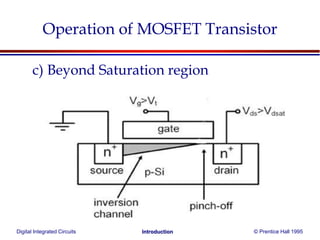

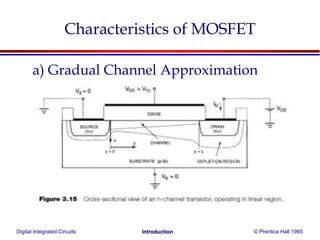

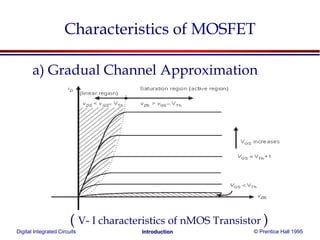

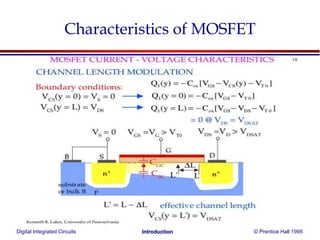

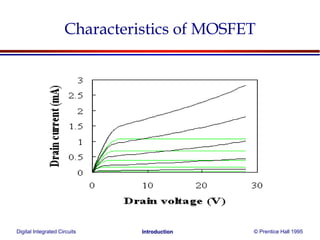

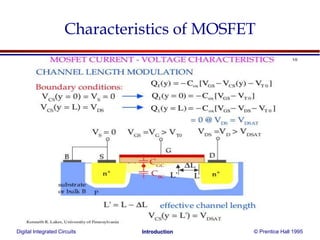

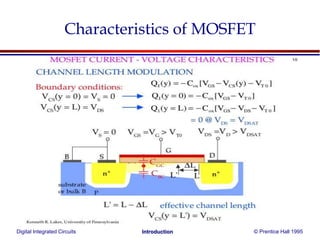

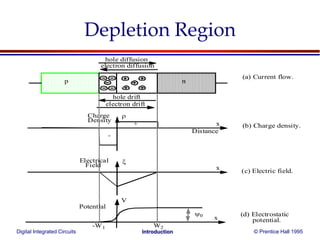

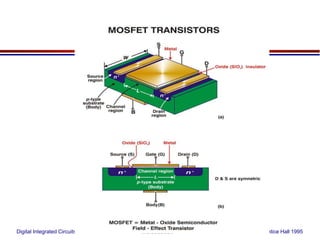

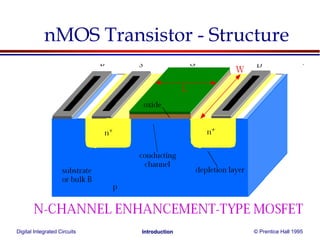

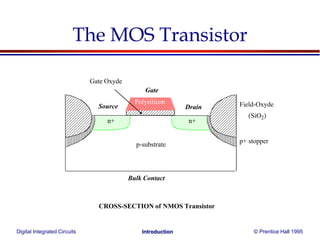

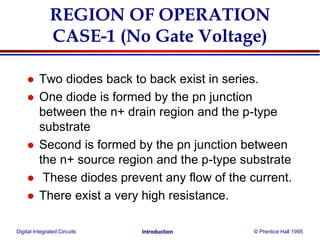

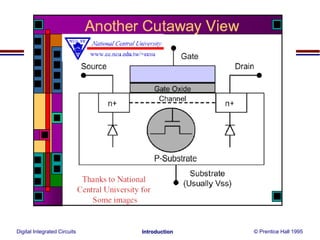

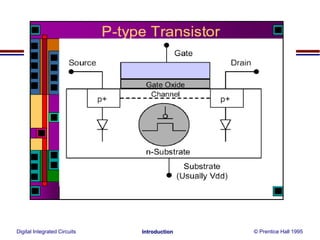

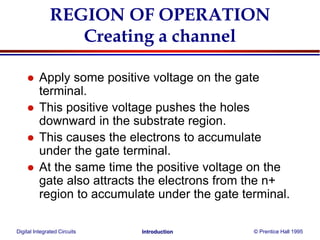

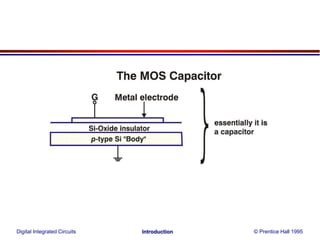

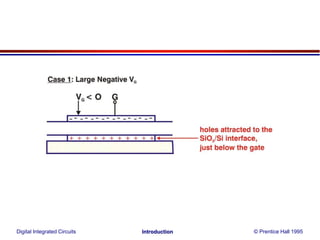

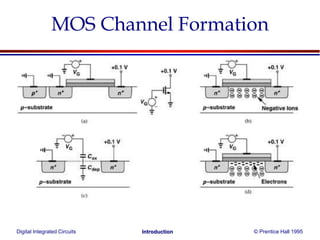

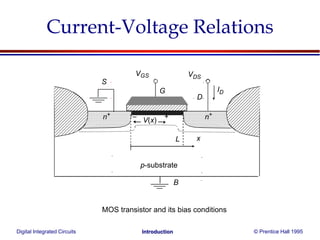

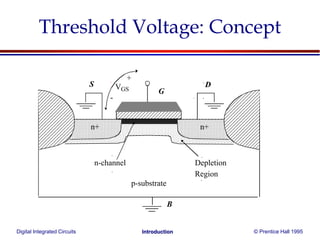

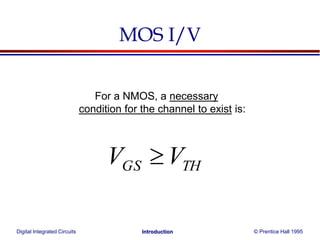

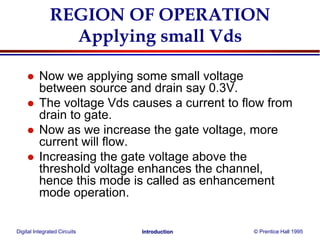

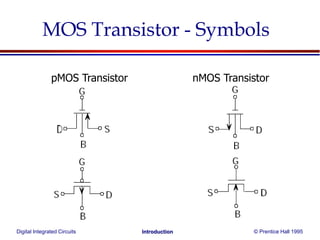

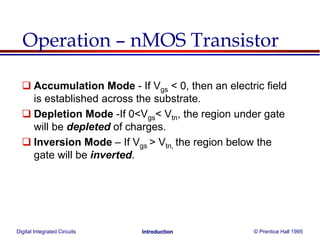

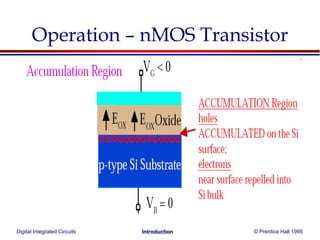

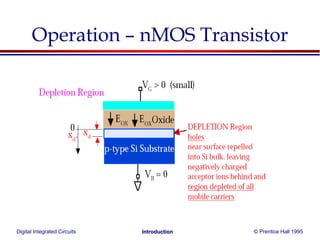

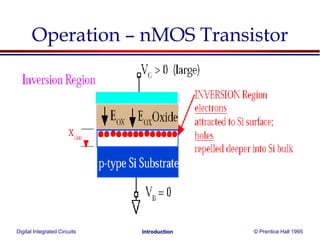

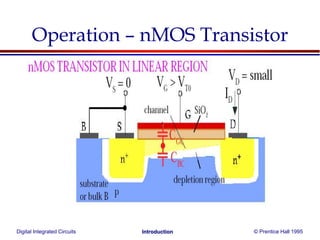

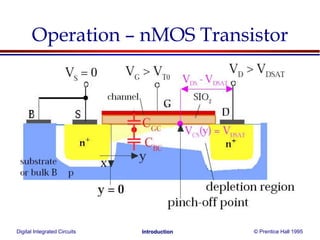

The document discusses MOS transistors and their operation. It introduces MOS structure, showing the metal-oxide-semiconductor makeup. It describes how applying a positive voltage to the gate can create an inversion layer channel between the source and drain, allowing current to flow. The threshold voltage is defined as the minimum gate voltage needed to form an conducting channel. The document covers MOS transistor regions of operation like accumulation, depletion and inversion modes in detail. It also discusses key characteristics like current-voltage relationships.