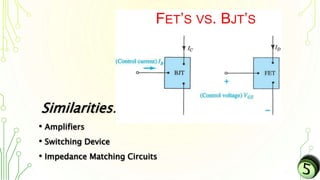

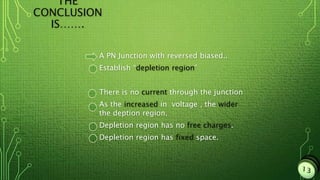

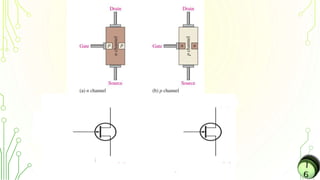

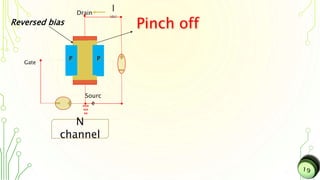

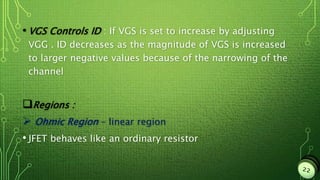

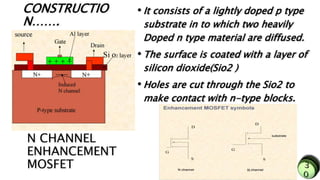

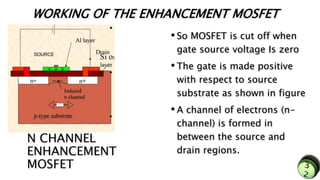

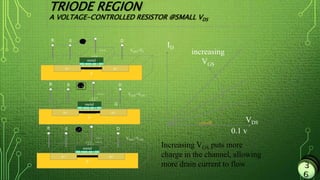

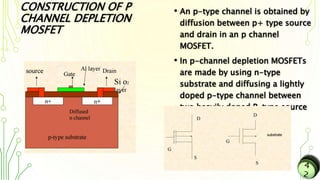

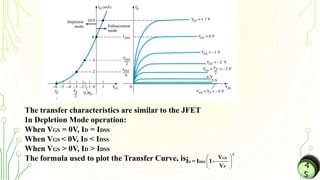

The document summarizes different types of field-effect transistors (FETs). It describes the invention of the transistor in 1947 and its impact. It then discusses the basic principles and constructions of junction FETs (JFETs), metal-oxide-semiconductor FETs (MOSFETs) including n-channel and p-channel enhancement and depletion mode MOSFETs. Key differences between FETs, BJTs, and operating characteristics such as different regions of operation are also summarized. The document provides a high-level overview of various FET technologies.