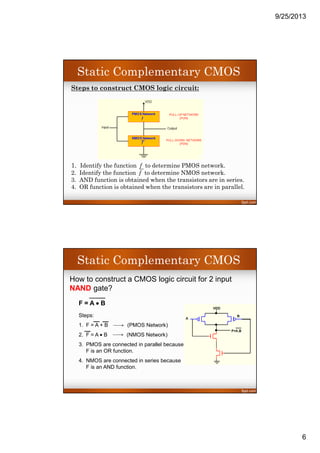

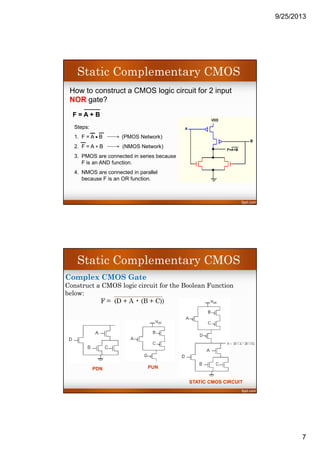

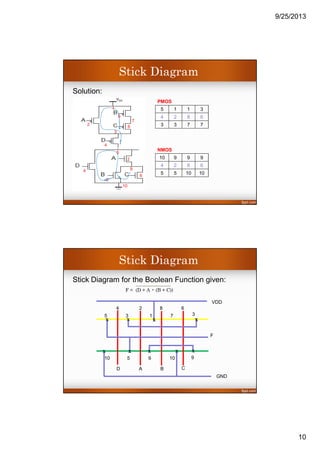

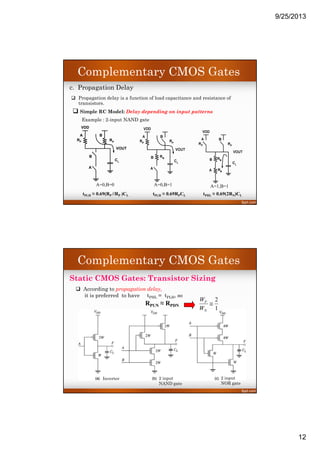

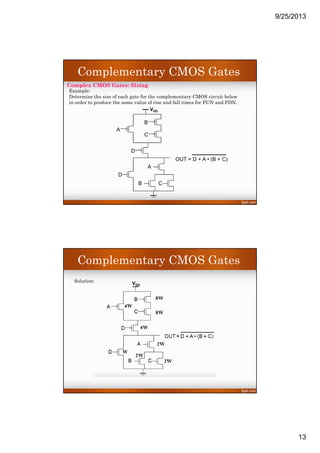

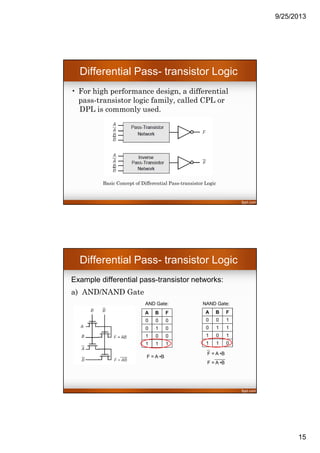

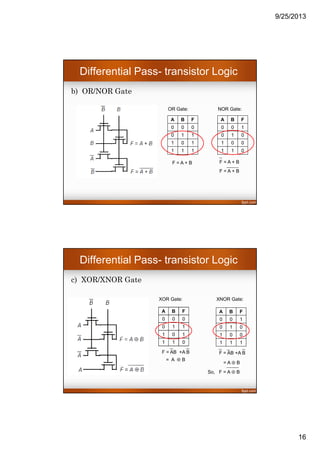

This document discusses designing combinational logic circuits using static complementary CMOS design. It explains how to construct static CMOS circuits for logic gates like NAND and NOR by using pull-up and pull-down networks of PMOS and NMOS transistors respectively. Issues related to pass-transistor design like noise margins and static power consumption are also covered. The document provides details on implementing various logic functions using pass-transistor logic and differential pass-transistor logic. It discusses solutions to overcome the disadvantages of pass-transistor logic like level restoration and use of multiple threshold transistors.