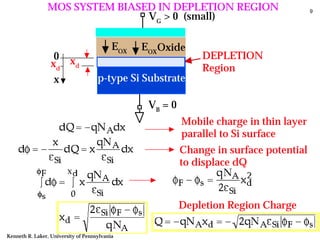

This document discusses MOS transistor theory and provides examples for calculating threshold voltage (VT).

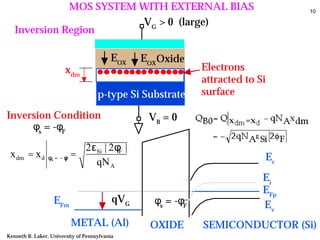

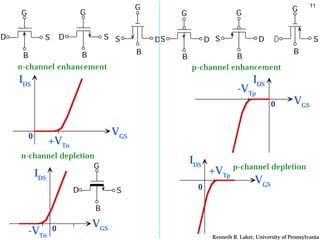

[1] It describes the basic structure of an n-channel MOSFET and the energy band diagrams for different biasing conditions, including accumulation, depletion, and inversion.

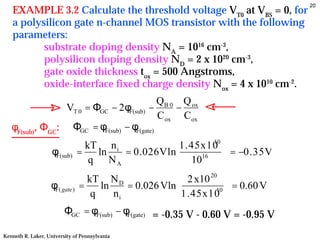

[2] Threshold voltage depends on factors like gate material, oxide thickness, channel doping, and interface charges. An example calculates VT0 = 0.38V for an nMOS transistor with given parameters.

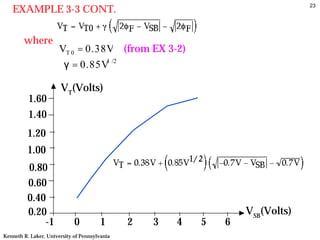

[3] Body effect is explained, where threshold voltage increases with reverse substrate bias. An example plots VT as a function of VSB, using the body effect coefficient γ = 0.85V1/2 calculated for the

![MOS Capacitance C = WLC , C = ε ox 15

[tox -> TOX in SPICE]

GC ox ox

t ox

[Cox -> COX in SPICE]

tox = 50 nm, εox = 0.34 pF/cm => Cox = 6.8 x 10-8 F/cm2

W x L = 50 µm x 50 µm => CGC = 170 fF

Depletion Capacitance C BC = WLC j , C j = εSi

xd

[NSUB -> NSUB in SPICE]

NSUB (p - substrate)

kT n i

ln φFp =

q NA

NA = 3 x 1017 cm-3, ni = 1.45 x 1010 cm-3 => φF = -0.438 V

(recall that at room temp or 27oC kT/q = 26 mV)

VSB = 0 V, εSi = 1.06 pF/cm, q = 1.6 x 10-19 C, NA, φF => xd = 6.22 µm

εSi, xd => Cj = 0.17 x 10-8 F/cm2

W x L = 50 µm x 50 µm => CBC = 42.5 fF

Kenneth R. Laker, University of Pennsylvania](https://image.slidesharecdn.com/ee560mostheoryp101-130309152641-phpapp02/85/Ee560-mos-theory_p101-14-320.jpg)

![16

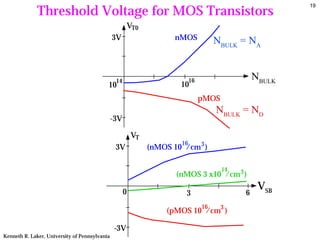

Threshold Voltage for MOS Transistors

n-channel enhancement

For VSB = 0, the threshold voltage is denoted as VT0 or VT0n,p T0 -> VT0 in SPICE]

[V

QB 0 Q ox

VT 0 = ΦGC − 2φF − −

C ox C ox

Threshold Voltage factors: (+ for nMOS and - for pMOS)

[2φ F = PHI in SPICE]

-> Gate conductor material;

-> Gate oxide material & [N A = NSUB in SPICE]

thickness;

-> Channel doping;

-> Impurities in Si-oxide

interface;

ΦGC = φF(substrate) -φM metal gate

ΦGC = φF(substrate) -φF (gate) polysilicon gate

-> Source-bulk voltage Vsb;

-> Temperature. [Qox = qNSS in SPICE]

Kenneth R. Laker, University of Pennsylvania](https://image.slidesharecdn.com/ee560mostheoryp101-130309152641-phpapp02/85/Ee560-mos-theory_p101-15-320.jpg)

![17

Threshold Voltage for MOS Transistors

n-channel enhancement

For : the threshold voltage is denoted as VT or VTn,p

QB Q ox

VT = ΦGC − 2φF − −

C ox C ox

Q B 0 Q ox Q B − Q B0

= ΦGC − 2φF − − −

C ox C ox C ox

where VT0

(γ = Body-effect coefficient) [γ = GAMMA in SPICE]

+

Kenneth R. Laker, University of Pennsylvania](https://image.slidesharecdn.com/ee560mostheoryp101-130309152641-phpapp02/85/Ee560-mos-theory_p101-16-320.jpg)