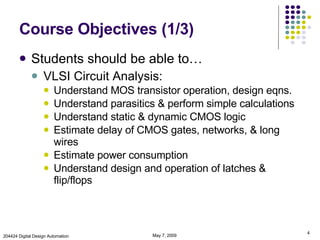

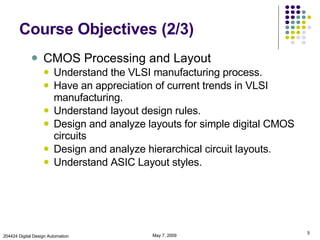

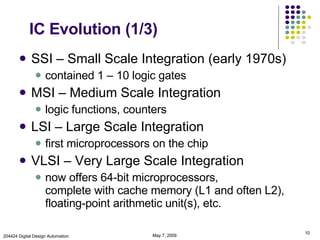

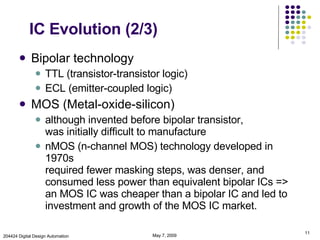

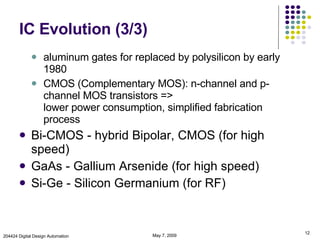

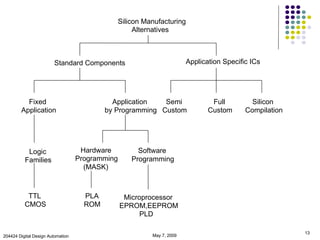

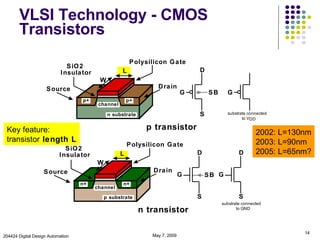

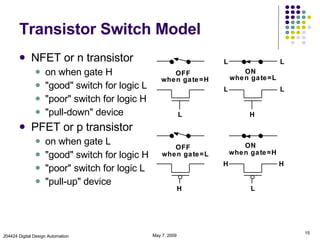

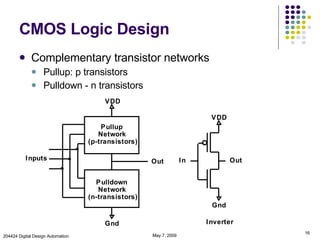

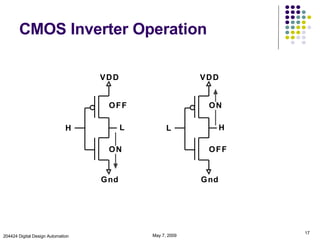

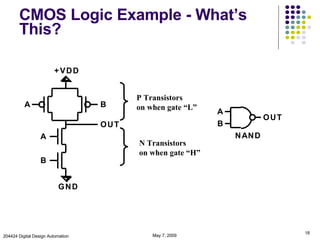

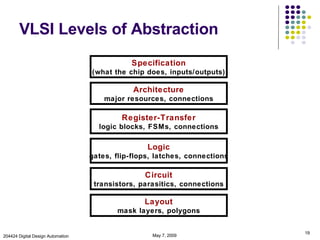

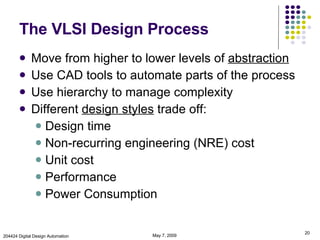

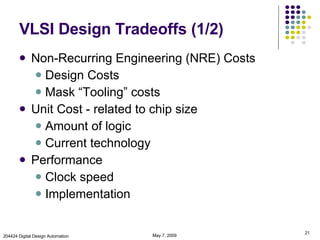

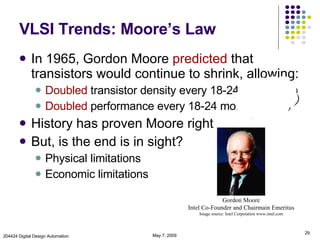

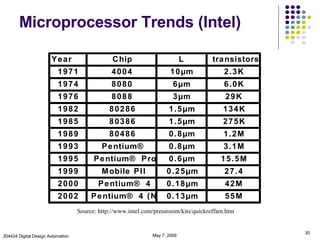

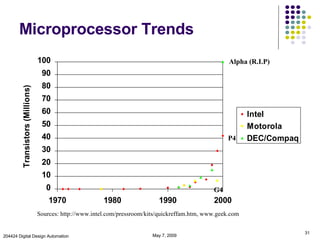

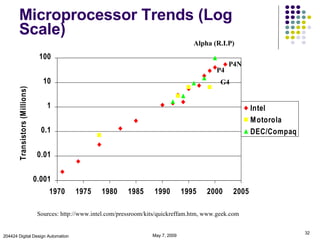

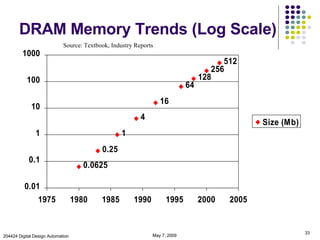

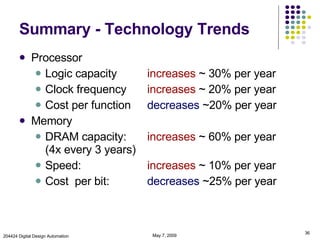

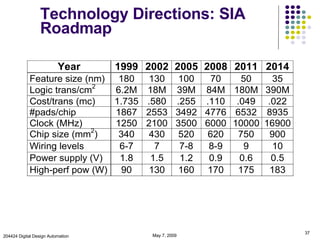

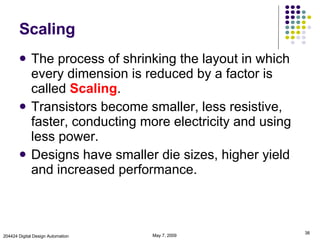

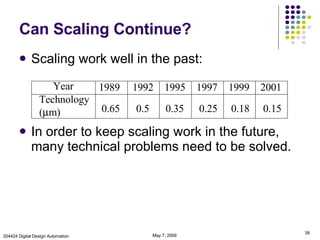

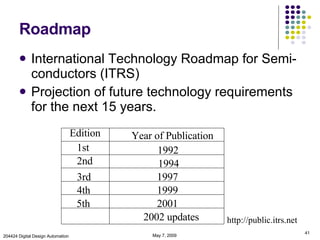

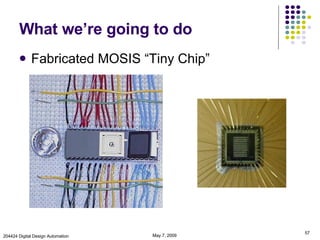

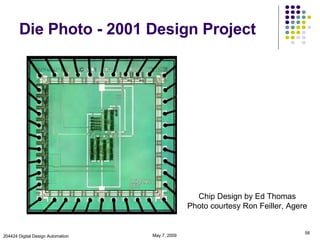

This document provides an overview of VLSI design for a course. It discusses topics including CMOS transistors and logic gates, VLSI levels of abstraction, the VLSI design process, design styles like full custom and ASIC, and trends like Moore's Law. The roadmap outlines topics to be covered like CMOS processing, combinational and sequential circuit design, and a design project to complete a chip. Course objectives are listed relating to VLSI analysis, layout design, and system design skills.

![Lecture 1 Introduction to VLSI Design Pradondet Nilagupta [email_address] Department of Computer Engineering Kasetsart University](https://image.slidesharecdn.com/lecture-vlsi-090507042309-phpapp01/85/Introduction-to-VLSI-1-320.jpg)