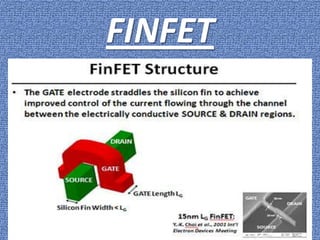

FINFET is a type of non-planar transistor with a conducting channel that is wrapped by a thin silicon fin. It was developed to overcome short channel effects seen in planar MOSFETs as transistors continue to shrink. Key aspects of FINFETs include the fin structure which allows gate control of the channel from both sides and the top, reducing leakage currents. Fabrication involves depositing fins and wrapping a gate material around them. FINFETs have been shown to effectively suppress short channel effects even at very small gate lengths, but come with increased manufacturing complexity and potential reliability issues compared to planar transistors.