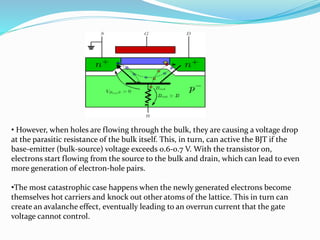

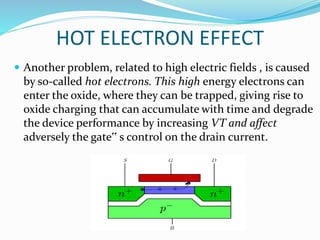

This document discusses short channel effects that occur in MOSFET devices when the channel length decreases to the same order of magnitude as the source/drain junction depth. It describes five main short channel effects: drain induced barrier lowering, drain punch through, velocity saturation, impact ionization, and hot electron effects. For each effect, it provides an explanation of the physical phenomenon and how it impacts device performance as the channel length decreases. It concludes by listing three references for further reading on leakage current mechanisms and MOSFET modeling.

![REFERENCES

[1] Kaushi Roy, Saibal Mukhopadhyay and Hamid

Mahmoodi-Meimand, "Leakage current mechanisms

and leakage reduction techniques in deep-

submicrometer CMOS circuits", Proceedings of the

IEEE, 305-327, vol. 91, no.2, February 2003.

[2].Sung-Mo Kang and Yusuf Leblebici, Cmos Digital

Integrated Circuits, Tata McGraw-Hill Education,

2003.

[3]. Narain Arora, Mosfet Modeling for VLSI Simulation:

Theory and Practice, WORLD SCIENTIFIC, 2007](https://image.slidesharecdn.com/shortchanneleffects-180919050414/85/Short-channel-effects-11-320.jpg)