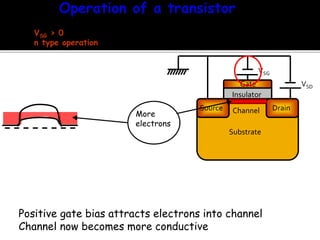

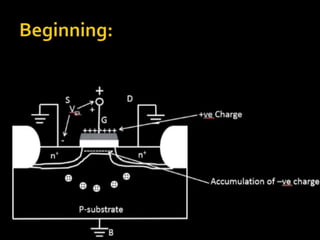

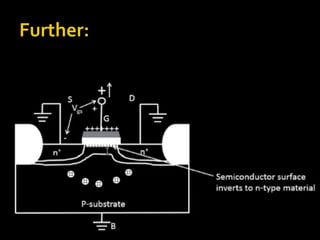

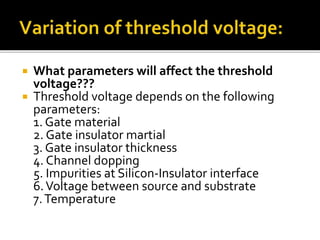

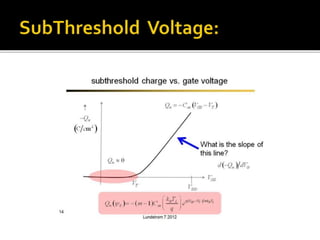

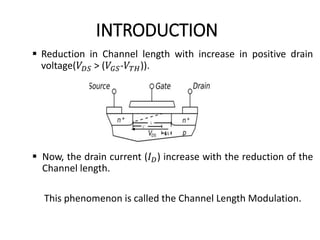

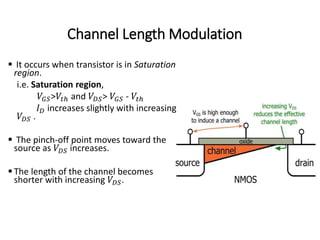

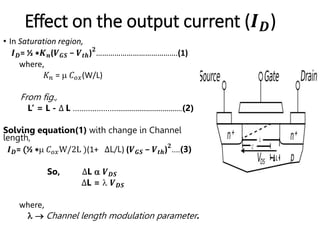

The document discusses threshold voltage and channel length modulation in transistors, outlining factors affecting threshold voltage such as gate material and impurities. It describes channel length modulation as a phenomenon where channel length reduces with increasing drain voltage, leading to increased drain current in the saturation region. Key equations and parameters related to these concepts are also presented.

![REFERENCES:

[1] http://www.onmyphd.com/print.php?p=channel.length.modulation

[2] Modern VLSI Design-by Yuan Taur and Tak H. Ning

[3] https://ecee.colorado.edu/~bart/book/book/chapter7/ch7_3

[4] https://www.researchgate.net/post/

[5] http://nptel.ac.in/courses/117103063/17](https://image.slidesharecdn.com/dtednew-171117180707/85/Threshold-Voltage-Channel-Length-Modulation-14-320.jpg)