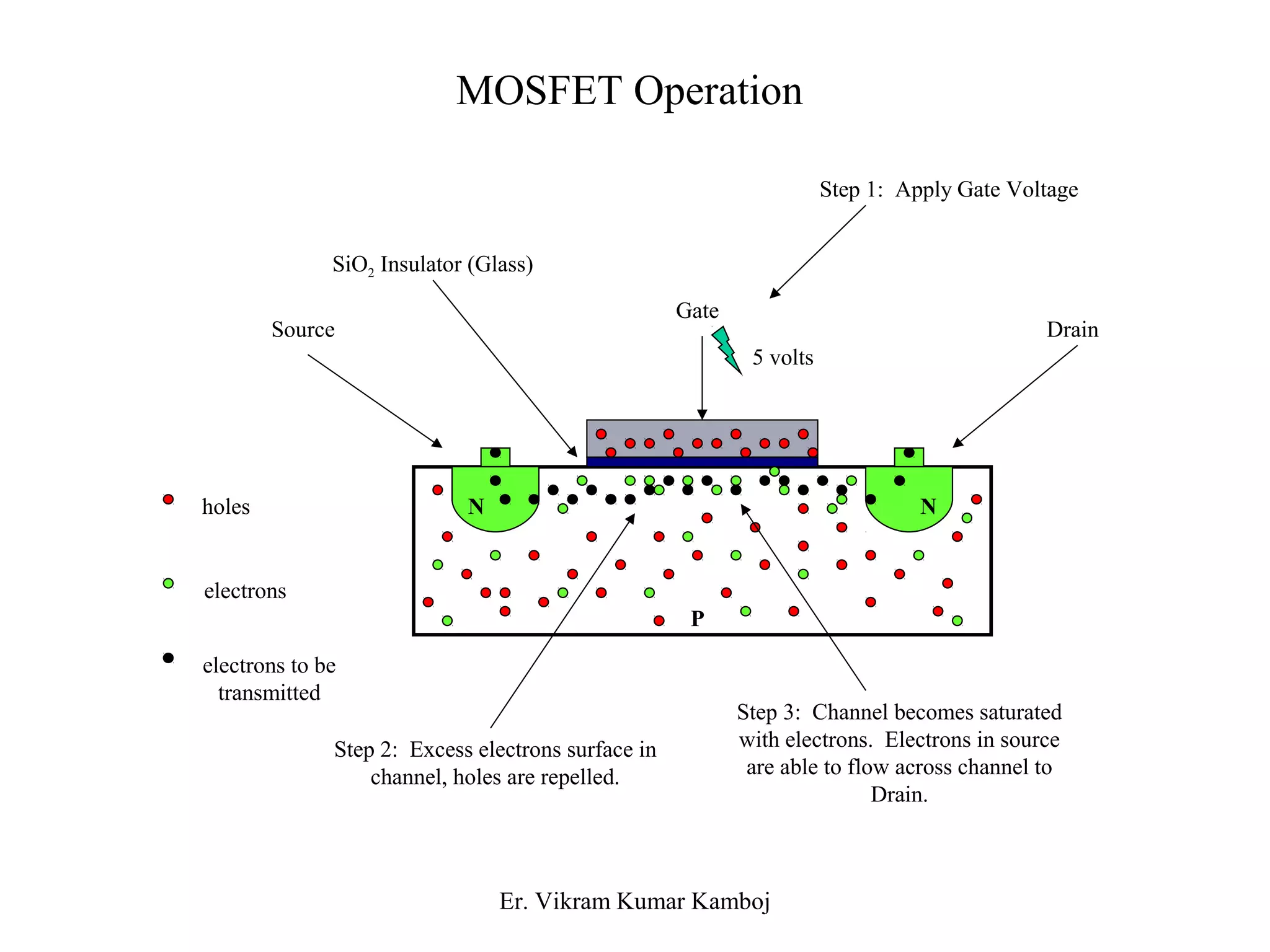

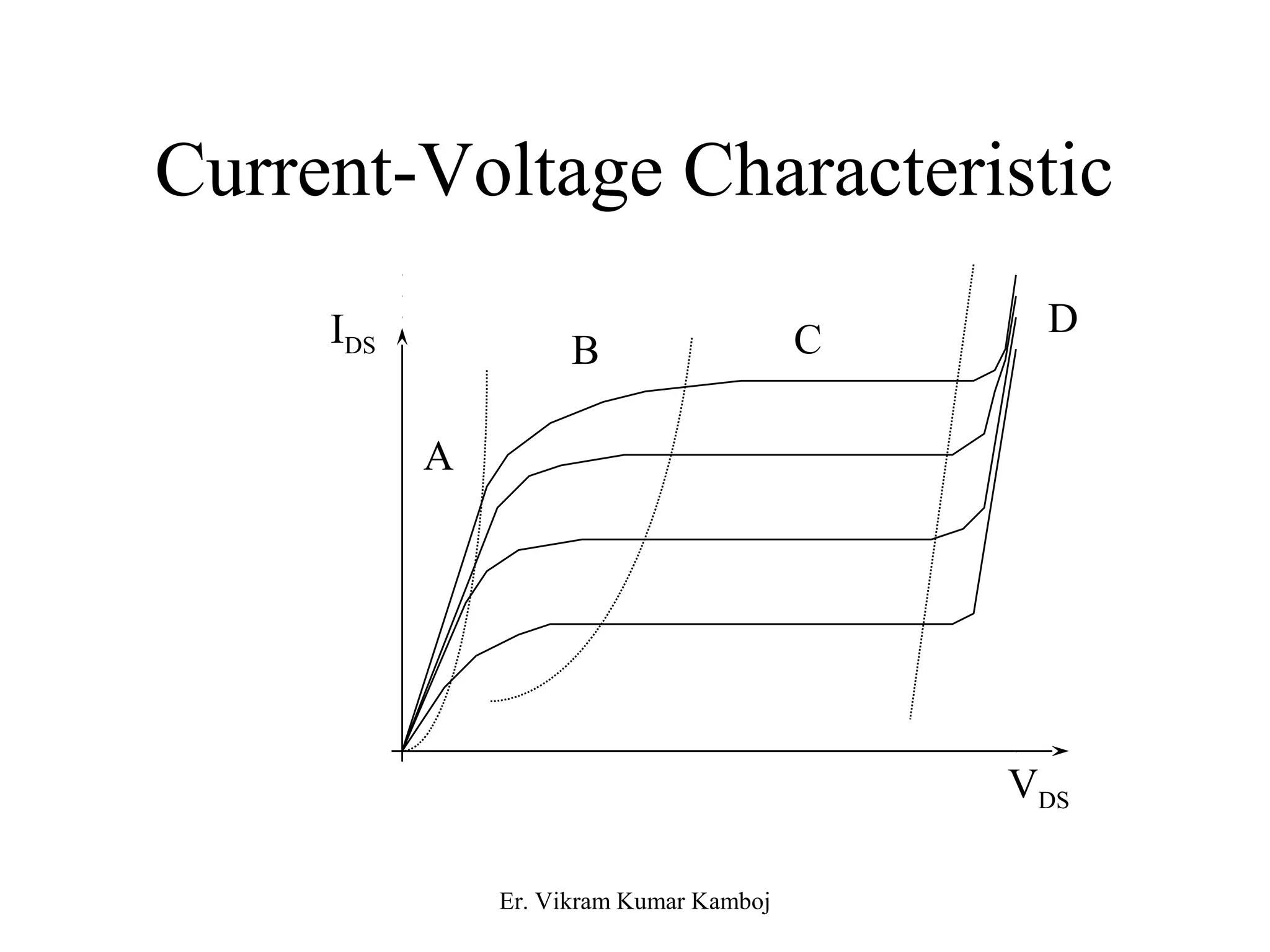

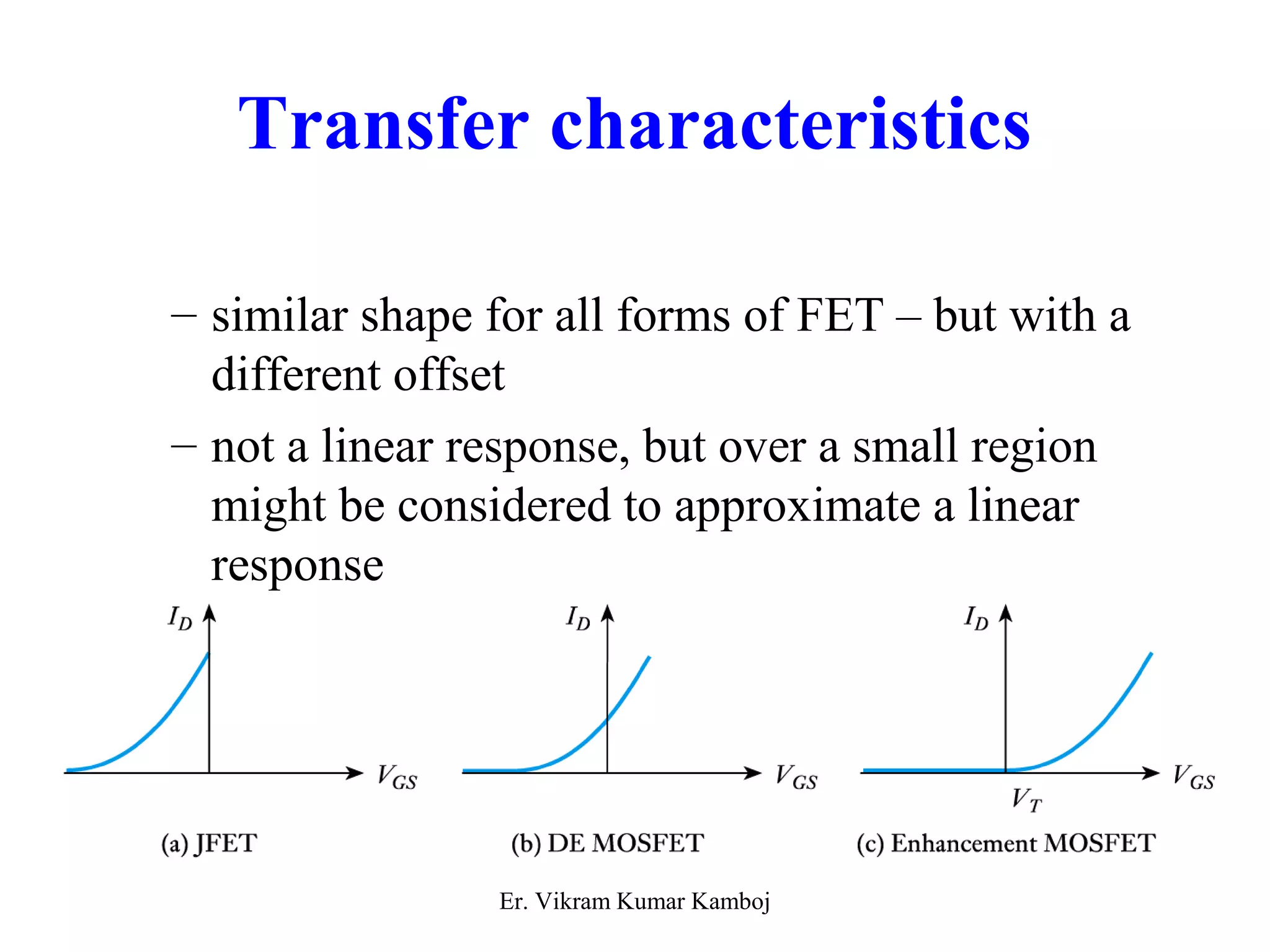

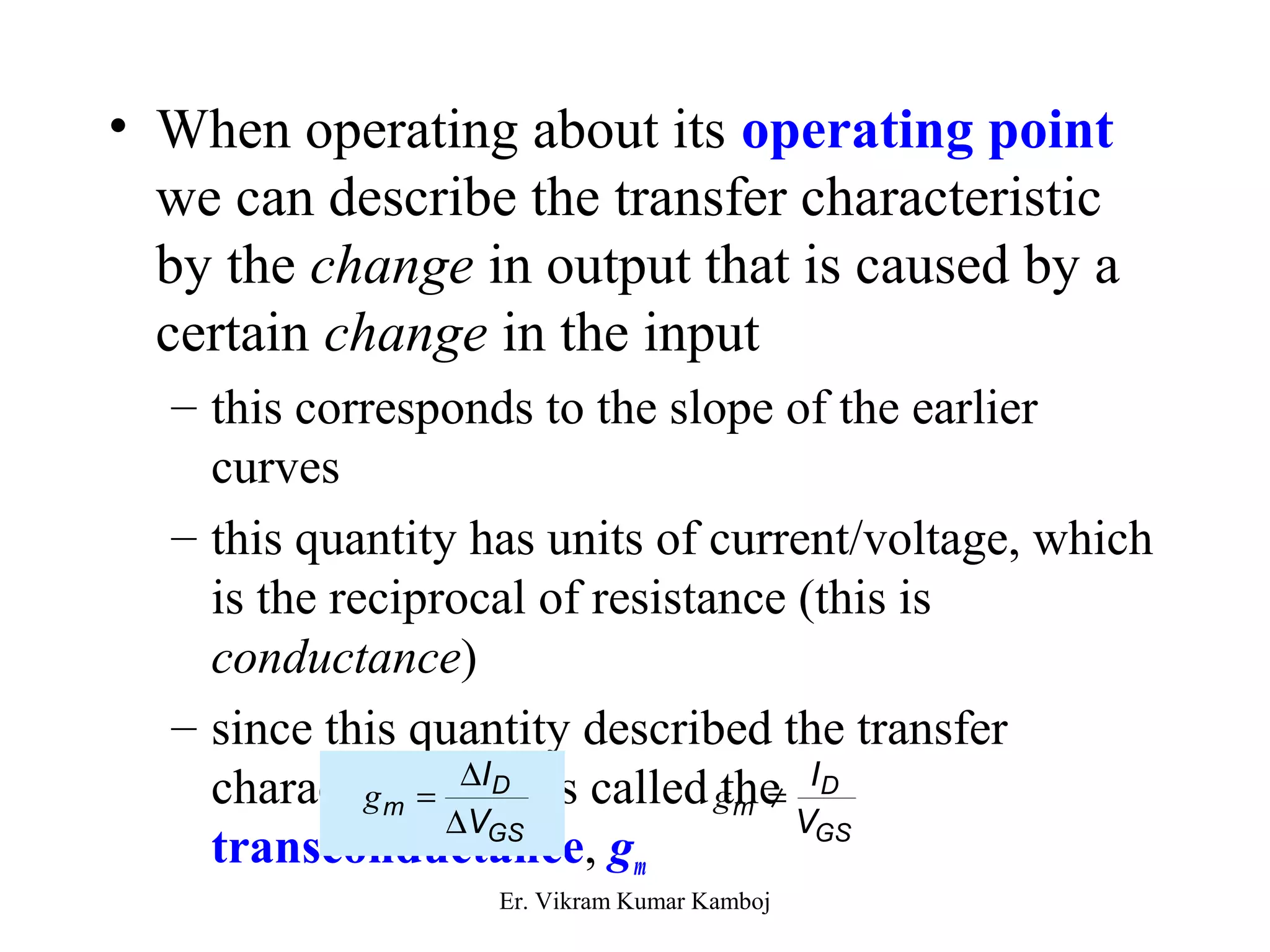

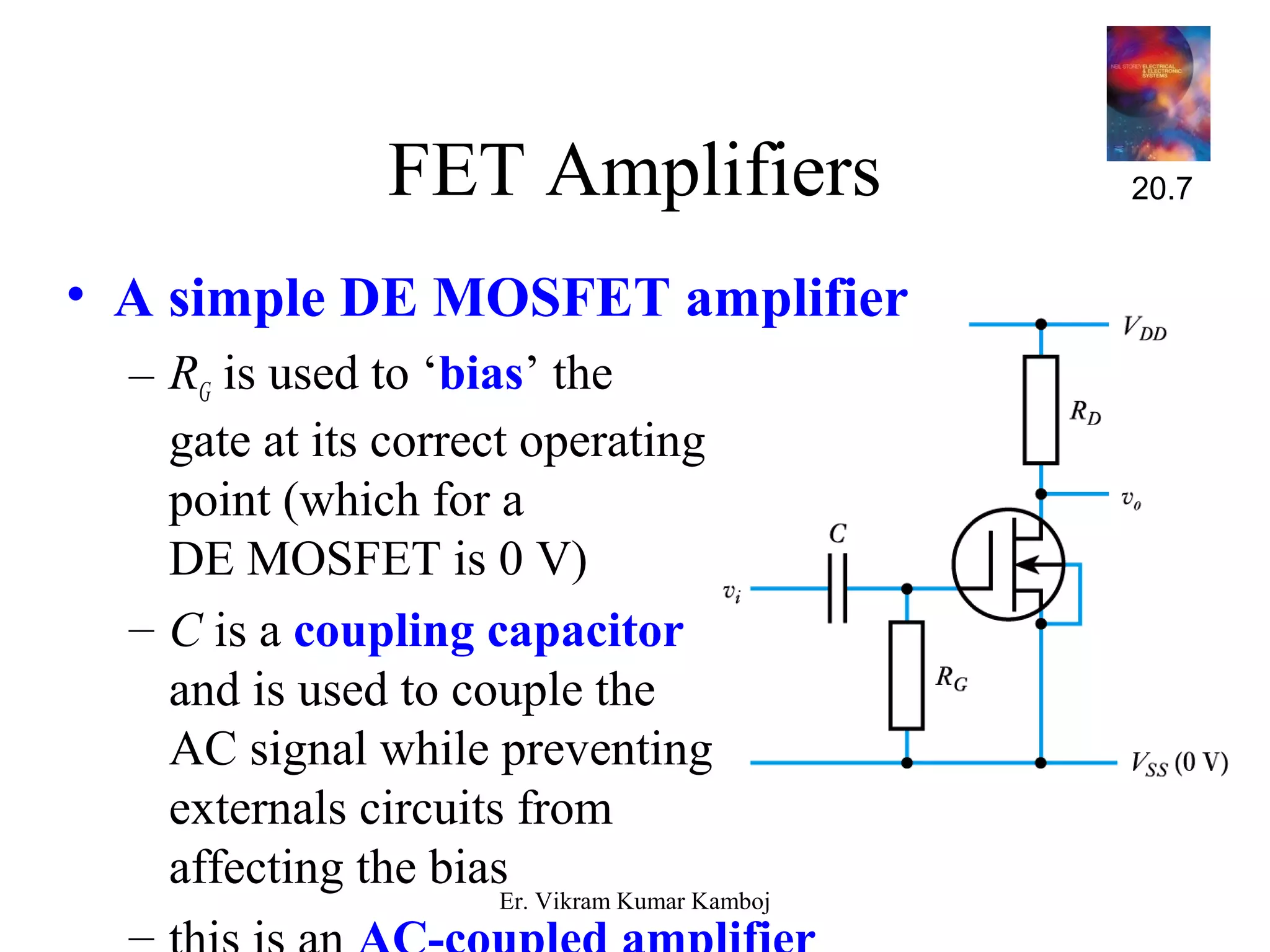

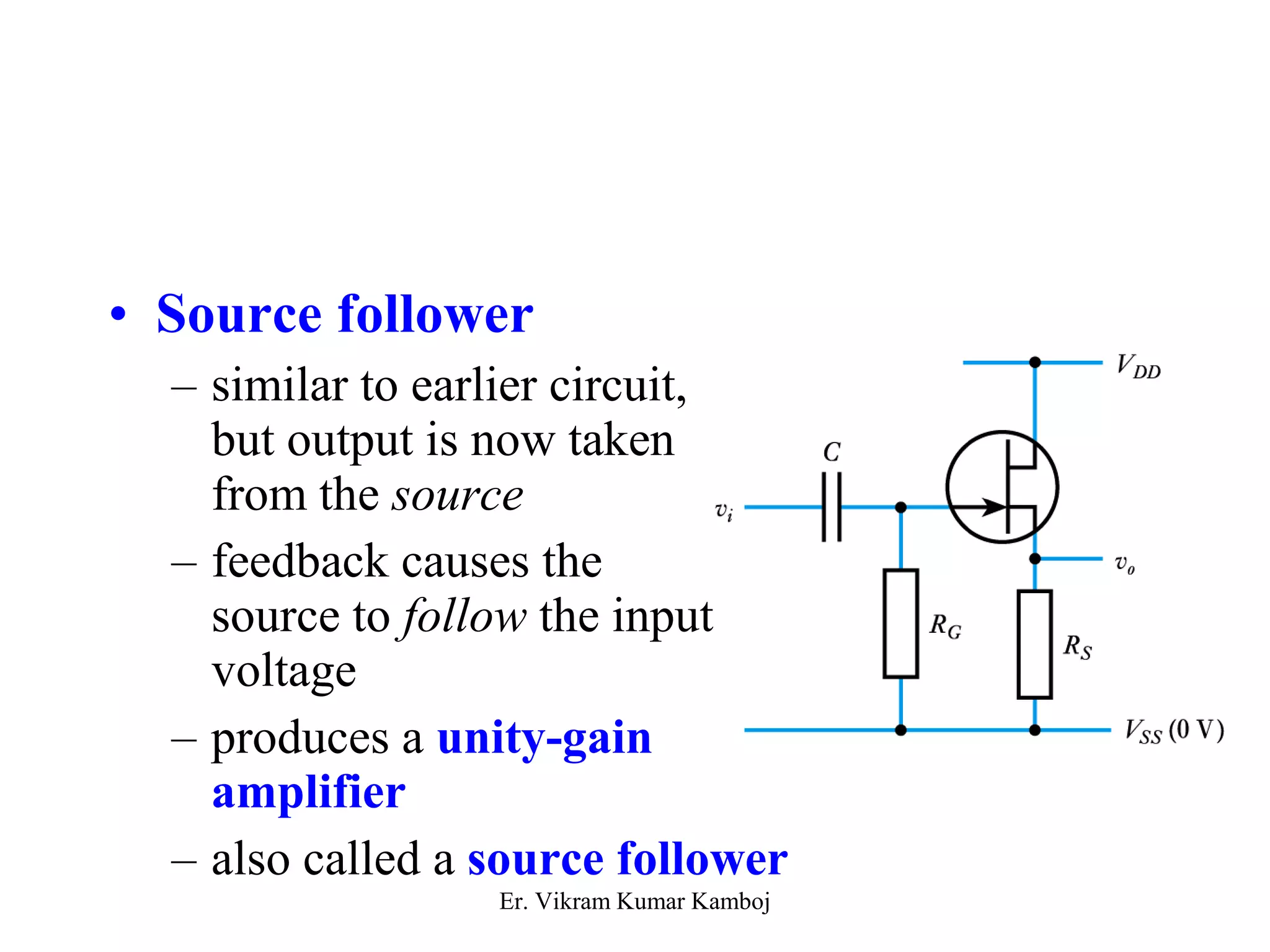

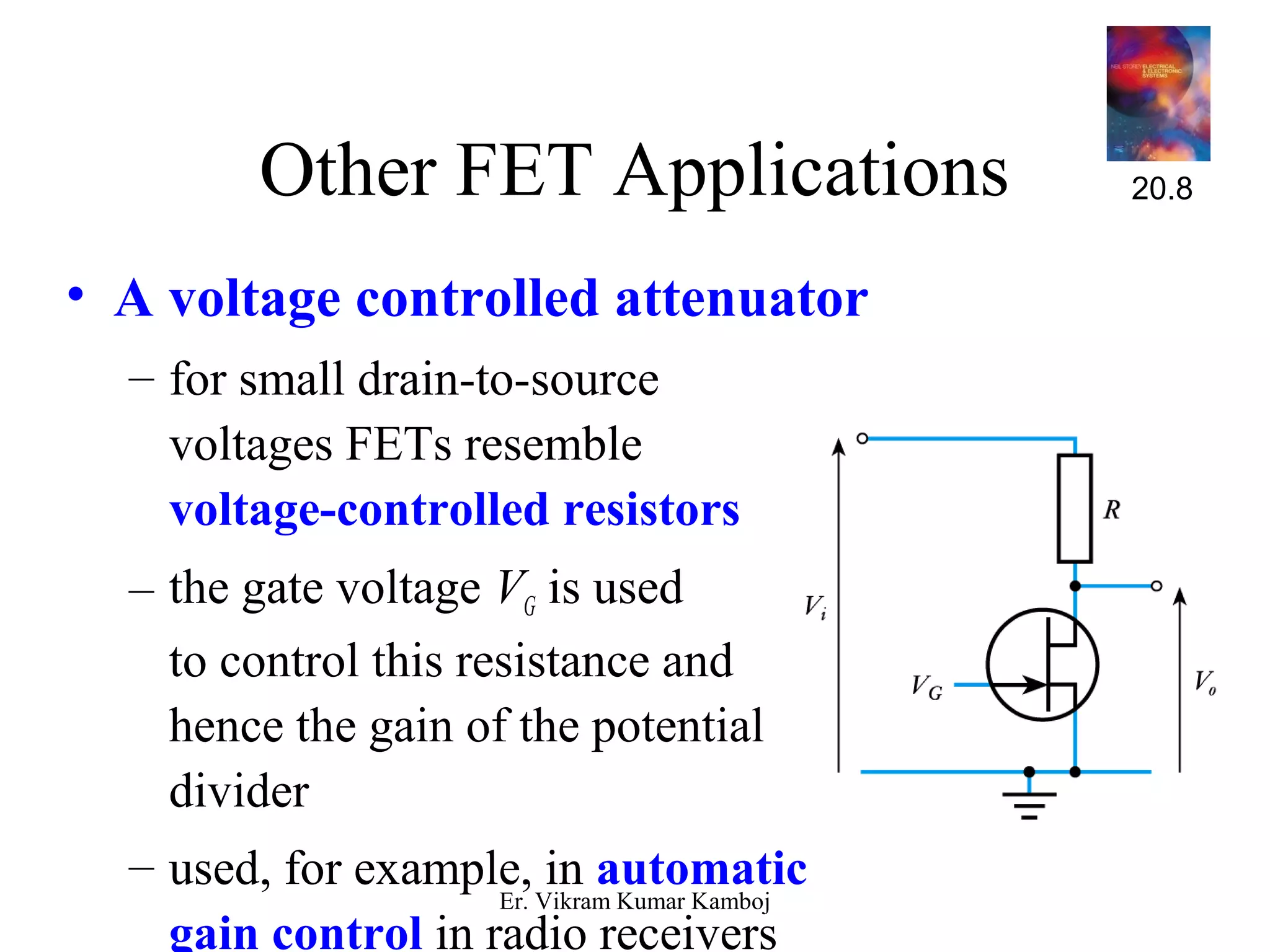

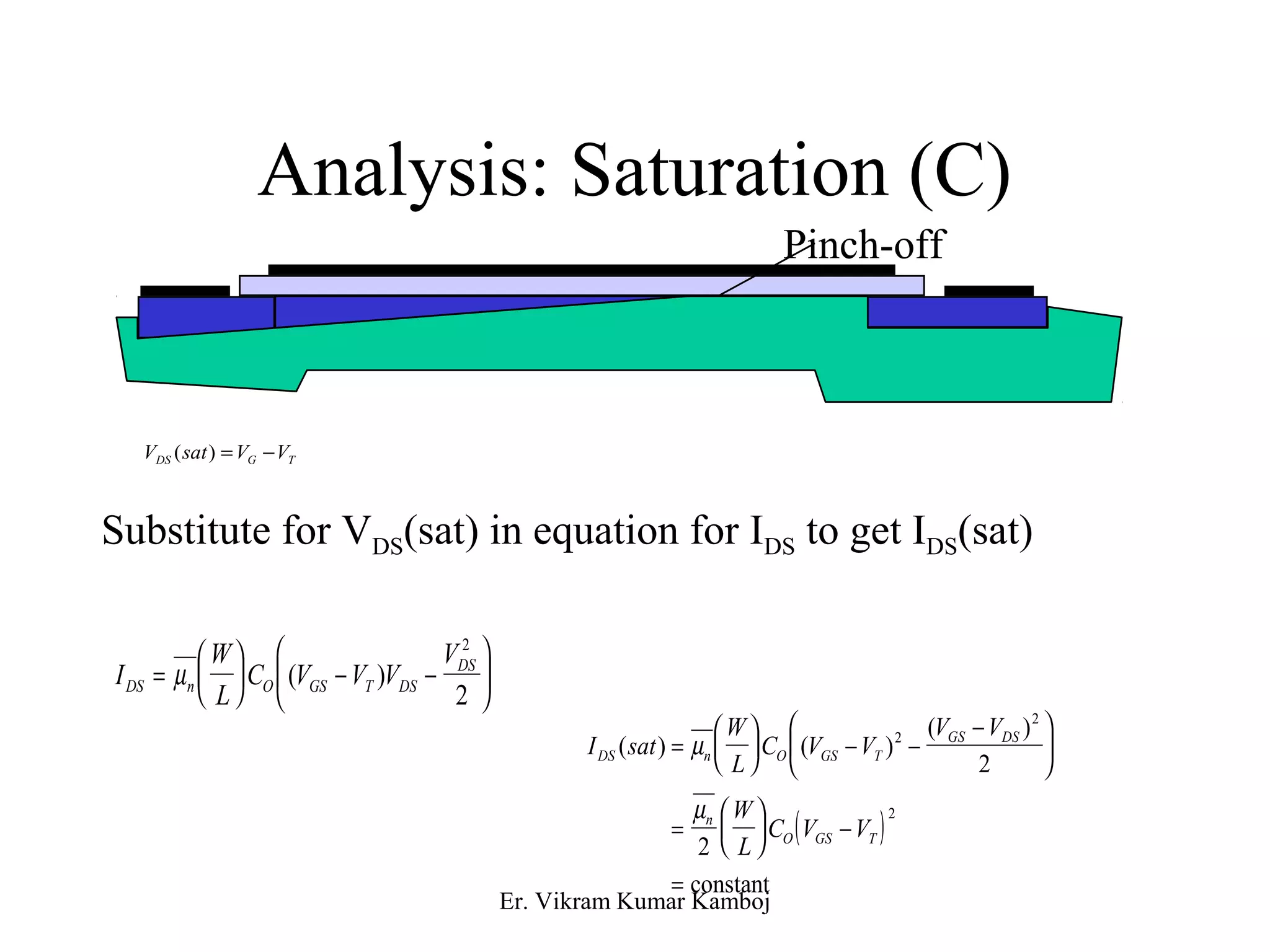

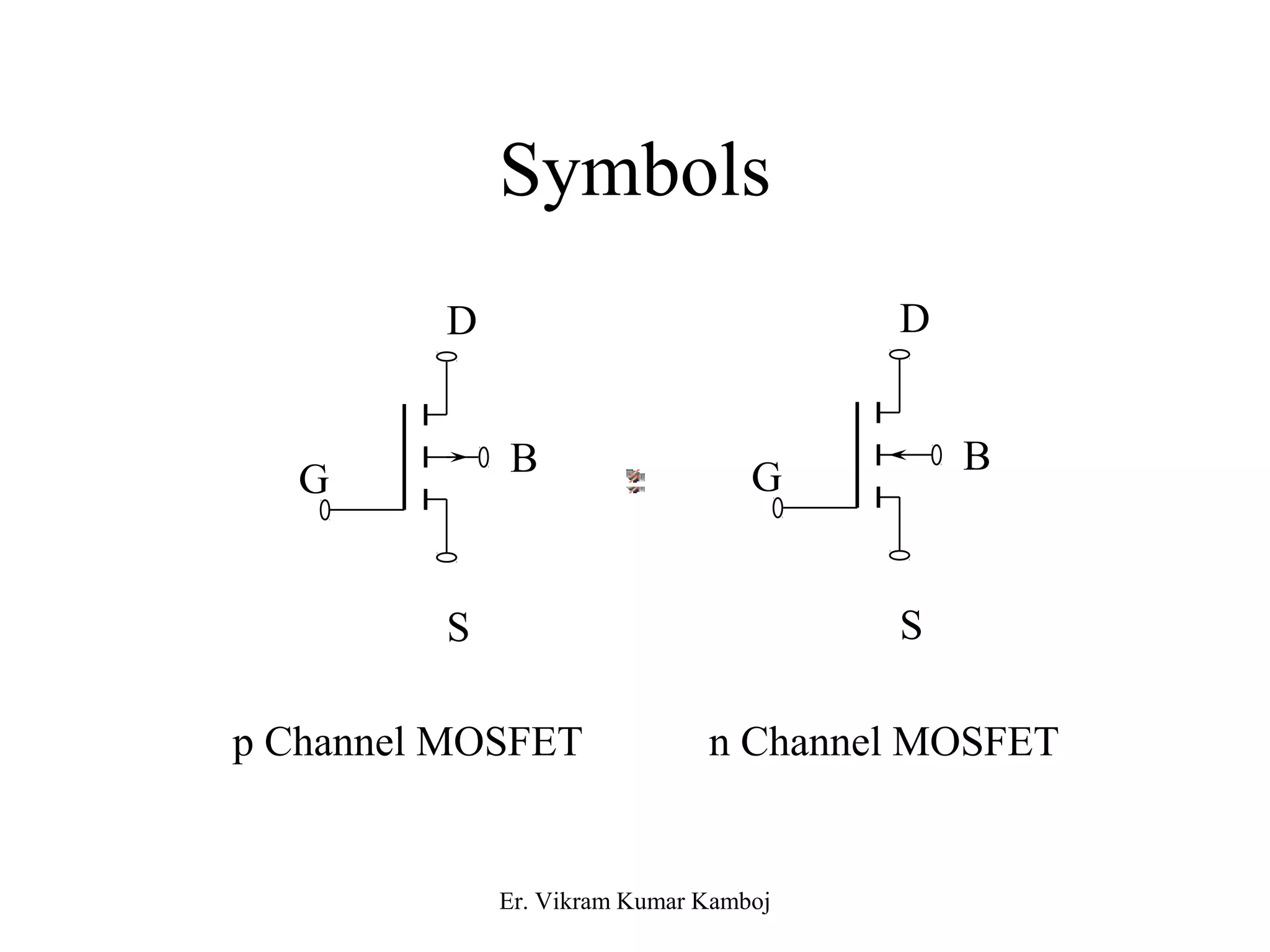

The document discusses the metal-oxide-semiconductor field-effect transistor (MOSFET). It describes the basic structure of the MOSFET, including the source, gate, and drain terminals. It also discusses the different types of MOSFETs, such as n-channel and p-channel MOSFETs, as well as depletion and enhancement MOSFETs. The key characteristics of MOSFETs are summarized, including the different regions of operation depending on the voltages applied to the gate, source, and drain terminals. Common applications of MOSFETs in analog and digital circuits are also outlined.

![Physical Structure of MOS FETS

NMOS

PMOS

Er. Vikram Kumar Kamboj

[Adapted from Principles of CMOS VLSI Design by Weste & Eshraghian]](https://image.slidesharecdn.com/14827mosfet-141214020912-conversion-gate02/75/14827-mosfet-10-2048.jpg)