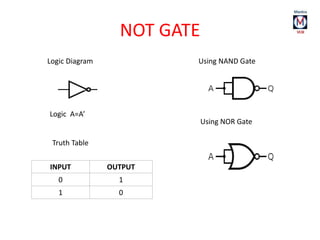

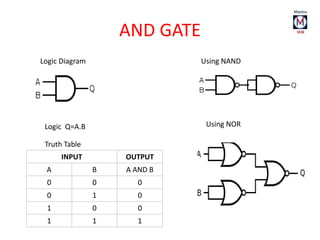

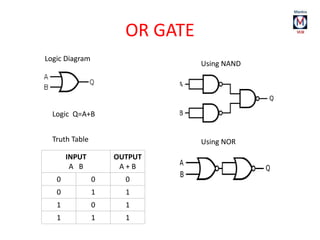

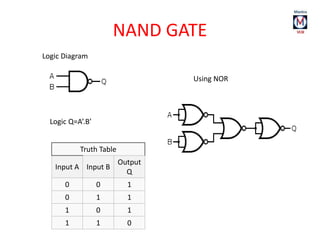

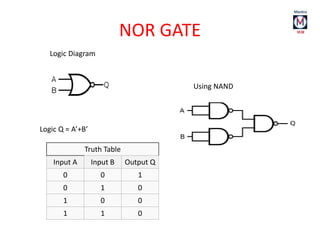

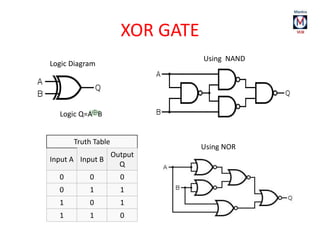

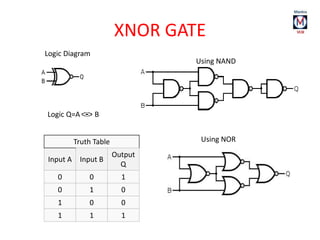

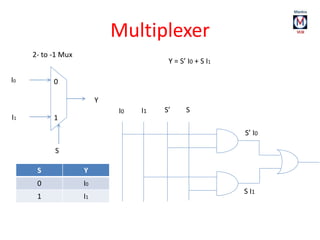

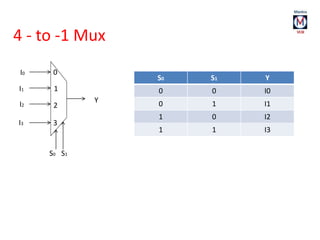

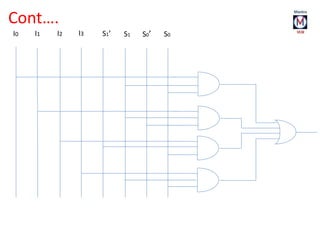

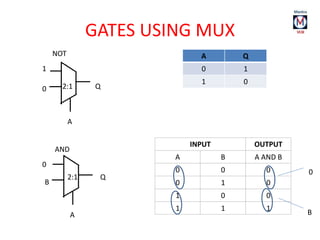

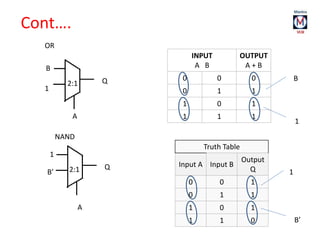

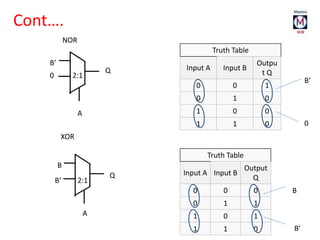

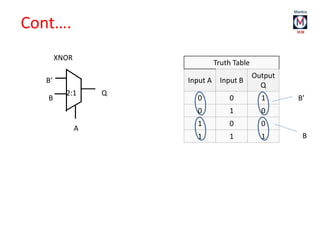

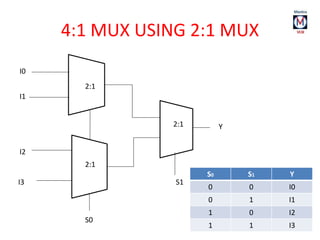

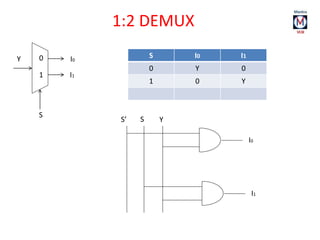

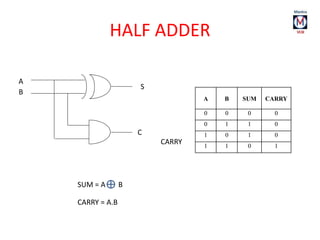

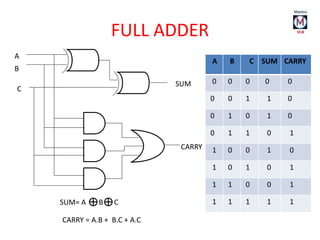

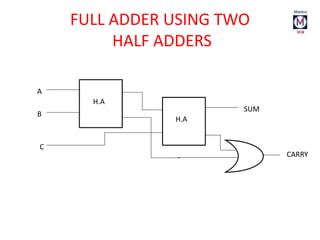

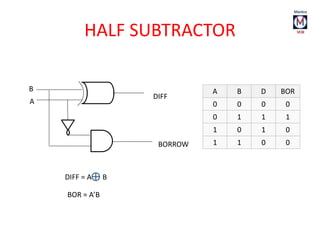

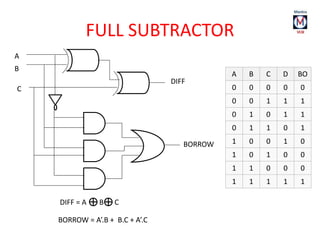

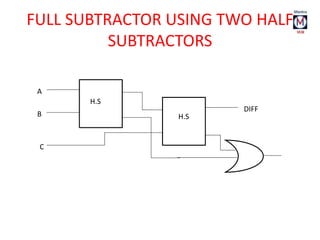

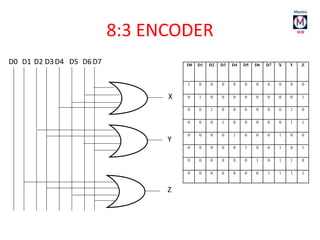

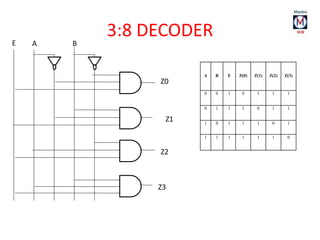

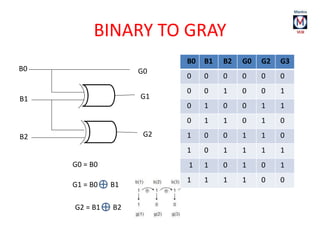

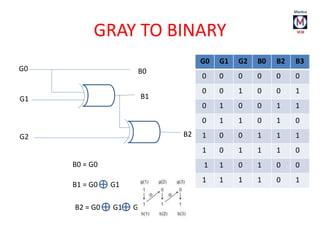

The document summarizes basic digital logic gates and components including NOT, AND, OR, NAND, NOR, XOR, XNOR gates. It also discusses multiplexers, demultiplexers, half/full adders, half/full subtractors, encoders, decoders, and conversions between binary and gray codes.