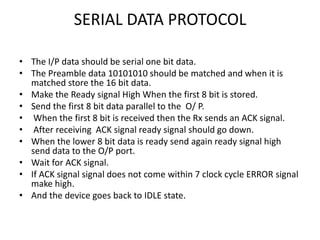

The document describes a serial data protocol that uses a preamble pattern to detect incoming data, a shift register to store the 16-bit data packets, and a state machine to control the transfer of the 8-bit data chunks to output and wait for acknowledgement signals between transfers. A test bench is also proposed to generate clock and reset signals to test the top module by sending serial data and checking for the acknowledgement response.