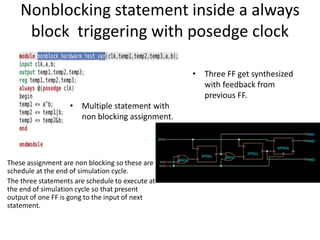

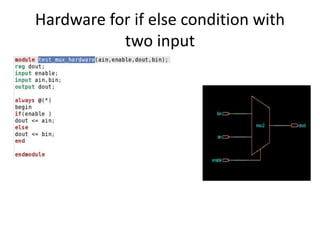

The document describes how different Verilog code constructs are synthesized to hardware. It provides examples of how always blocks, variables assignments, if/else statements, case statements, mathematical operations, counters and other code are mapped to logic gates, flip-flops and other digital circuits.