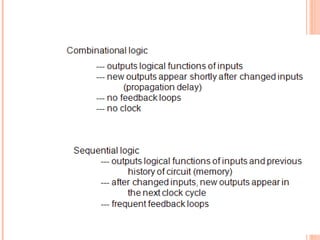

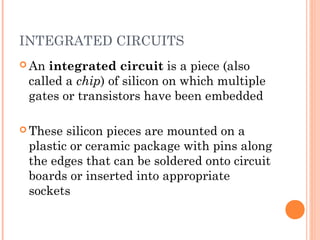

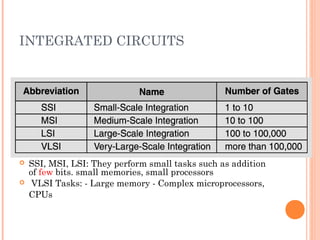

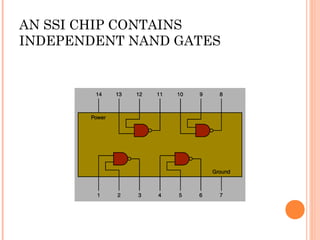

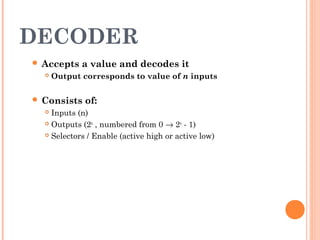

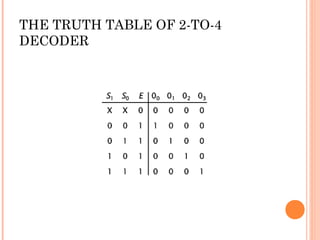

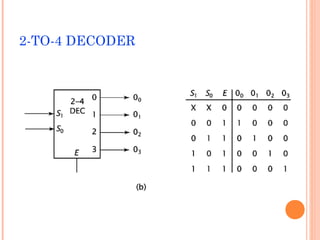

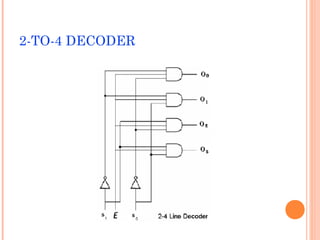

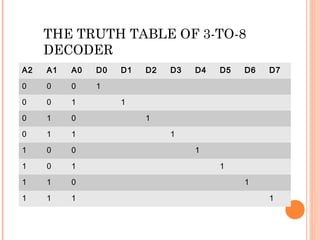

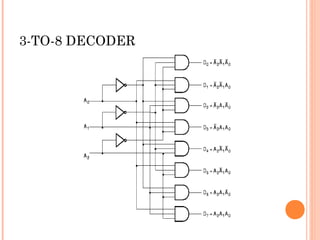

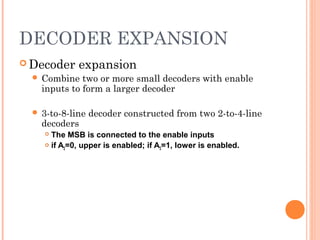

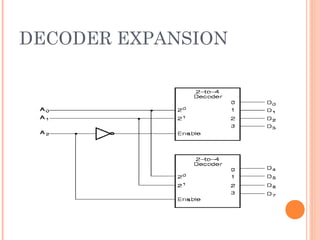

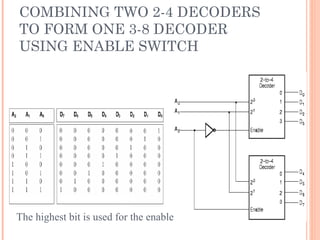

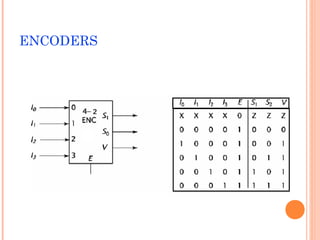

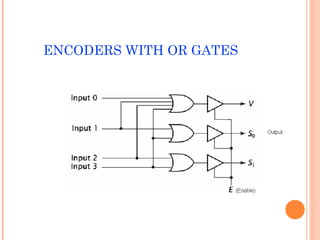

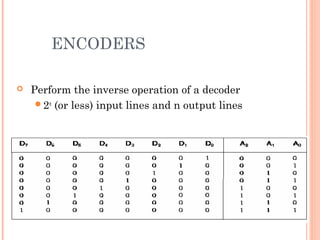

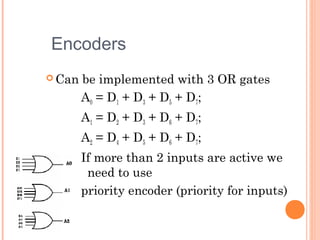

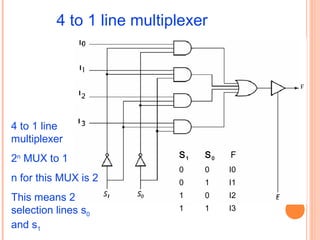

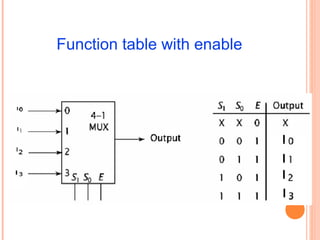

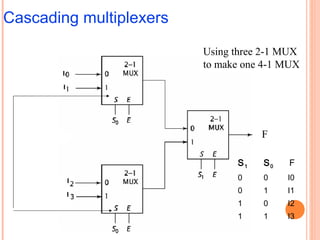

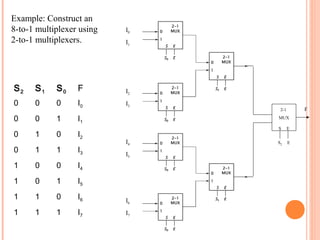

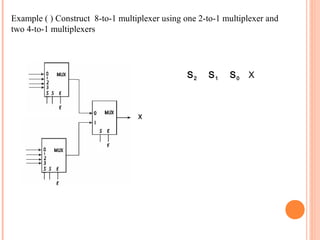

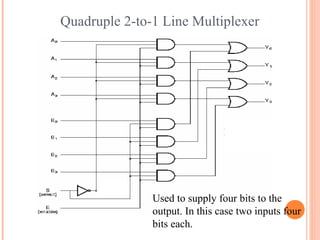

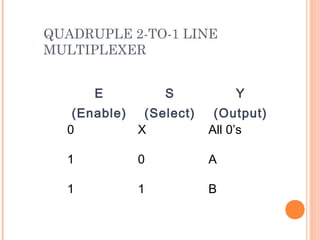

An integrated circuit is a small chip of silicon that contains multiple transistors. Decoders and encoders are types of combinational logic circuits. A decoder accepts an input and uses it to activate one of its outputs, while an encoder performs the inverse by activating its outputs based on active inputs. Decoders and multiplexers are similar in that they select an output from multiple inputs, but decoders have multiple outputs while multiplexers have a single output. Multiplexers can be cascaded to increase the number of inputs selected from.