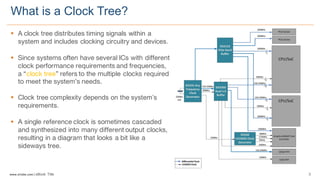

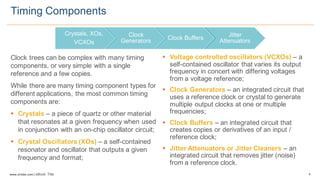

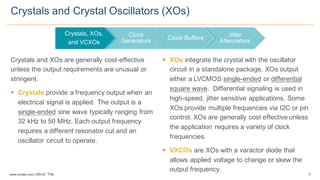

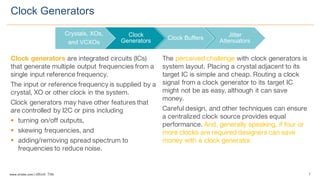

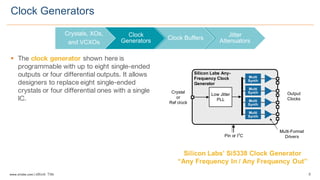

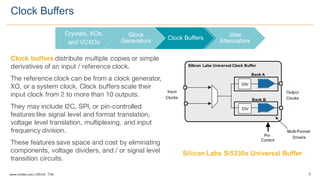

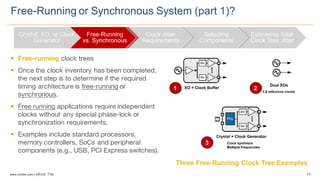

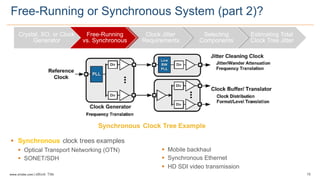

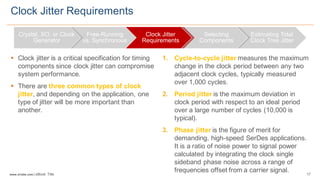

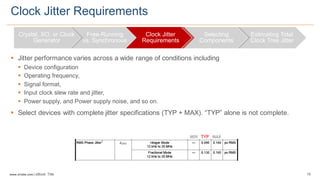

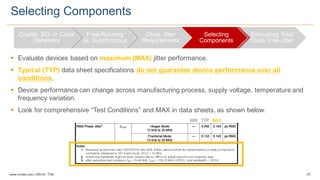

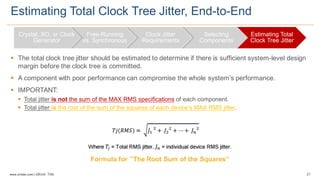

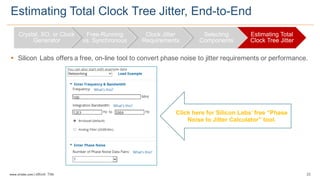

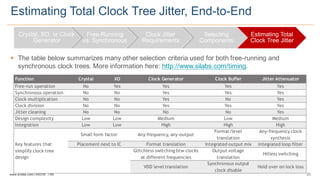

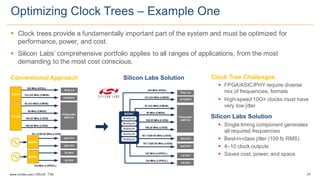

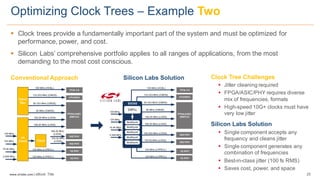

The document provides a comprehensive overview of clock trees, detailing their function in distributing timing signals across systems with various clock performance needs. It emphasizes the significance of components like crystals, oscillators, clock generators, and jitter attenuators in the design and optimization of clock trees, considering factors like frequency output and jitter performance. Additionally, it discusses the critical design criteria and selection processes necessary for effective clock tree implementation in both free-running and synchronous systems.