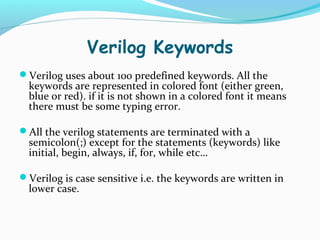

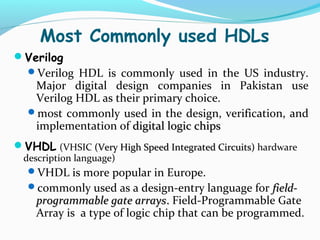

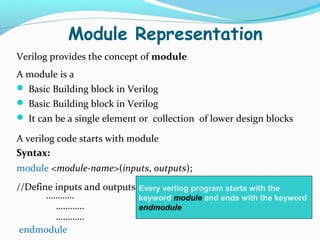

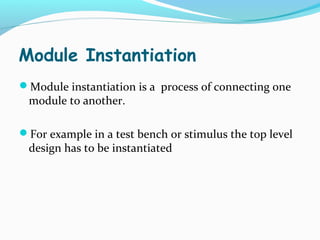

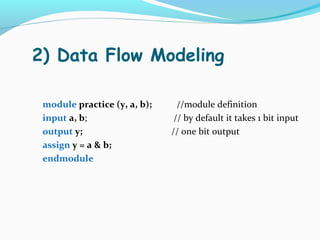

Hardware description languages (HDLs) allow designers to describe digital systems at different levels of abstraction in a textual format. The two most commonly used HDLs are Verilog and VHDL. Verilog is commonly used in the US, while VHDL is more popular in Europe. HDLs enable simulation of designs before fabrication to verify functionality. Digital designs can be modeled at the gate level, data flow level, or behavioral level in Verilog. Verilog code consists of a design module and test bench module to stimulate inputs and observe outputs.

![Input Output Definition

Once the module is defined at the start the inputs and

outputs are to be defined explicitly. e.g.

input a , b //means there are 2 inputs of one bit

each

If input or output is more than 1 bit i.e. two or more bits,

then the definition will be:

input [3:0] A, B; //4 bit inputs A3-A0 and B3-B0

output [3:0] C;](https://image.slidesharecdn.com/veriloghdl-130130165613-phpapp02/85/Verilog-hdl-13-320.jpg)

![TOP LEVEL MODULE

//Define a 4 bit 4 adder

module toplevel_fa(sum,c_out,a,b,c_in);

//I/O port declaration

output [3:0] sum;

output c_out;

input [3:0] a, b;

input c_in;

//internal nets

wire c1,c2,c3;

//Instantiate four 1-bit full adder

fulladder fa0(sum[0],c1,a[0],b[0],c_in);

fulladder fa1(sum[1],c2,a[1],b[1],c1);

fulladder fa2(sum[2],c3,a[2],b[2],c2);

fulladder fa3(sum[3],c_out,a[3],b[3],c3);

endmodule](https://image.slidesharecdn.com/veriloghdl-130130165613-phpapp02/85/Verilog-hdl-27-320.jpg)

![Test Bench (stimulus)

//define stimulus toplevel module

module stimulus;

reg [3:0]a,b; //set up variables

reg c_in;

wire [3:0] sum;

wire c_out;

//Instantiate the toplevelmodule(ripple carry adder) call it tl

toplevel_fa tl(sum,c_out,a,b,c_in);](https://image.slidesharecdn.com/veriloghdl-130130165613-phpapp02/85/Verilog-hdl-28-320.jpg)