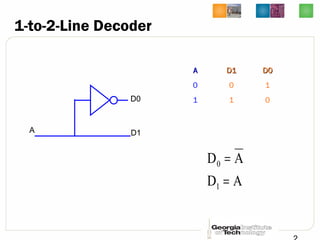

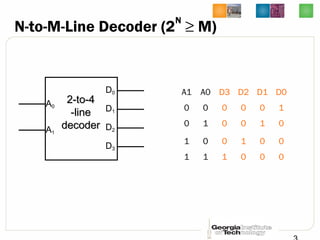

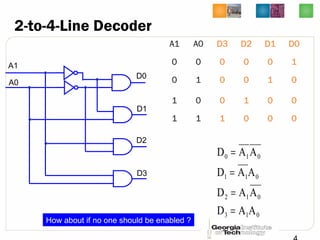

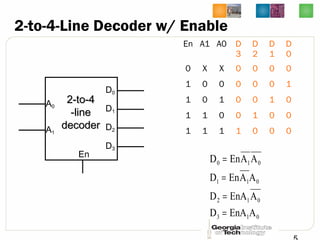

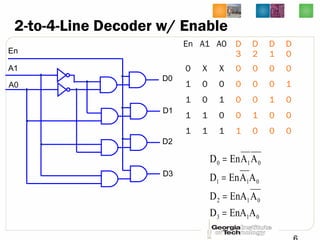

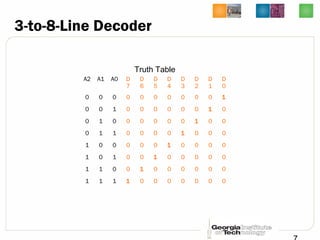

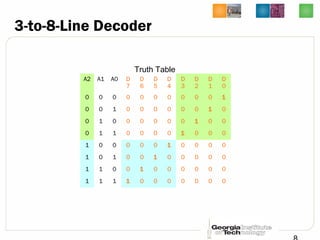

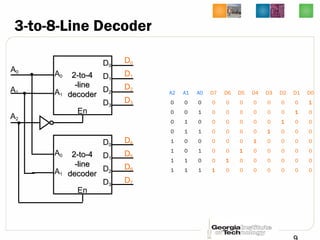

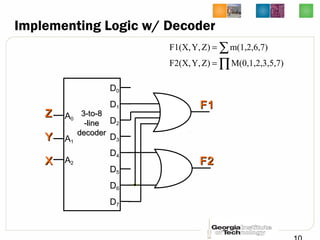

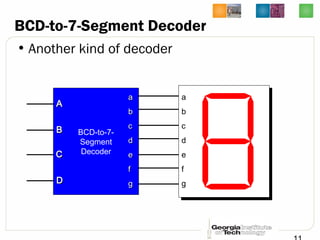

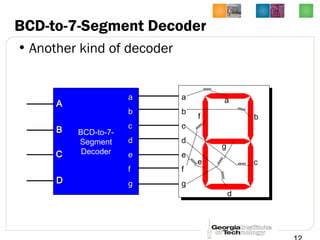

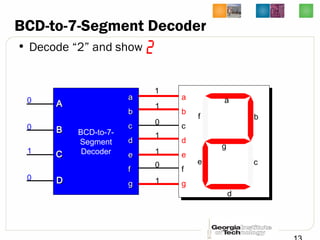

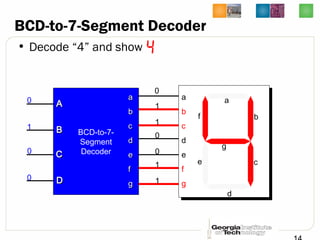

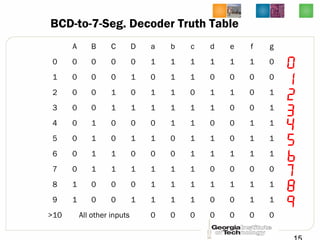

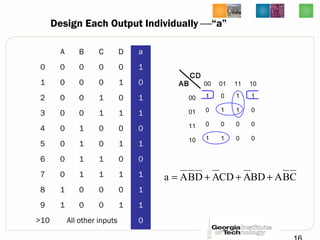

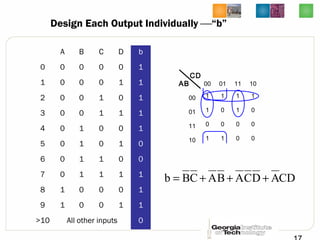

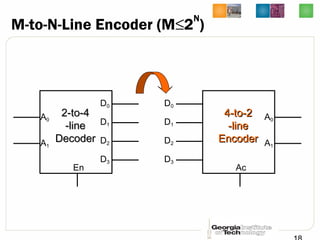

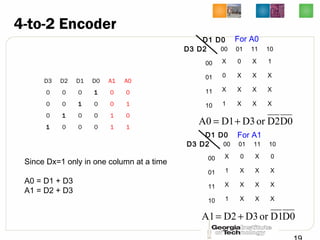

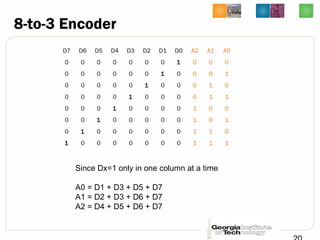

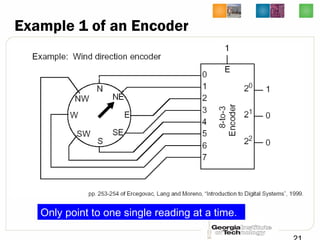

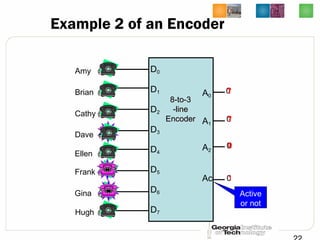

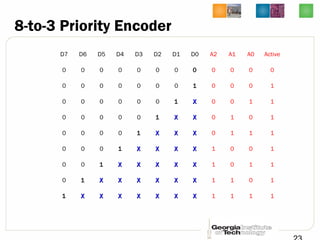

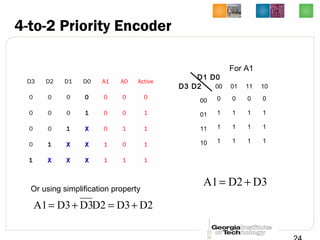

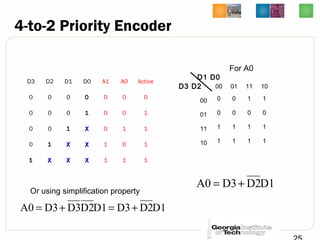

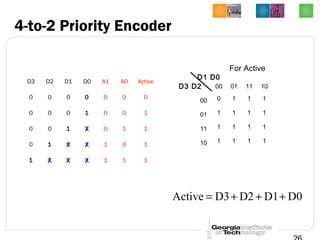

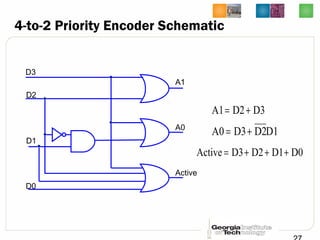

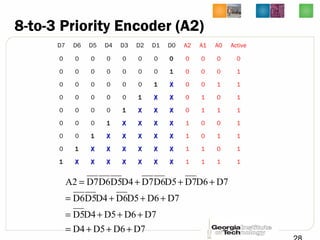

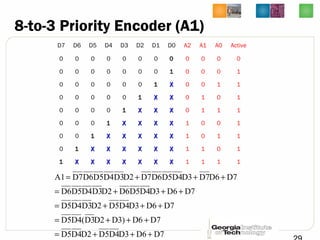

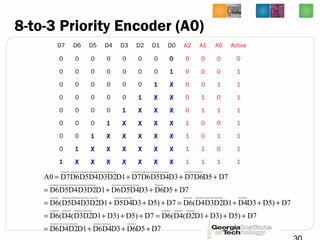

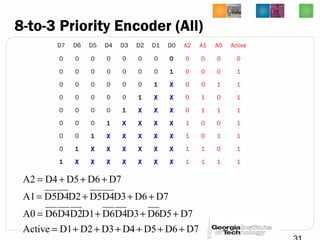

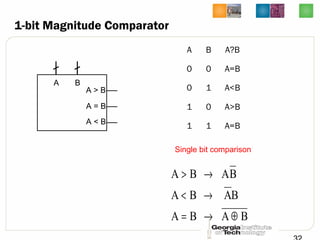

This document discusses different types of decoders and encoders used in digital logic circuits. It begins by explaining 1-to-2 line, N-to-M line, and 2-to-4 line decoders. It then describes decoders with enables and how to implement logic functions using decoders. The document also covers BCD-to-7 segment decoders and designing the outputs individually. Finally, it summarizes M-to-N line encoders and provides examples of 4-to-2 and 8-to-3 encoders as well as priority encoders.

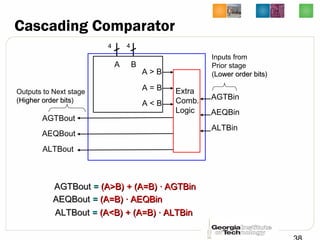

![16-bit Cascading Comparator

A B

AGTBin

AEQBin

ALTBin

4 4

AGTBout

AEQBout

ALTBout

A[3:0] B[3:0]

A B

AGTBin

AEQBin

ALTBin

4 4

AGTBout

AEQBout

ALTBout

A[7:4] B[7:4]

A B

AGTBin

AEQBin

ALTBin

4 4

AGTBout

AEQBout

ALTBout

A[11:8] B[11:8]

A B

AGTBin

AEQBin

ALTBin

4 4

AGTBout

AEQBout

ALTBout

A[15:12] B[15:12]

0

1

0

A>B

A<B

A=B

B[15:0]

A[15:0]](https://image.slidesharecdn.com/lec11-dec-150829105857-lva1-app6892/85/Lec11-Intro-to-Computer-Engineering-by-Hsien-Hsin-Sean-Lee-Georgia-Tech-Decoder-Encoder-and-Comparator-39-320.jpg)