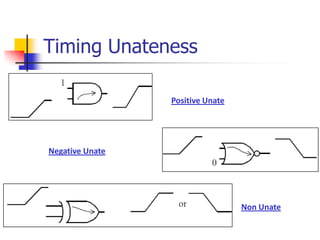

This document discusses library characterization, which involves characterizing standard cell libraries used in semiconductor design. It begins with an overview of why library characterization is an interesting career and then discusses fundamental terminology. It provides examples of characterizing an inverter and D flip-flop, covering timing analysis, power characterization, and more. Advanced topics discussed include state dependent delays, load capacitance characterization, and measuring tri-state delays. References are provided for further reading.