Designing State Machine

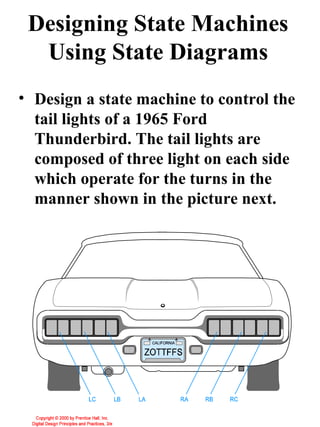

- 1. Designing State Machines Using State Diagrams • Design a state machine to control the tail lights of a 1965 Ford Thunderbird. The tail lights are composed of three light on each side which operate for the turns in the manner shown in the picture next.

- 2. Designing State Machines Using State Diagrams • The state machine has: – Three inputs: left, and right turns, and hazard. – Six outputs: LA, LB, LC, RA, RB, and RC. – Free running clock with frequency equal to the flashing rate.

- 3. Designing State Machines Using State Diagrams • State name represents • LA = L1+L2+L3+LR3 a logic expression that • is 1 only in that state LB = L2+L3+LR3 • The output equations • LC = L3+LR3 may be written • RA = R1+R2+R3+LR3 without assigning • RB = R2+R3+LR3 coded states • RC = R3+LR3

- 4. For the state diagram to be unambiguous: The transition expressions on the arcs leaving each state have to be mutually exclusive and all inclusive. That is, for each state, no two expressions are 1 for the same input combination, and some expression is 1 for every input combination. This can be confirmed algebraically by performing two steps Mutual exclusion: For each state, show that the logical product of each pair of transition expression on arcs leaving that state is zero. If there are n arcs, then there are n(n-1)/2 logical products to evaluate. All inclusion: For each state show that the logical sum of the transition expressions on all arcs leaving the state is 1.

- 5. The state diagram in not mutually exclusive because for some input combinations more than one transition expressions are 1. State IDLE I/p Transition Expressions combinations Le Ri Ha L R H L+R+H 0 0 0 0 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 1 1 0 1 1 0 1 0 0 1 0 0 0 1 0 1 1 0 1 0 1 1 0 1 1 0 0 1 1 1 1 1 1 0

- 6. • Some of the logical products for each pair of transition expression on arcs leaving IDLE state is not zero. For the state IDLE Arcs leaving the state: 4 L, R, H, L + R + H Logical products to evaluate:4*3/2 = 6 L·R ≠ 0, L·H ≠ 0, R·H ≠ 0 L· =0 L+R+H R· =0 L+R+H H· =0 L+R+H • All inclusion: For each state the logical sum of the transition expressions on all arcs leaving the state is one. L+R+H+ L + R + H =1

- 7. Problem - The state diagram doesn’t handle multiple inputs asserted simultaneously. That is, what happens in the IDLE state if both LEFT and HAZ are asserted? According to the state diagram the machine goes into two states L1 and LR3 which is impossible. The problem is avoided by giving HAZ input a priority. Also we treat both LEFT and RIGHT asserted simultaneously as a Hazard request, since the driver is completely confused and requires help.

- 9. The state diagram in now mutually exclusive State IDLE I/p comb- Transition Expressions inations L⋅R + H R⋅H ⋅L Le Ri Ha L⋅H ⋅R L+R+H 0 0 0 0 0 0 1 0 0 1 0 1 0 0 0 1 0 0 0 1 0 0 1 1 0 1 0 0 1 0 0 1 0 0 0 1 0 1 0 1 0 0 1 1 0 0 1 0 0 1 1 1 0 1 0 0

- 10. • The logical products for each pair of transition expression on arcs leaving IDLE state is zero. For the state IDLE Arcs leaving the state: 4 L ⋅ H ⋅ R , L ⋅ R + H , R ⋅ H ⋅ L, L + R + H Logical products to evaluate:4*3/2 = 6 All 6 products are zero. • For each state the logical sum of the transition expressions on all arcs leaving the state is one. • Hence the state diagram now is both mutually exclusive and all inclusive

- 11. • In the new state diagram we notice that once the turn has been initiated the state diagram allows the cycle to run to completion even if HAZ is asserted. This may have a certain aesthetic appeal, however it would be safer to allow the machine to go into Hazard mode as soon as possible. • Hence the state diagram is modified as shown next.

- 13. State Assignment • IDLE state of 000. • Q1 and Q0 are used to count in gray code sequence (IDLE→L1→L2→L3→IDLE) (IDLE→R1→R2→R3→IDLE). • Q2 identifies LEFT or RIGHT turn. • HAZ state of 100.

- 14. • Next step – sort of transition table • In this case the transitions are specified by expressions rather than an exhaustive tabulation of next states Transition List

- 15. Synthesis using transition List • Develop a set of transition equations that define the next state variable S* in terms of current state S and inputs • The transition list may be viewed as a sort of hybrid truth table in which the state-variable combinations for the current state are listed explicitly and input combinations are listed algebraically. • Reading down a S* column find a sequence of 0s and 1s indicating the value of S* for various state/input combinations. • A transition equation for a next state variable S* can be written using a sort of hybrid canonical sum. • S* = ∑ (transition p-term) Transition list rows where S* = 1

- 16. Synthesis using transition List • Transition p-term is the product of the current states min-term and the transition expression. • The transition equation has one transition p-term for each row of the transition list that contains a ‘1’ in the S* column. • There is no guarantee that the transition equations obtained by this method are in any sense minimal. • The equations are not even in the standard POS or SOP forms • They only provide a starting point for whatever combinational design method one might choose to synthesize the excitation logic for the FSM

- 17. Synthesis using transition List • Based on the transition list we get the following transition equations for Q2*, Q1* and Q0* ( ) Q 2* = Q 2 ⋅ Q1⋅ Q0 ( L ⋅ R + H ) + (Q 2 ⋅ Q1⋅ Q0 )( L ⋅ R ⋅ H ) + (Q 2 ⋅ Q1⋅ Q0 )( H ) + (Q 2 ⋅ Q1⋅ Q0 )( H ) + (Q 2 ⋅ Q1⋅ Q0 )( H ) + (Q 2 ⋅ Q1⋅ Q0 )( H ) + ( Q 2 ⋅ Q1⋅ Q0)( H ) + ( Q 2 ⋅ Q1 ⋅ Q0) ( H ) ( ) Q 2* = Q 2 ⋅ Q1⋅ Q0 ( R + H ) ( ) + Q 2 ⋅ Q0 ( H ) + ( Q 2 ⋅ Q0)

- 18. Synthesis using transition List ( )( ) ( Q1* = Q 2 ⋅ Q1 ⋅ Q0 H + Q 2 ⋅ Q1⋅ Q0 H )( ) + (Q 2 ⋅ Q1⋅ Q0 )( H ) + ( Q 2 ⋅ Q1⋅ Q0) ( H ) Q1* = Q0( H ) ( )( Q0* = Q 2 ⋅ Q1 ⋅ Q0 L ⋅ R ⋅ H ) + (Q 2 ⋅ Q1 ⋅ Q0)( L ⋅ R ⋅ H ) + (Q 2 ⋅ Q1⋅ Q0 )( H ) + (Q 2 ⋅ Q1⋅ Q0 )( H ) ( )( Q0* = Q 2 ⋅ Q1 ⋅ Q0 H ( L ⊕ R ) ) + (Q1⋅ Q0)( H )

- 19. Excitation equations • On deriving the transition equations it is desirable to use the D flip flops as memory elements • The transition equation directly gives the excitation equation in this case • The excitation equations of other flip- flops are not so easy to derive • Majority of the PLD & ASIC based systems employ D flip flops.

- 20. Variations in the scheme • If the column for a particular next state variable contains fewer 0s than 1s, it may be advantageous to write that variables transition equation in terms of 0s in its column S*= ∑ (transition p terms ) transition list rows where S *= 0 • That is S * = 1 for all the p terms for which S * = 0 • Thus a transition equation may be written for Q 2 * as the sum of 7 p-terms ( )( Q 2 * = Q 2 ⋅ Q1 ⋅ Q0 L + R + H ) + (Q 2 ⋅ Q1⋅ Q0 )( L ⋅ R ⋅ H ) + (Q 2 ⋅ Q1⋅ Q0 )( H ) + (Q 2 ⋅ Q1 ⋅ Q0 )( H ) + (Q 2 ⋅ Q1 ⋅ Q0)(1) + (Q 2 ⋅ Q1⋅ Q0 )(1) + (Q 2 ⋅ Q1 ⋅ Q0)(1)

- 21. Variations in the scheme ( ) ( Q 2 * = Q 2 ⋅ Q1 ⋅ Q0 ⋅ H ⋅ R + Q 2 ⋅ Q0 ⋅ H ) ( ) ( + Q1⋅ Q0 + Q 2 ⋅ Q0 ) • To obtain an expression for Q 2 * we simply complement both sides of the reduced equation • To obtain an expression for a next state variable V * directly, using the 0s in the transition list, we can complement the right hand side of the general V * equation using DeMorgan’s theorem, obtaining a sort of hybrid canonical product V* = ∏ (transition s terms) transition list rows where V *= 0 •Transition s-term is the sum of the current states max-term and the complement of the transition expression.

- 22. Unused states • In this problem there were no unused states • However, in case there are some unused states in the problem then they do not reflect in the transition list • They are treated as don’t care in a very limited sense • While writing equations for S*, the sum of p-terms for rows that had an explicit 1 in the corresponding column were taken • Although we don’t consider the unused states, the procedure implicitly treats them as if they had 0s in the corresponding column • Conversely for S * the procedure implicitly treats unused states as if they had 1s in the corresponding column

- 23. Output-Coded state assignment • The machines outputs are a function of state only • A different output combination is produced in each named state • We can use the outputs as state variables and assign each named state to the required output combination • This sort of assignment is termed as output-coded state assignment • Sometimes results in excitation equations that are simpler than the set of excitation and output equations obtained with a state assignment using minimum number of state variables • It saves cost in a PLD based design since fewer PLD macrocells or outputs are needed overall • Current State| Transition Exp| Next State

- 24. Decomposing State Machines • Just like large programs being decomposed into procedures or subroutines, large state-machine problems are often solved with a collection of smaller state machines • The original design problem is put into a natural hierarchical structure, so that the functions and uses of the sub-machines are obvious, making it unnecessary even to write a state table for the sub-machine • The most commonly used sub-machine is a counter. The main machine usually STARTS the counter when it wishes to stay in a particular main state for n counts • The counter counts the n counts and sends a DONE signal when the count is completed

- 25. Decomposing State Machines • The main machine is designed to wait in the same state till it receives the DONE signal from the sub-machine • This adds an extra output and input to the main machine (START and DONE) but saves n -1 states • The simplest type of decomposition is shown in figure • The Main machine provides the primary inputs and outputs and executes the top level control algorithm. • The sub-machines perform the lower level functions under the control of the main machine and may also optionally handle some of the primary inputs and outputs

- 26. Decomposing State Machines Inputs Outputs Sub Machine Start 1 1 Done 1 Main Machine Start 2 Sub Done 2 Machine 2 Typical hierarchical state-machine structure