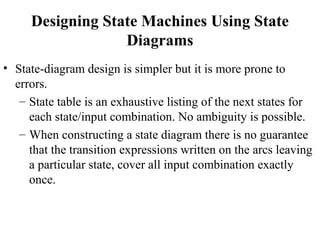

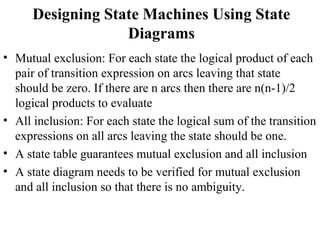

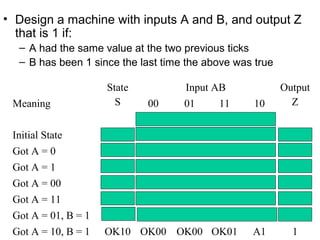

This document discusses state machine design using state diagrams and state tables. It provides examples of designing a state machine with inputs A and B and output Z. Key steps include:

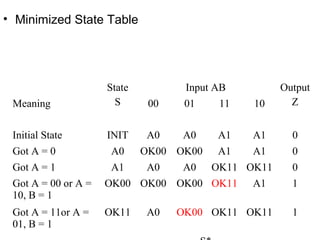

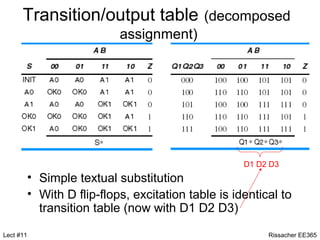

1. Defining the machine's states and behaviors in a state table.

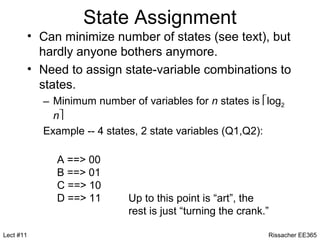

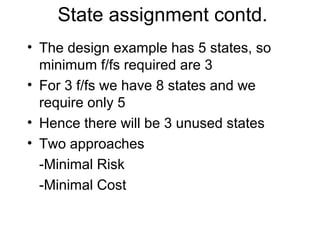

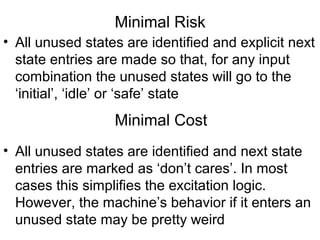

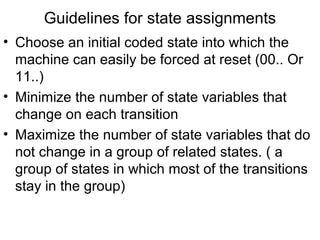

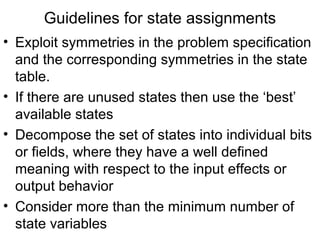

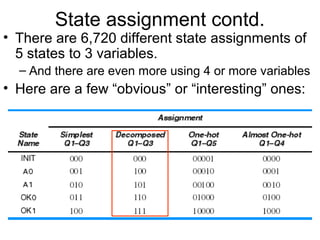

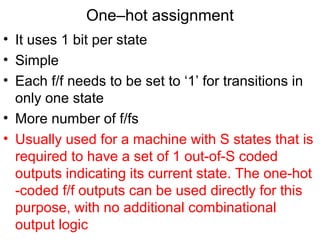

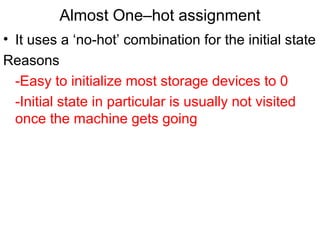

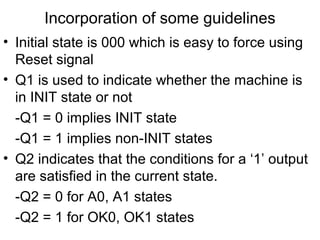

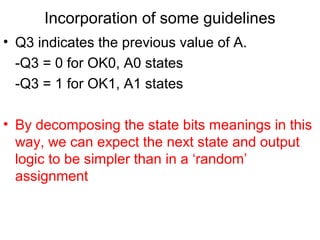

2. Assigning state codes to minimize the number of variables needed.

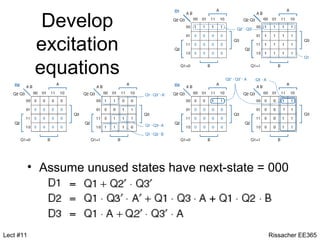

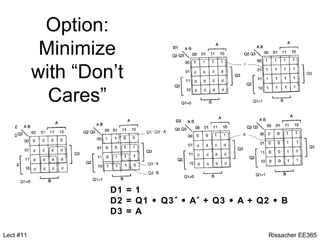

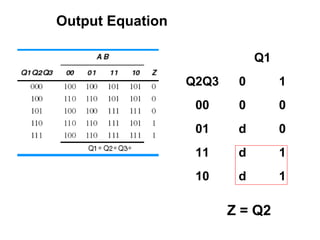

3. Deriving excitation and output equations from the state table.

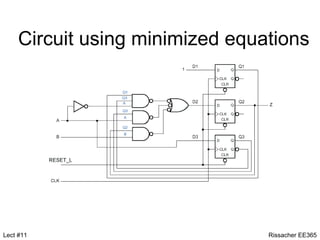

4. Implementing the state machine design using flip-flops and combinational logic.