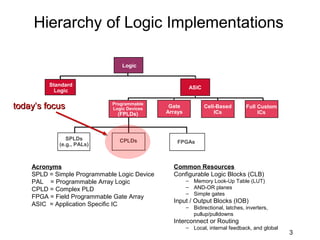

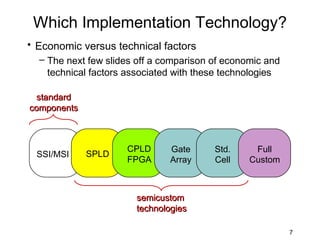

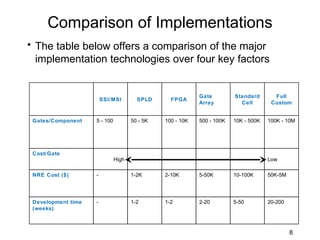

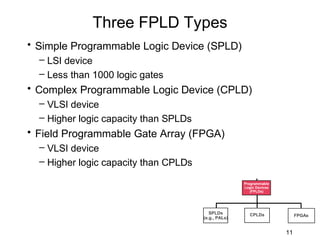

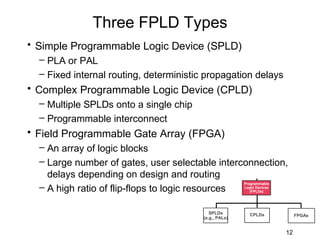

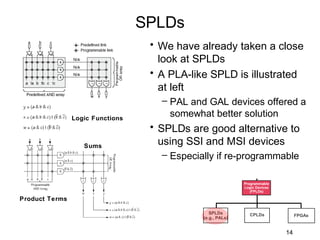

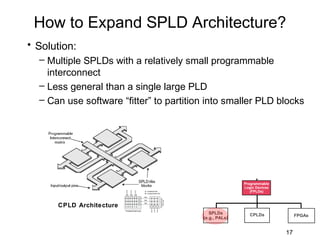

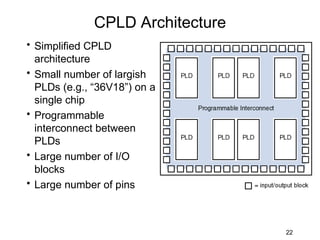

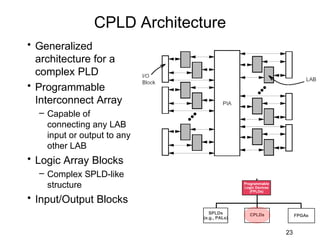

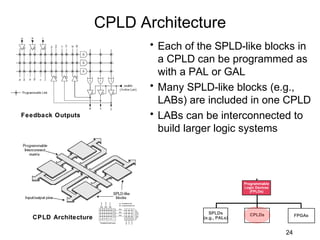

This document discusses complex programmable logic devices (CPLDs). CPLDs contain multiple simpler programmable logic devices (SPLDs) like PALs or GALs on a single chip connected by a programmable interconnect. This allows CPLDs to implement larger logic functions than SPLDs. CPLDs are made up of logic blocks, input/output blocks, and a programmable interconnect that can connect any logic block inputs or outputs. CPLDs generally provide better performance and more predictable timing than FPGAs but have lower density.