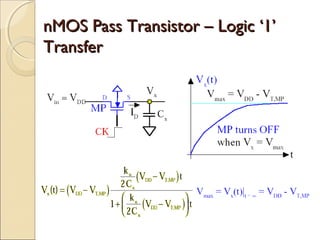

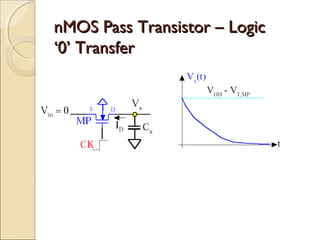

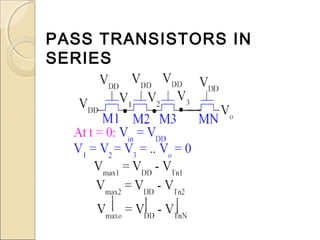

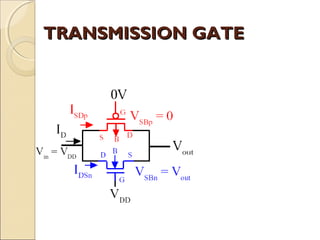

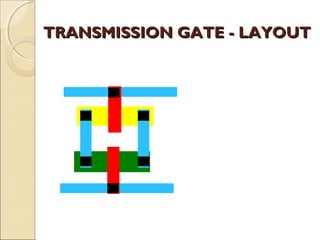

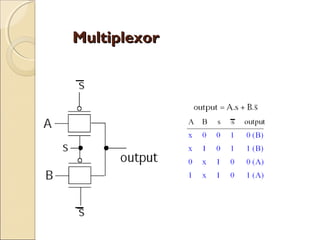

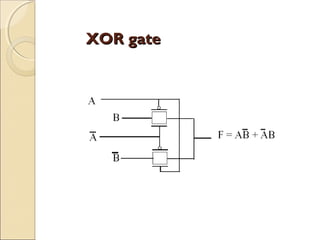

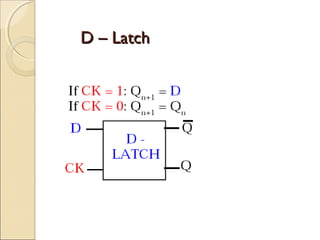

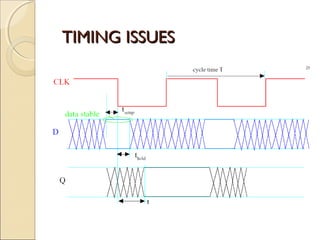

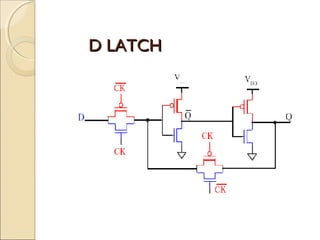

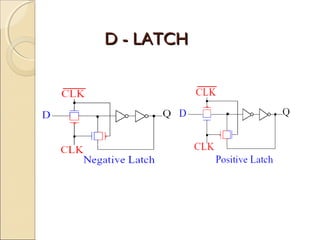

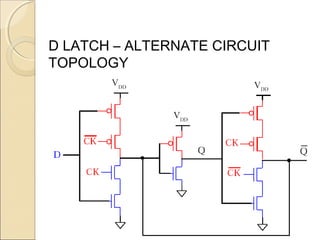

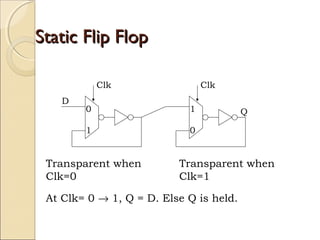

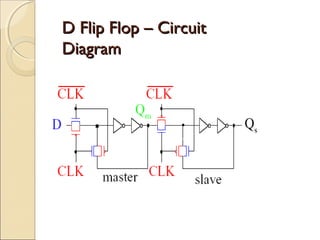

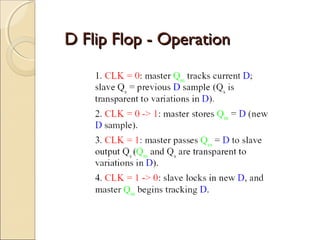

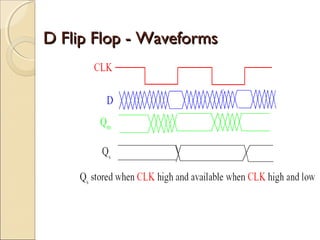

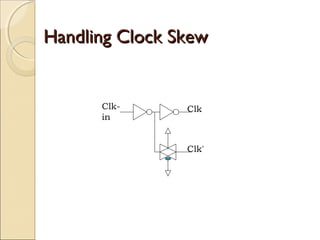

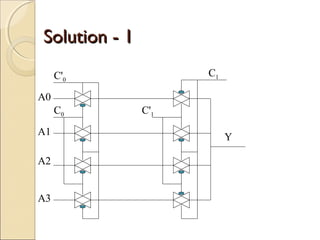

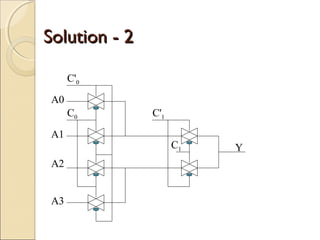

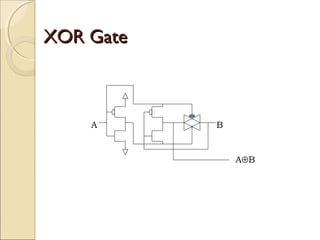

The document discusses pass transistor logic circuits. It describes how nMOS pass transistors can transfer logic 1 and 0 signals. Transmission gates are introduced which use both nMOS and pMOS pass transistors to pass strong signals in both directions. Applications of transmission gates include multiplexers, XOR gates, D latches, and D flip-flops. Clock skew management and different pass transistor logic families are also covered.