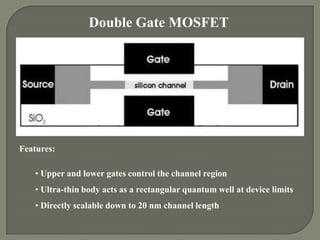

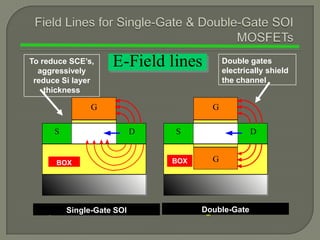

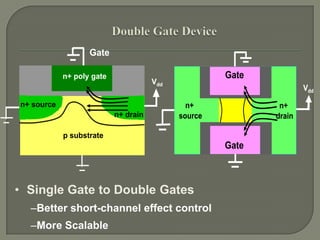

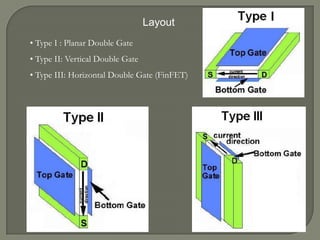

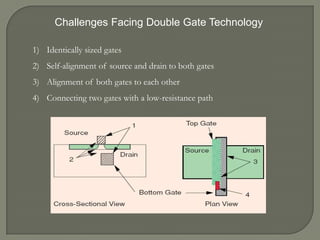

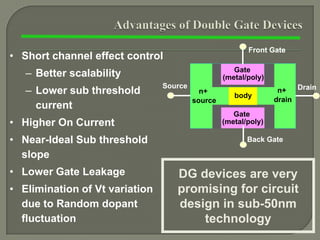

This document summarizes the double-gate MOSFET transistor. It begins by describing the basic operation of a single-gate MOSFET and then discusses the scaling limitations of bulk MOSFETs, such as decreasing carrier mobility and threshold voltage rolloff as channel length decreases. It introduces the double-gate MOSFET as a way to better control the channel and reduce short-channel effects. Key features of the double-gate MOSFET include two gates that control the ultra-thin body channel and allow direct scaling to small channel lengths of 20nm or less. Fabricating double-gate MOSFETs using a silicon-on-insulator approach provides benefits like low leakage currents. The double gates provide improved performance