This document discusses challenges and requirements for low-power design and verification. It begins with an overview of how leakage is significantly increasing due to process scaling and how active power is now a major portion of power budgets. New strategies are needed to address process variations and enhance scaling approaches. The verification flows must support multi-voltage domain analysis and rule-based checking across voltage states while capturing island ordering and microarchitecture sequence errors. Low-power implementation introduces challenges for design representation, implementation across tools, and verification. Methodologies and design flows must be adapted to account for power and ground nets becoming functional signals.

![Slide 17

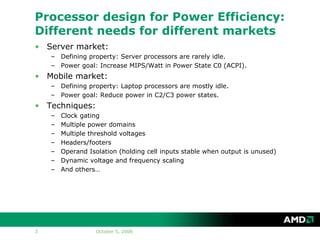

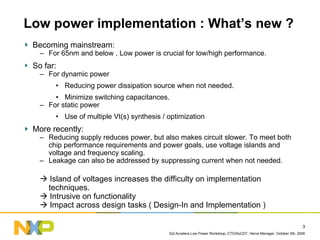

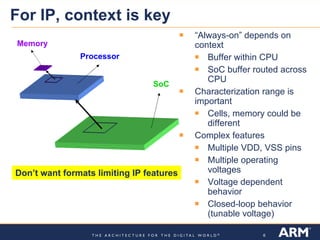

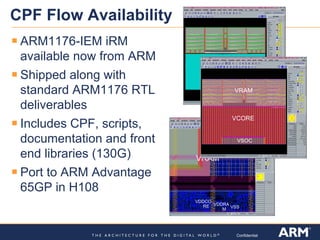

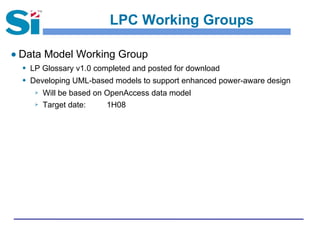

Hierarchical view of Energy Conservation

Software

Definitions

Dynamic system monitoring and intelligent control of energy

savings, work load profiling, [dvfs], profiling and partitioning

Architectural

Definitions

Heterogeneous processing resource optimization: MCU, DSP,

accelerators, functional processing units, memory usage

optimization

Design

Definitions

Hardware support for voltage islands, power gating, low-

power idle modes, SRPG, AWB, DVFS, DPTC, clock gating

PROCESS node

Definitions

Transistor design, Vt Optimization, memory bitcell design.

Special circuits, libraries, custom and analog blocks, SOI

Power Trees/Voltage islands, Connectivity of components & consistent

platform power modes, intelligent bus coding, dependency

discovery/optimization

Platform

Definitions

Thanks to Milind Padhye, Freescale Semiconductor, Austin Wireless Design Center](https://image.slidesharecdn.com/schulzaustinq22008-130422130434-phpapp01/85/Low-Power-Design-and-Verification-14-320.jpg)

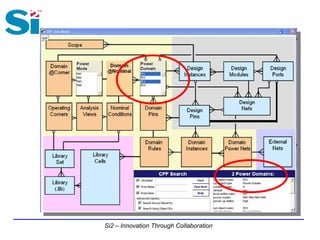

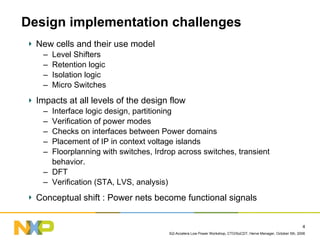

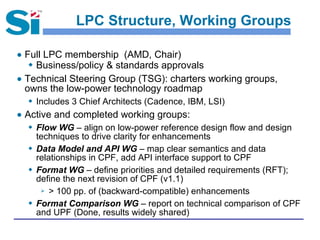

![– 11 –Innovation Through Collaboration – 11 –Innovation Through Collaboration – Low Power Coalition

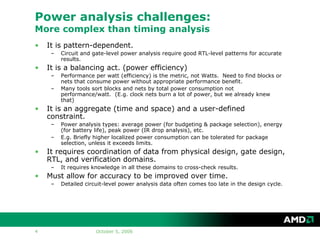

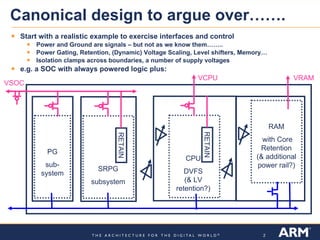

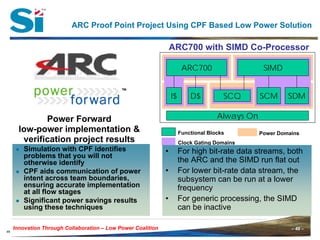

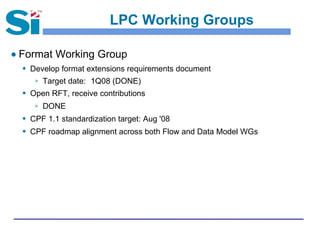

CPF Language

● CPF is TCL-based.

● CPF Language = TCL commands + CPF objects + Design objects

Power domain

Analysis view

Delay corner

Library set

Operating condition

● Design objects: objects that already exist in the RTL/gate netlist

Module, Instance, Net, Pin, Port

● Commands – 42 commands

set_* commands [version, scope, and general commands]

define_*_cell commands [library cell description]

create_*_rule commands [design intent]

update_*_rules commands [implementation directives]](https://image.slidesharecdn.com/schulzaustinq22008-130422130434-phpapp01/85/Low-Power-Design-and-Verification-32-320.jpg)

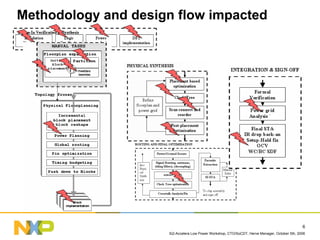

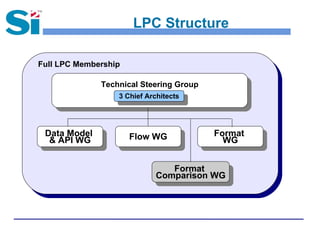

![– 24 –Innovation Through Collaboration – 24 –Innovation Through Collaboration – Low Power Coalition

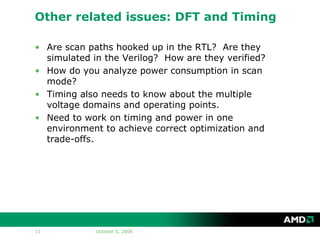

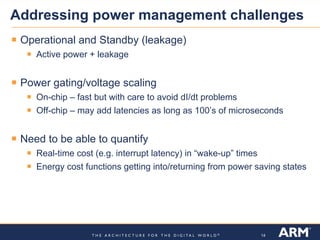

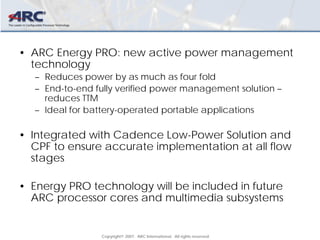

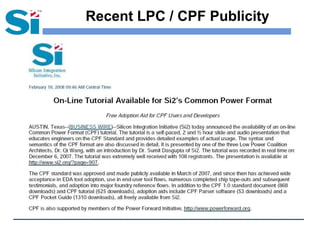

Specify Power Mode Transitions

create_mode_transition -name PM1toPM2 –from_mode PM1 –to_mode PM2

-start_condition { pcu_inst/ctrl[0] & pcu_inst/ctrl[1] }

-clock_pin { pcu_inst/clk } –cycles 100

create_mode_transition -name PM2toPM3 –from_mode PM2 –to_mode PM3

-start_condition { pcu_inst/ctrl[0] & !pcu_inst/ctrl[1] }

-clock_pin { pcu_inst/clk } –cycles 1000

create_mode_transition -name PM3toPM4 –from_mode PM2 –to_mode PM3

-start_condition { !pcu_inst/ctrl[0] & pcu_inst/ctrl[1] }

-clock_pin { pcu_inst/clk } –cycles 1000

create_mode_transition -name PM4toPM1 –from_mode PM2 –to_mode PM3

-start_condition { !pcu_inst/ctrl[0] & !pcu_inst/ctrl[1] }

-clock_pin { pcu_inst/clk } –cycles 200

PDcore PDau PDlu PDalu PDrf

PM1 1.2v

0.8v

PM3 0.8v off off off 1.2

PM4 0.8v 1.2v 1.2v 1.2v off

1.2v 1.2v 1.2v

PM2

1.2v

1.2v 1.2v 1.2voff

PM1

PM2

PM3

PM4](https://image.slidesharecdn.com/schulzaustinq22008-130422130434-phpapp01/85/Low-Power-Design-and-Verification-34-320.jpg)

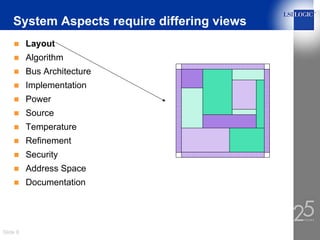

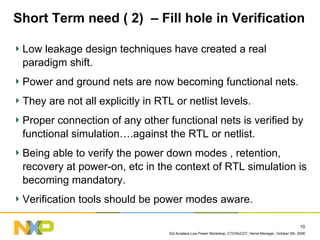

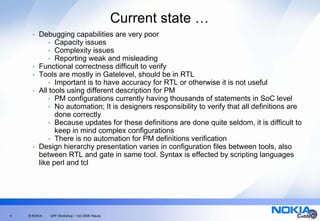

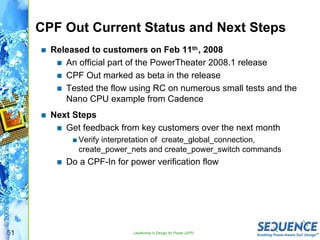

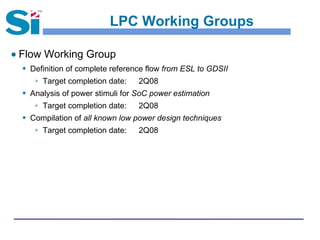

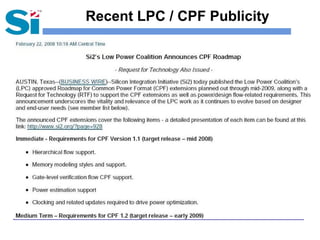

![Silicon Integration Initiative 6

set_design top

# Set up logic structure for all power domains

set_time_unit us

set_power_unit uW

create_power_domain -name PDcore -default

create_power_domain -name PDalu -instances {inst_A inst_B} -shutoff_condition {!pm_inst.pse_enable[0]}

create_power_domain -name PDrf -instances inst_C -shutoff_condition {!pm_inst.pse_enable[1]}

create_power_domain -name PD4 -instances inst_D -shutoff_condition {!pm_inst.pse_enable[2]}

# Define static behavior of all power domains and specify timing constraints

create_nominal_condition -name high -voltage 1.2

create_nominal_condition -name medium -voltage 1.1

create_nominal_condition -name low -voltage 1.0

create_power_mode -name PMhot -domain_conditions {PDcore@high PDalu@medium PDrf@high PD4@low} -default

create_power_mode -name PMcool -domain_conditions {PDcore@high PDrf@high PD4@low}

create_power_mode -name PMsleep -domain_conditions {PDcore@high PD4@low}

create_power_mode -name PMhibernate -domain_conditions {PDcore@low}

# Set up required isolation and state retention rules for all domains

create_state_retention_rule -name sr1 -domain PDalu -restore_edge {!pm_inst.pge_enable[0]}

create_state_retention_rule -name sr2 -domain PDrf -restore_edge {!pm_inst.pge_enable[1]}

create_state_retention_rule -name sr3 -domain PD4 -restore_edge {!pm_inst.pge_enable[2]}

create_isolation_rule -name ir1 -from PDalu -isolation_condition {pm_inst.ice_enable[0]} -isolation_output high

create_isolation_rule -name ir2 -from PDrf -isolation_condition {pm_inst.ice_enable[1]} -isolation_output high

create_isolation_rule -name ir3 -from PD4 -isolation_condition {pm_inst.ice_enable[2]} -isolation_output low

create_level_shifter_rule -name lsr1 -to {PDcore PDrf}

end_design

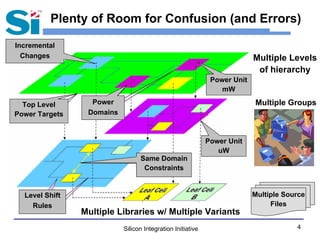

CPF Format Concepts

Define

PDs

Define

Nominals

PMs

Bind PD & NC

Rulesand

morerules

What if this command was in a different file and

the IP in PDcore had not been characterized at

the “low” nominal condition?](https://image.slidesharecdn.com/schulzaustinq22008-130422130434-phpapp01/85/Low-Power-Design-and-Verification-72-320.jpg)

![Silicon Integration Initiative 7

CPF Relational Analyzer

• Each object in the CPF hierarchy is tracked separately via metadata

• Architecture handles hierarchy merging, module cloning & port mapping

• Broad analysis – Analyze all objects and all O2O relationships

• Deep analysis – Every attribute, every object with every update

Interactive and Incremental:

Designed for “Hands-on” learners with English as a Second Language

Exposes the final state of the design intent compiled from many sources

Search and Report capabilities:

All searches can use standard wildcards of *, ?, [a-z], [0-9]

Any combination of CPF Objects, Property Names and Property Values](https://image.slidesharecdn.com/schulzaustinq22008-130422130434-phpapp01/85/Low-Power-Design-and-Verification-73-320.jpg)