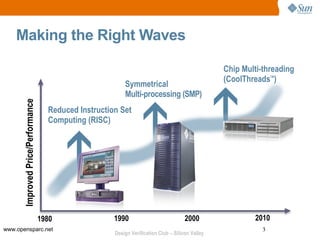

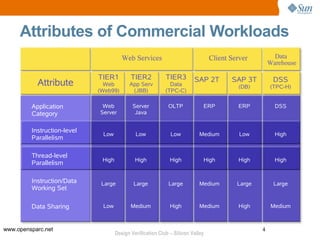

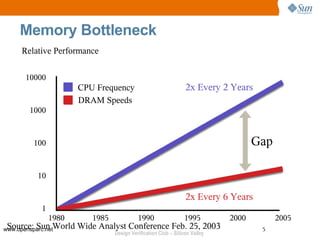

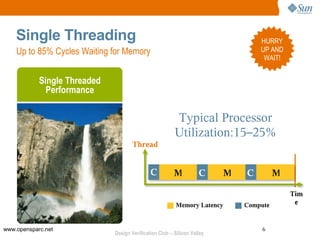

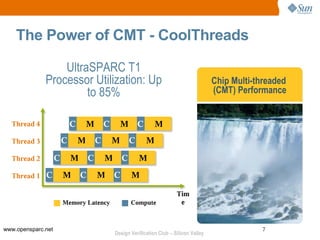

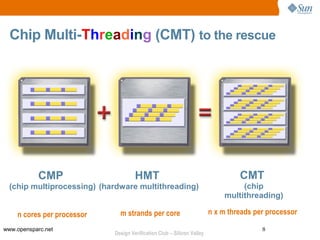

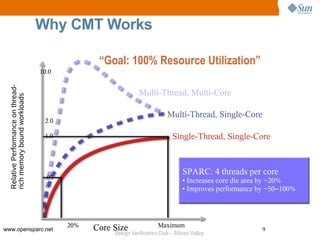

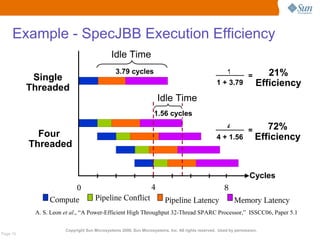

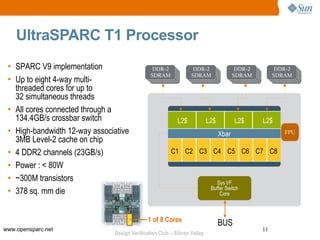

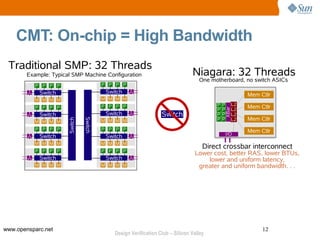

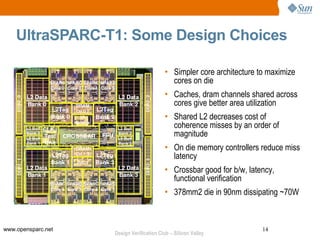

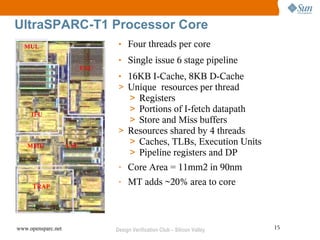

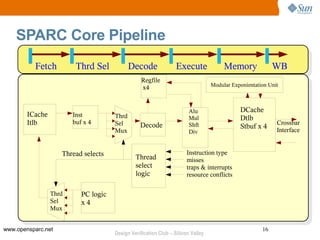

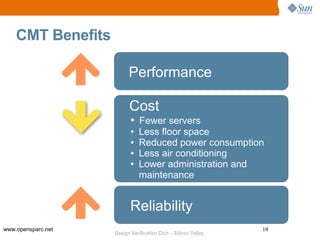

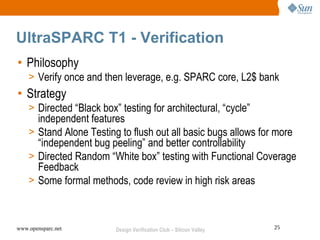

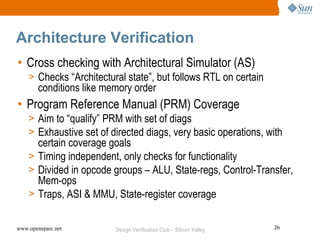

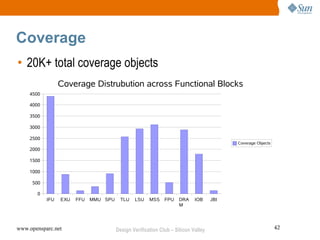

The document discusses Sun Microsystems' UltraSPARC T1 processor. It provides an overview of the processor's features, including its implementation of chip multi-threading with up to 8 cores and 32 threads. It describes the processor's design choices such as shared caches and memory controllers. It also discusses Sun's strategy for verifying the processor's architecture and microarchitecture through directed testing, coverage metrics, and other techniques. Finally, it notes some of the benefits of chip multi-threading for performance, cost, reliability, and power efficiency.

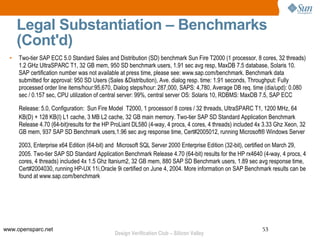

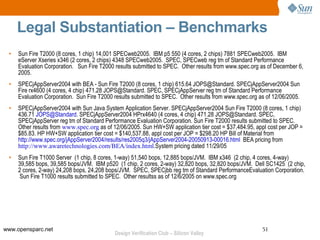

![Legal Substantiation – Benchmarks

(Cont'd)

• NotesBench R6iNotes Sun Fire T2000 (1x1200 MHz UltraSPARC T1, 32GB), 4 partitions, Solaris[TM] 10, Lotus[R] Domino

7.0, 19,000 users, $4.36 per user, 16,061 NotesMark tpm, 400 ms avg rt. NotesBench R6iNotes IBM x346 (2 x 3.4 GHz

Xeon processors, 8GB), 1 partition, SuSE Linux 8, Lotus[R] DominoR6.5.3, 6,50 users, $9.07 per user, 5,109 NotesMark

tpm, 569 ms avg rt.More info www.notesbench.org

• Portal tests conducted on Sun Fire Sun Fire T2000 configured with 6 cores, 1.0GHz UltraSPARC T1 processor and 16GB

memory. Dell 6650 configured with 4 x Intel Xeon processors at 2GHz and 4GB memory. 1 processor was active to run

the test. Internal test using SLAMD Distributed Load Generation Engine AE & Mercury Load Runner. Both systems were

installed with Solaris 10 OS and Sun Java Portal Server 7. Test date: 11/14/05.

• Crypto Processing RSA & DSA sign operations @ 1024-bit

www.opensparc.net 52

Design Verification Club – Silicon Valley](https://image.slidesharecdn.com/shrenikt1verifv3revised-130422130751-phpapp01/85/OpenSPARC-T1-Processor-52-320.jpg)