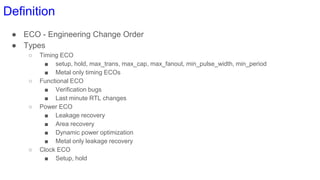

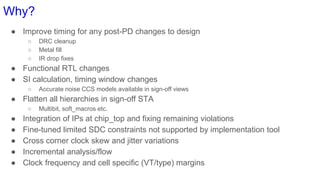

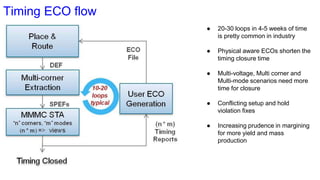

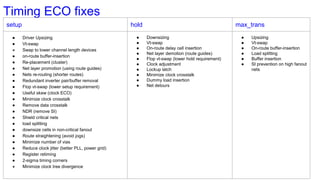

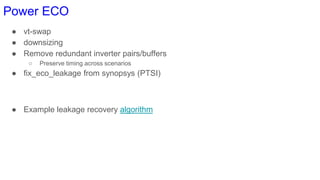

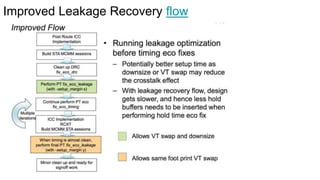

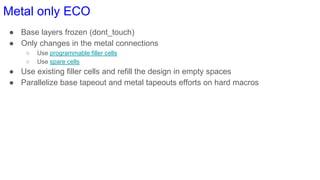

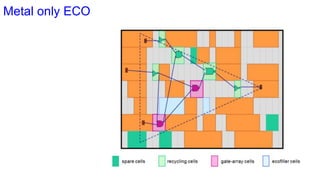

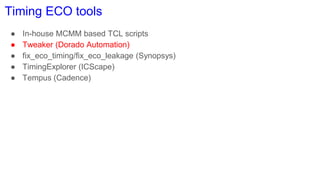

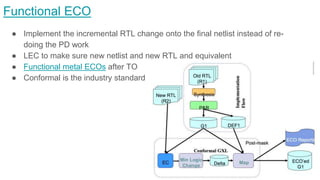

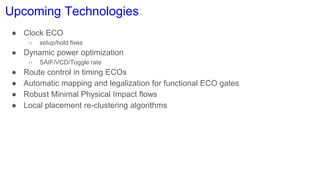

This document discusses engineering change orders (ECOs) used to fix timing, functional, power, and clock issues after physical design and sign-off. It describes the motivation for ECOs due to tool limitations and differences between implementation and sign-off. Common ECO techniques are listed for timing (driver upsizing, buffer insertion, etc.), power (vt-swapping, downsizing, etc.), and metal-only ECOs. Timing ECO tools from Synopsys, Cadence, and other vendors are also mentioned. Upcoming ECO technologies like dynamic power optimization and automatic legalization are noted.