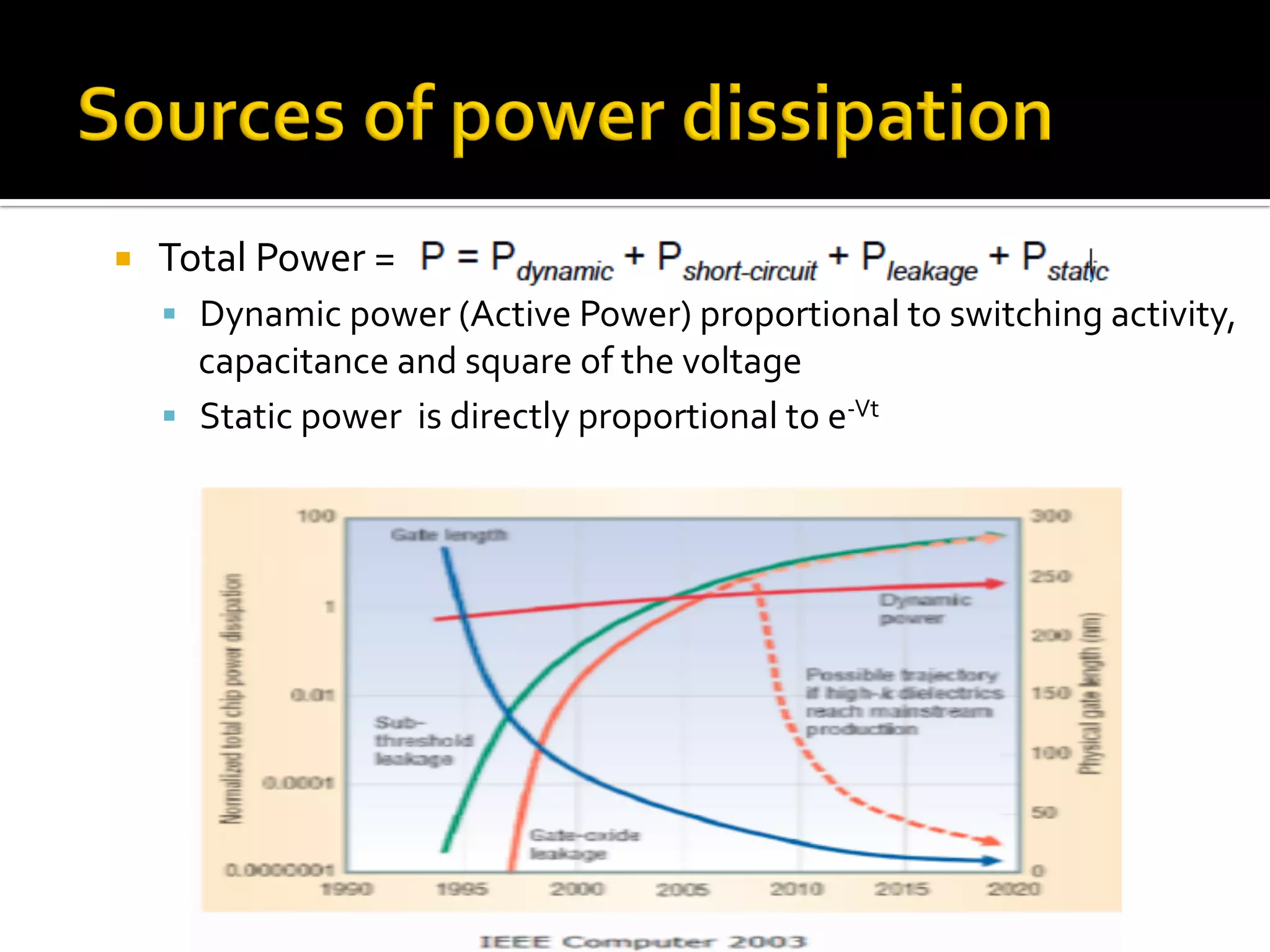

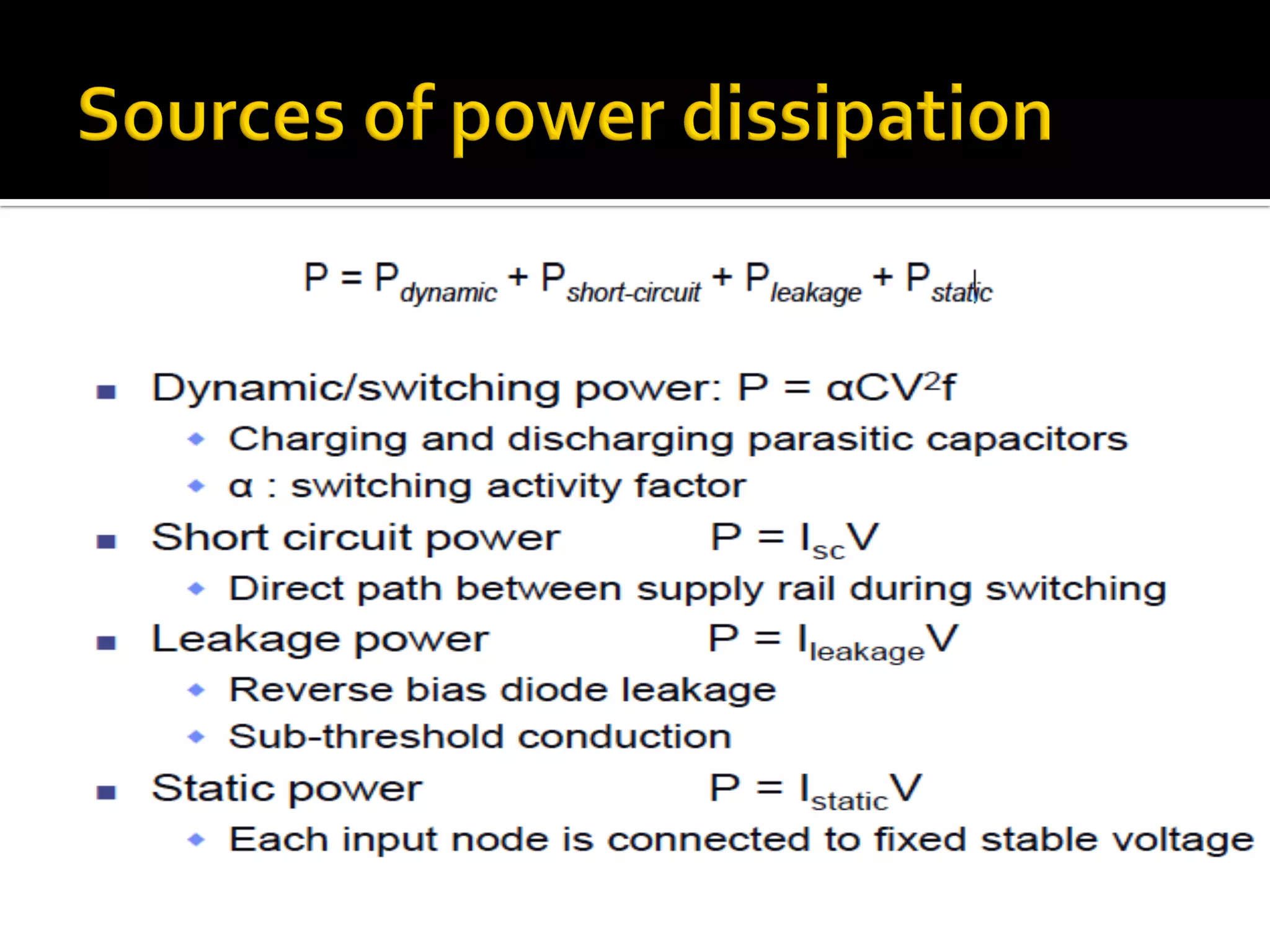

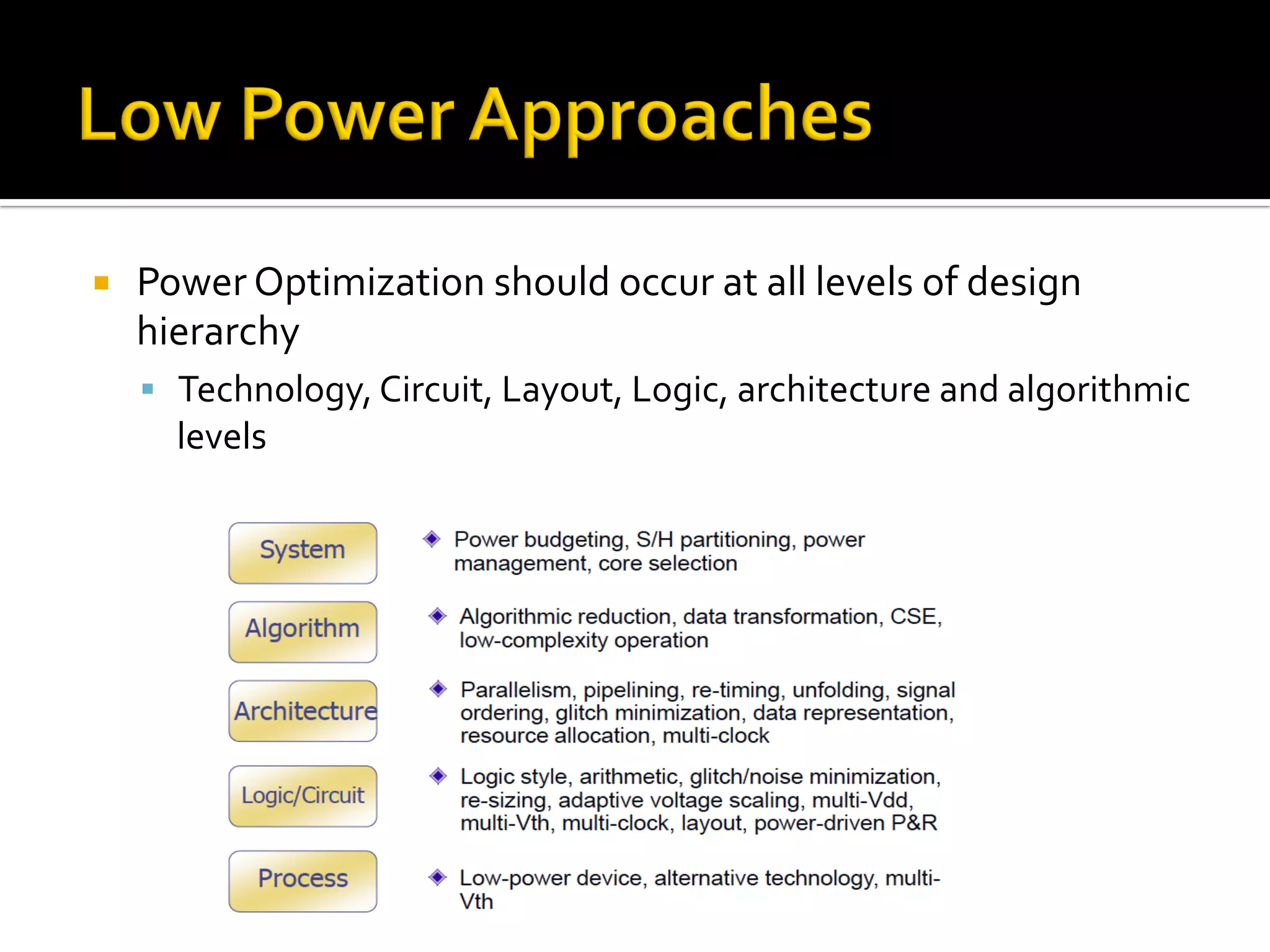

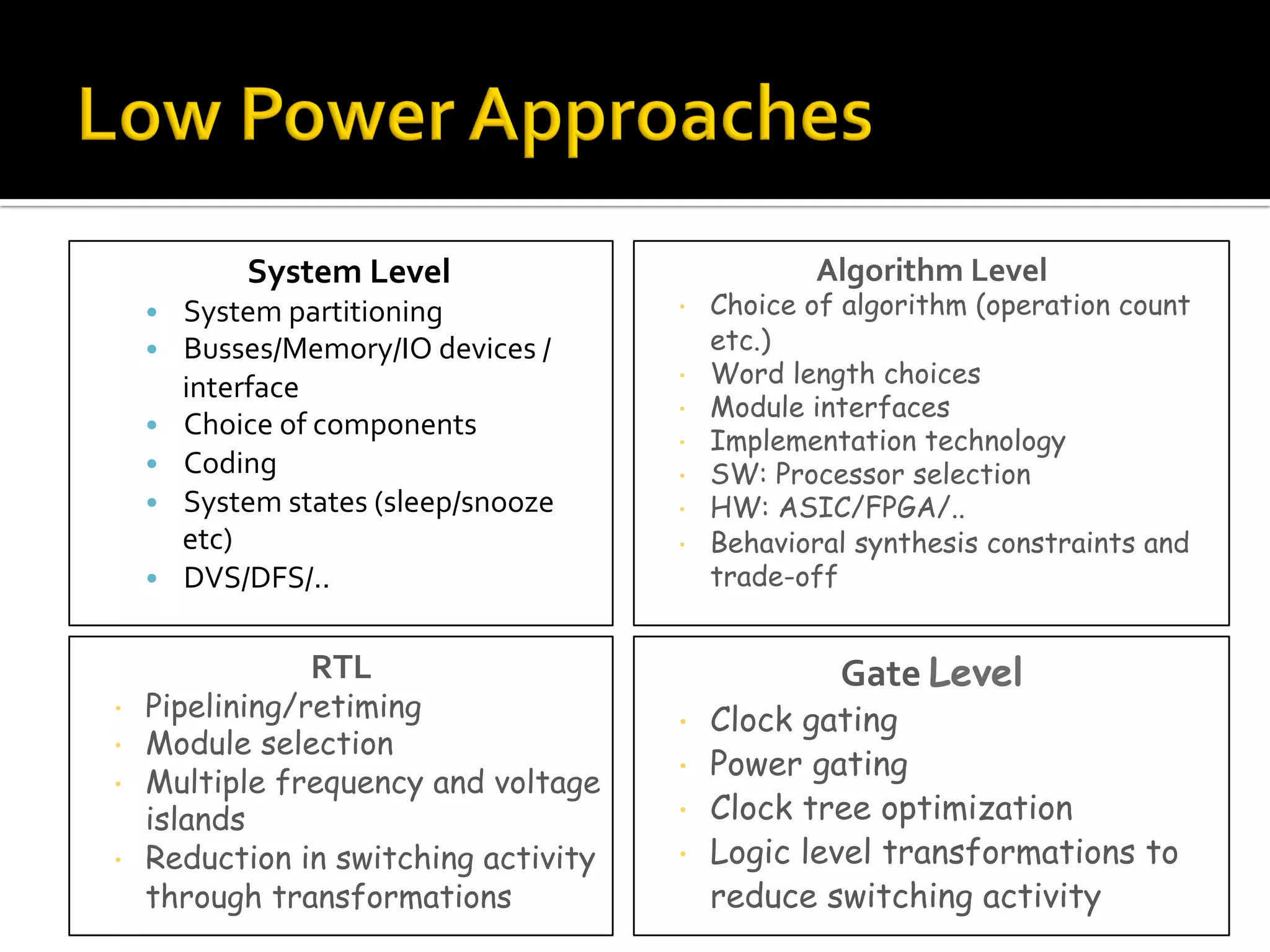

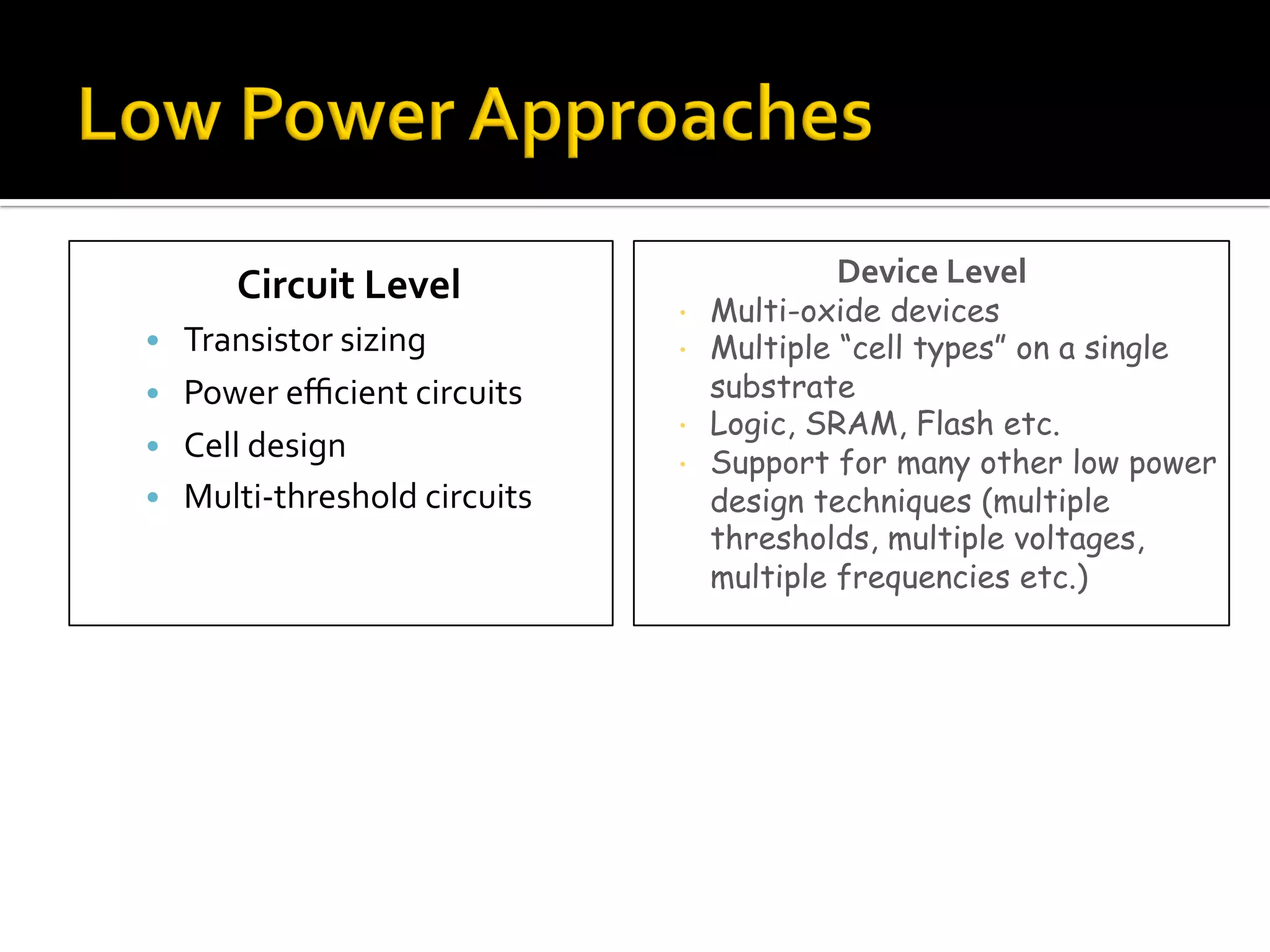

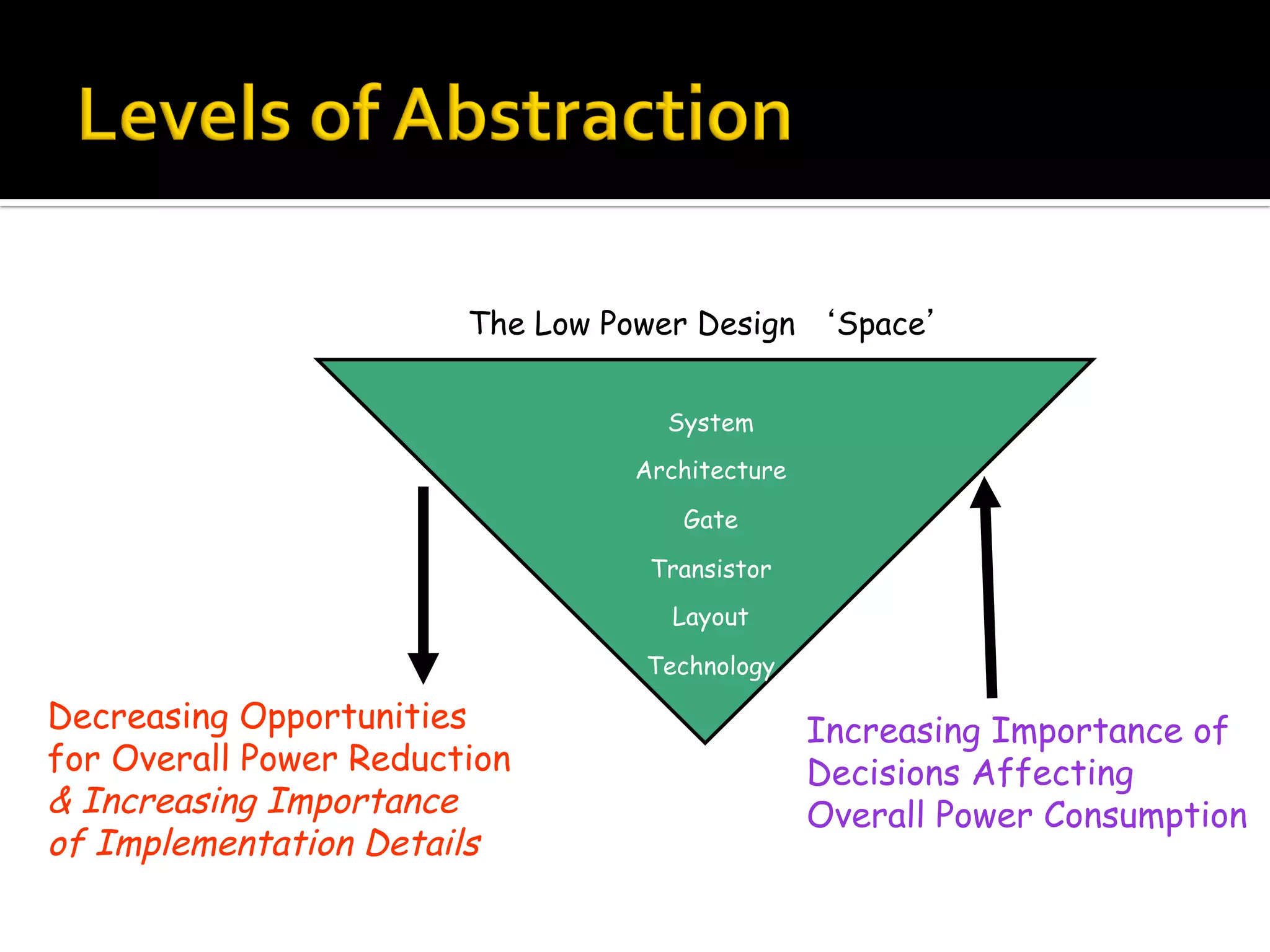

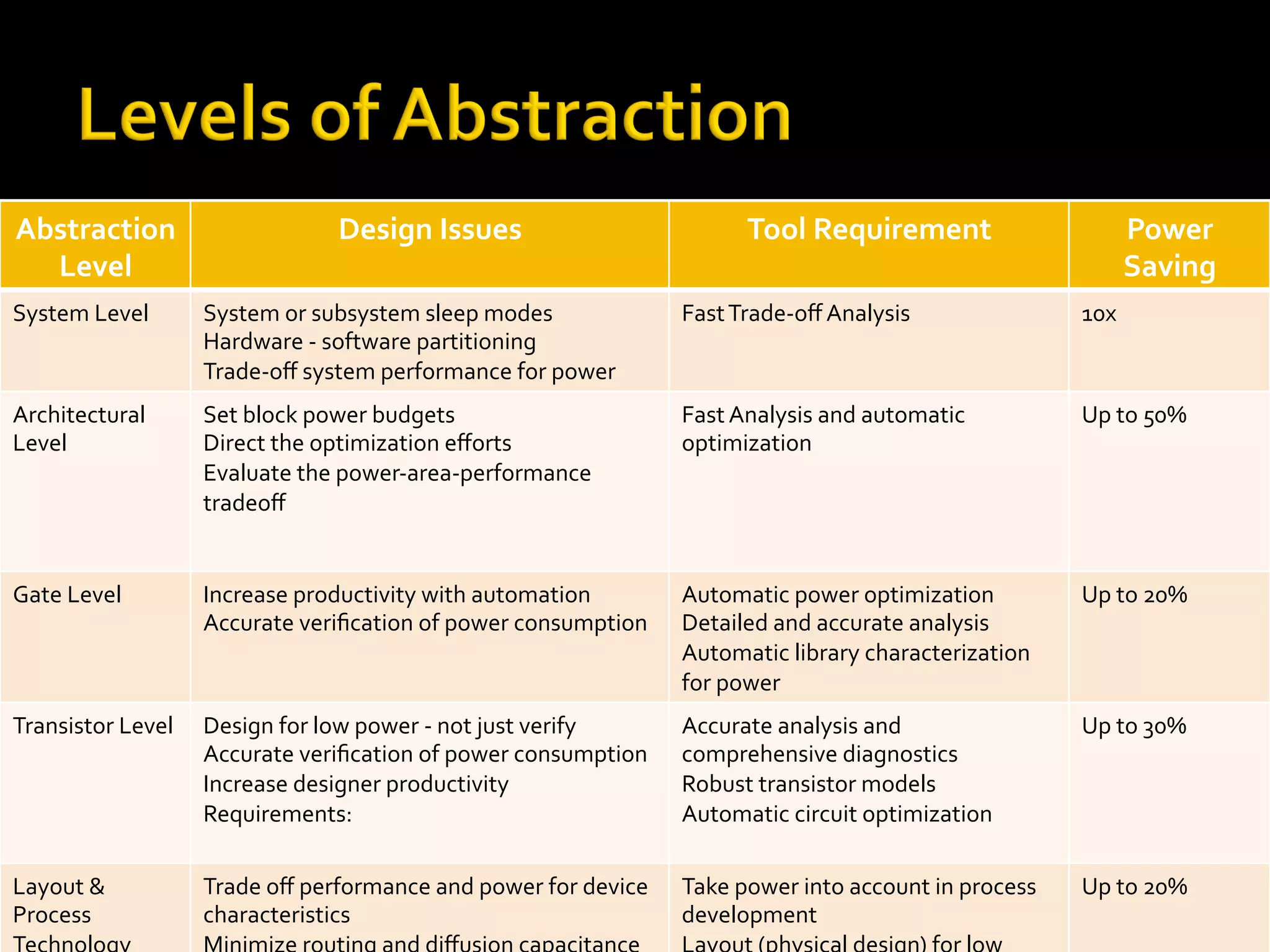

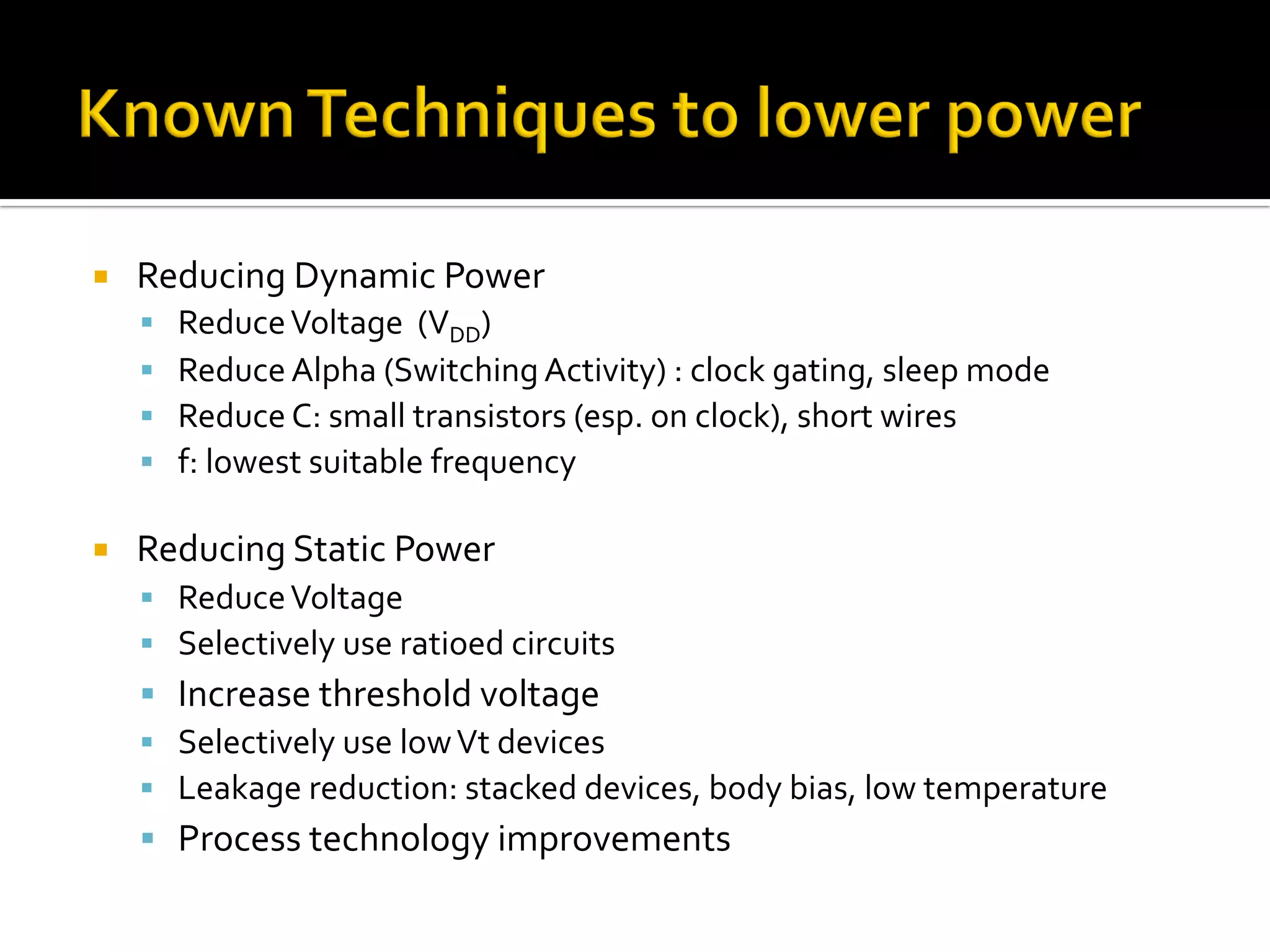

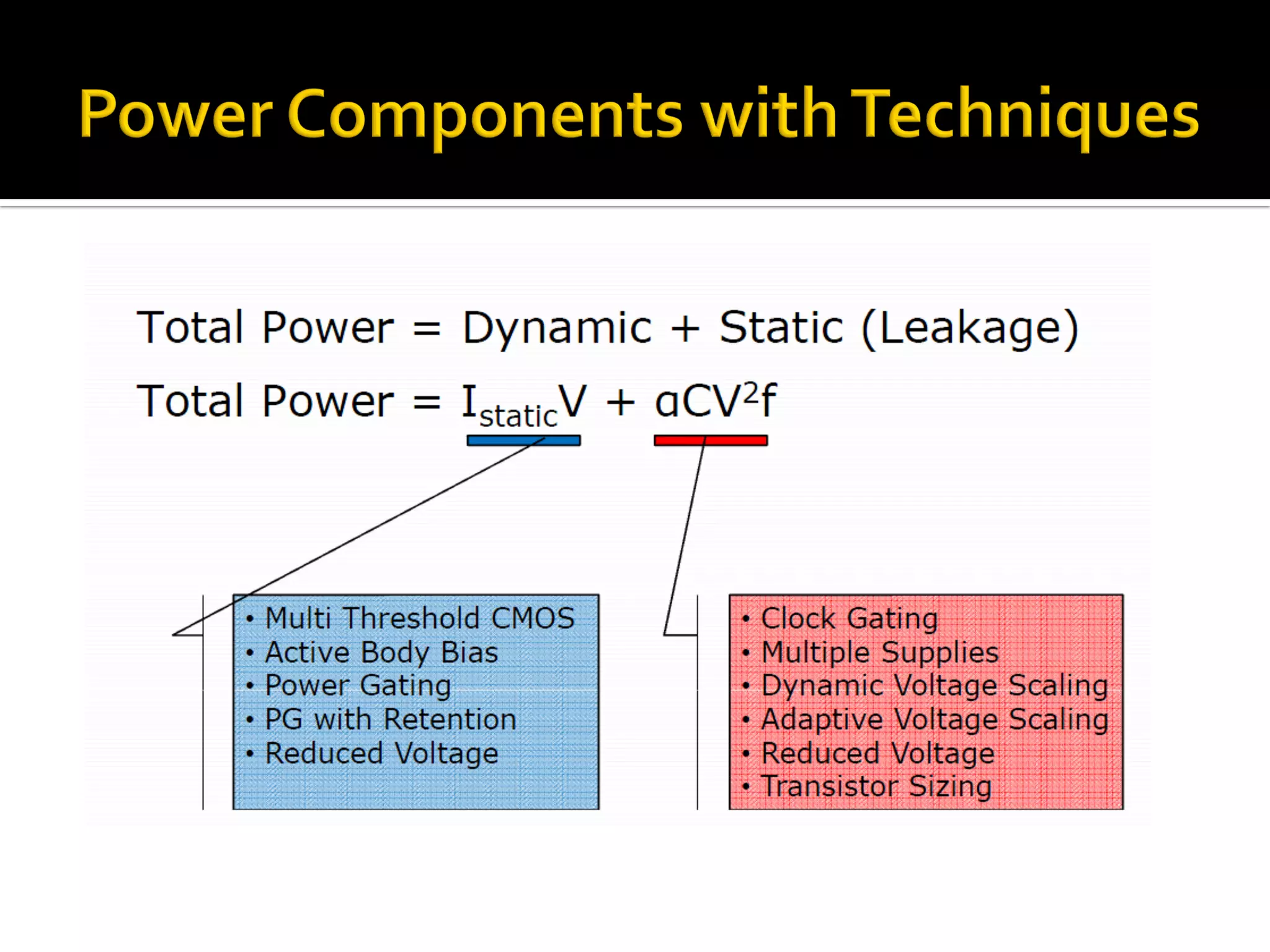

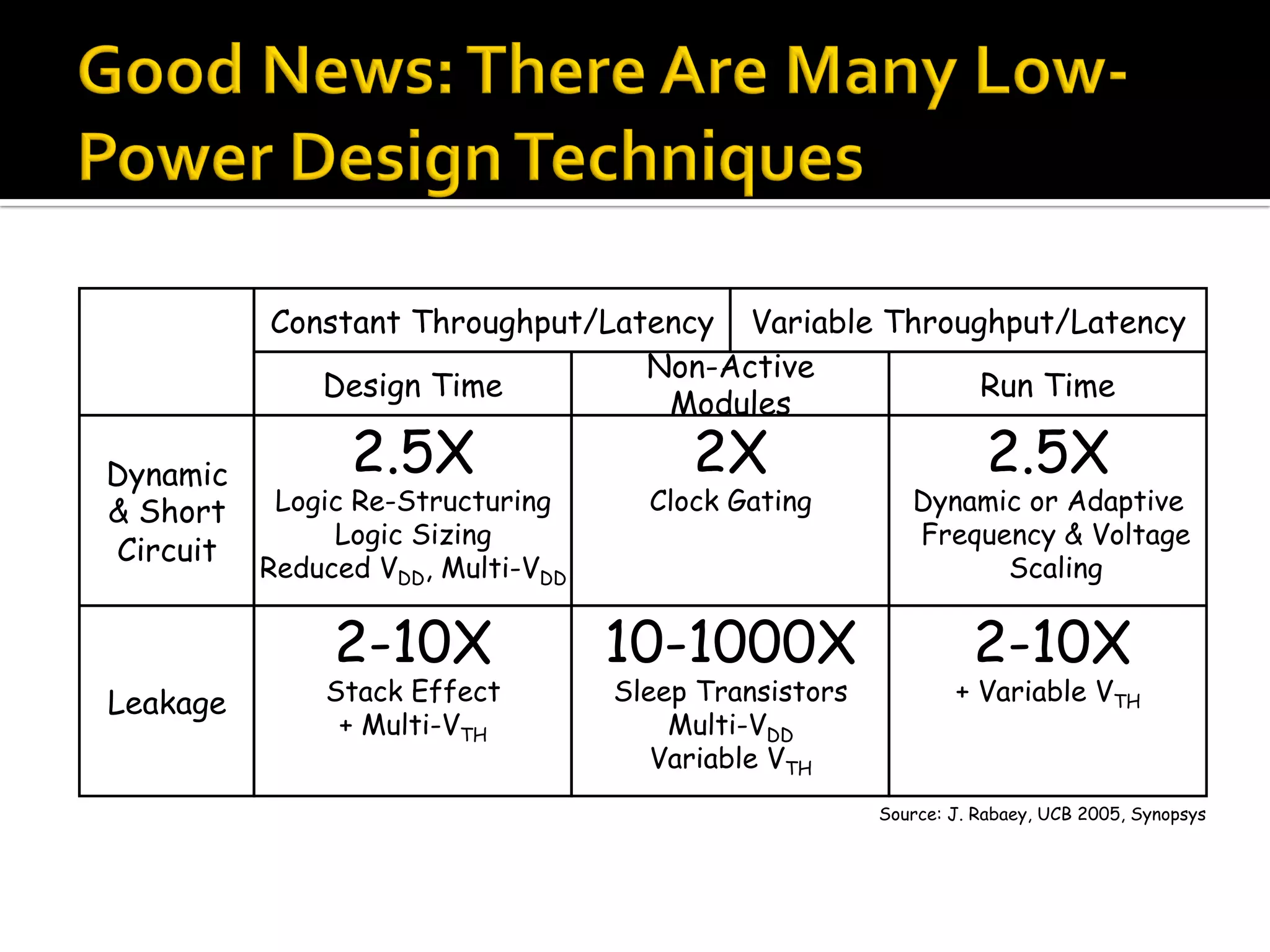

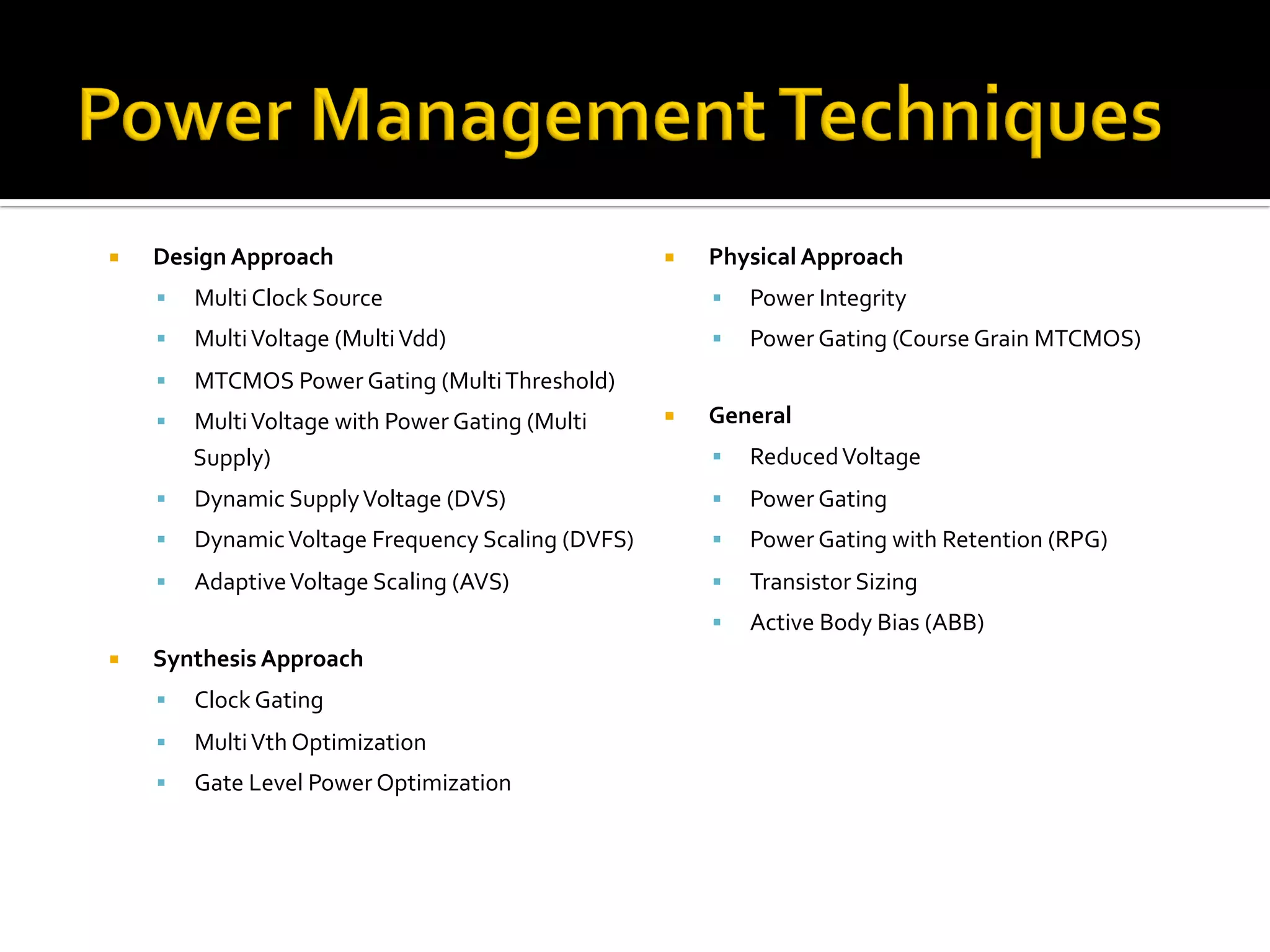

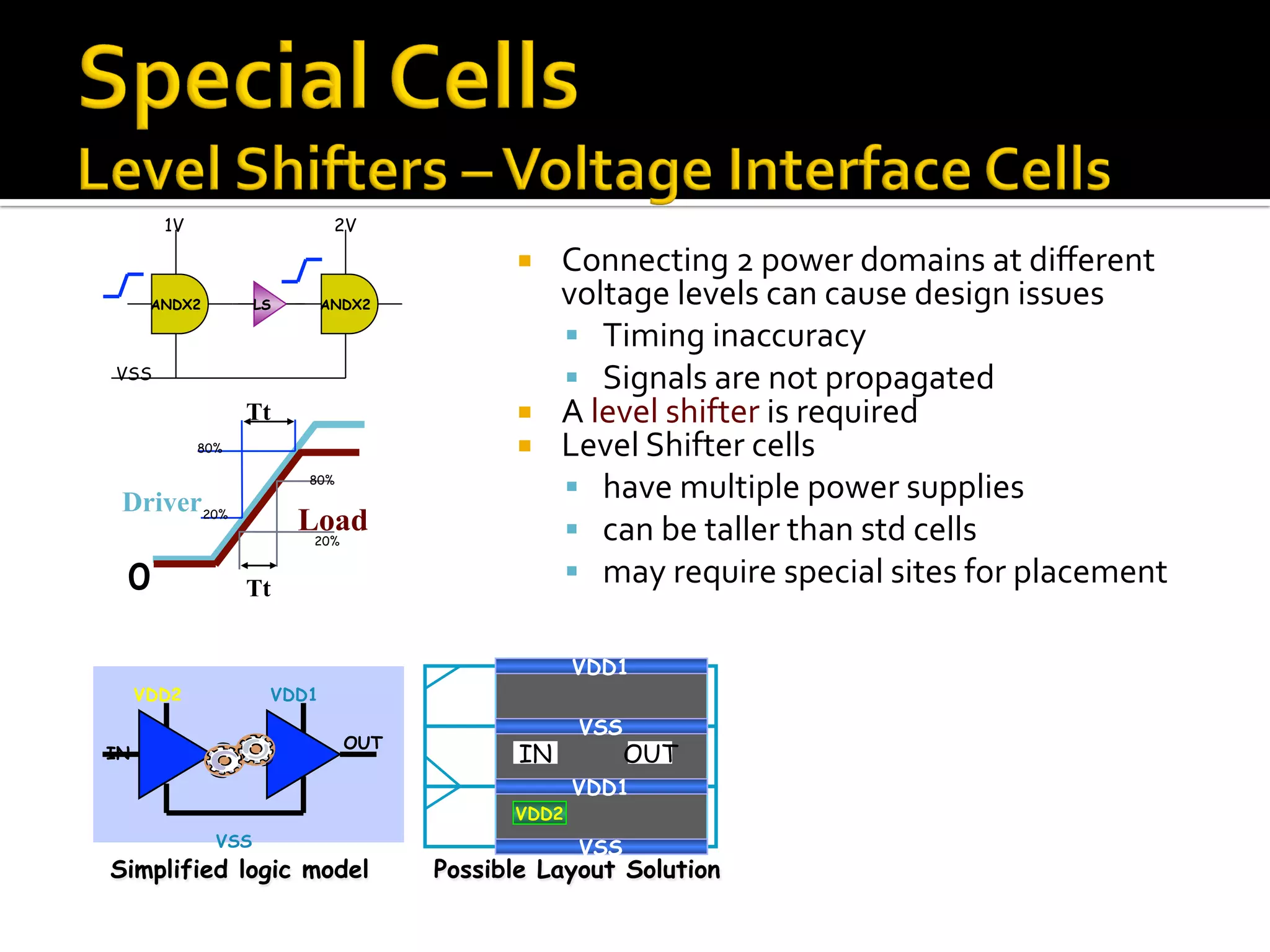

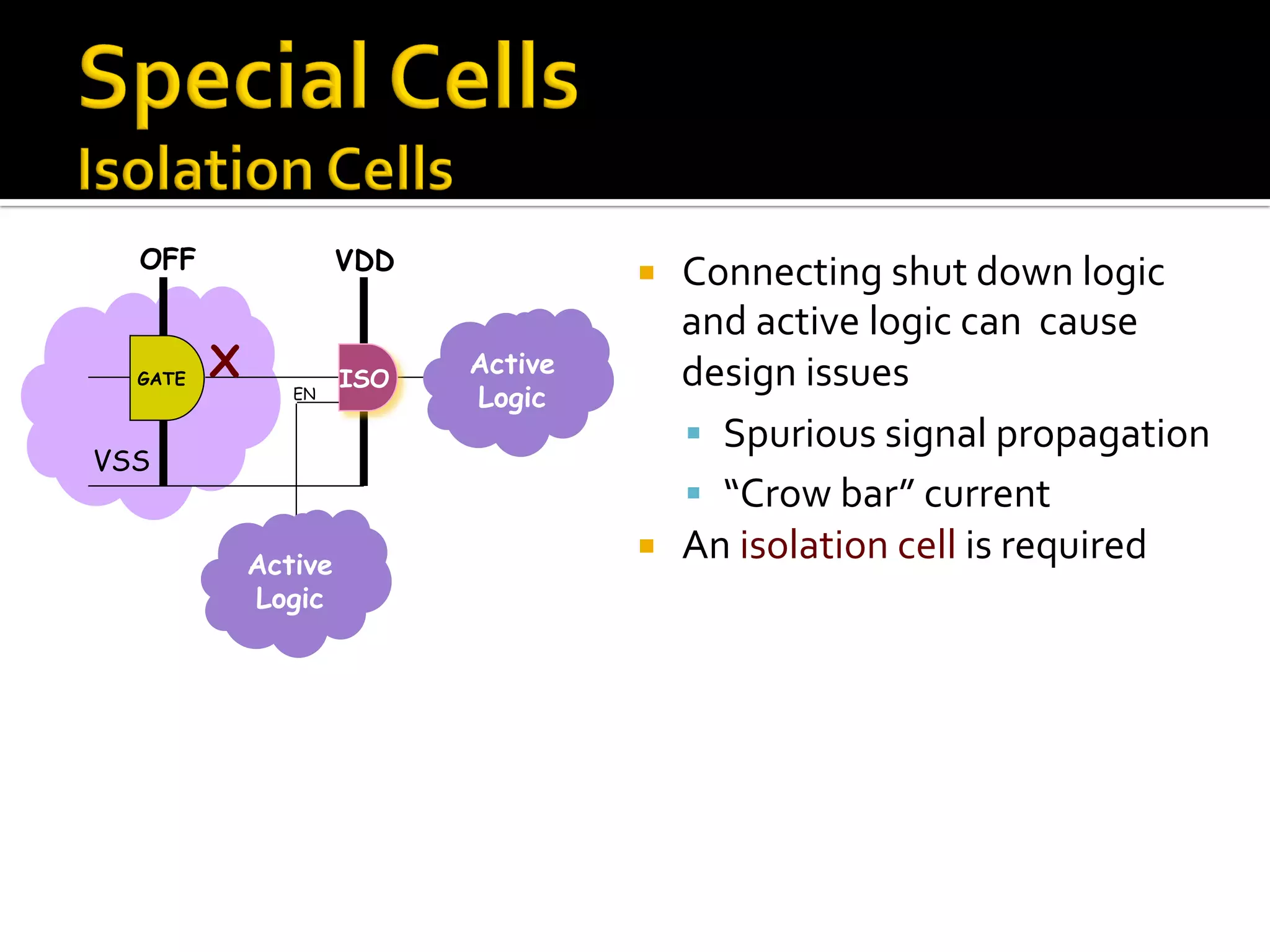

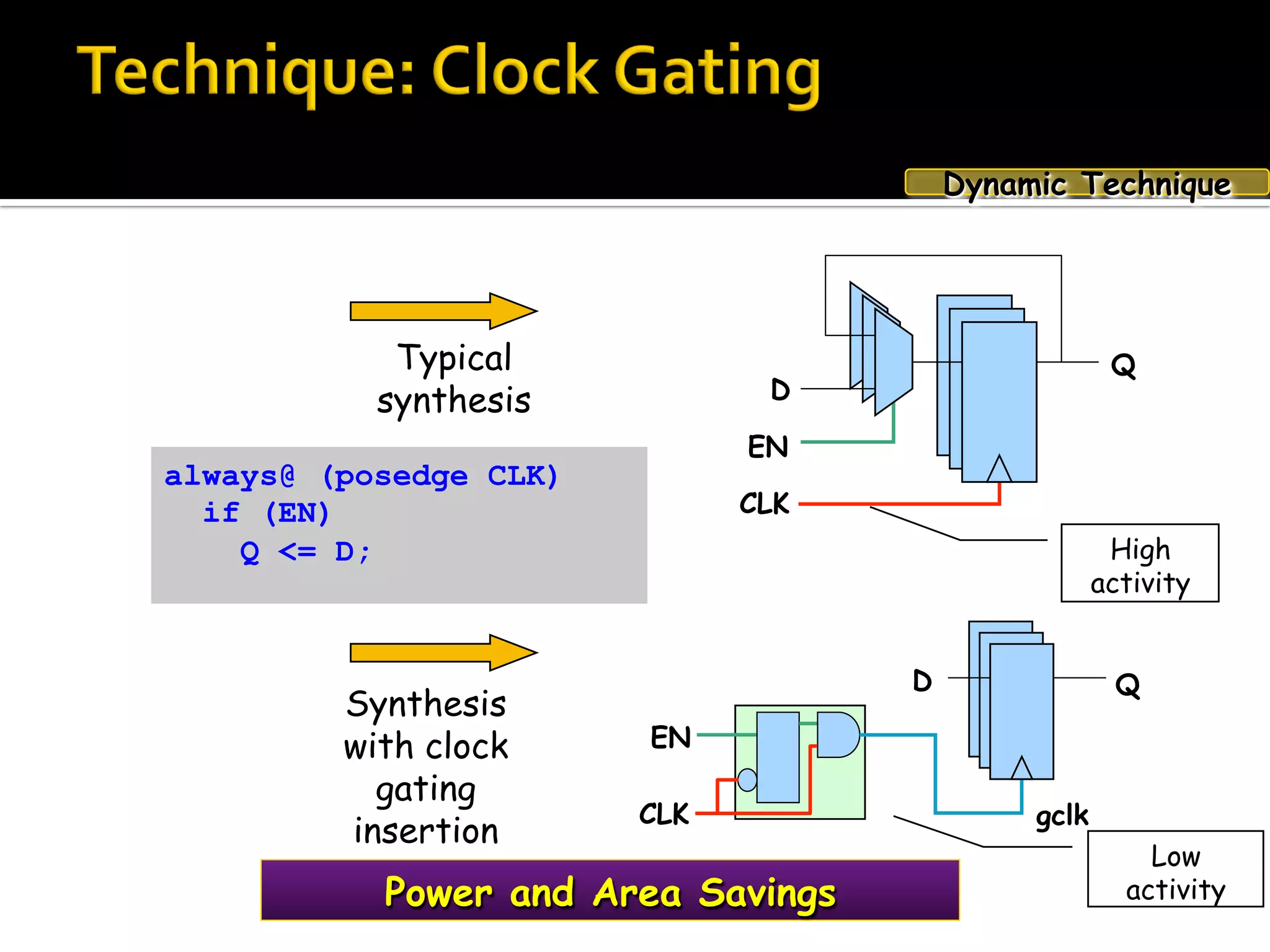

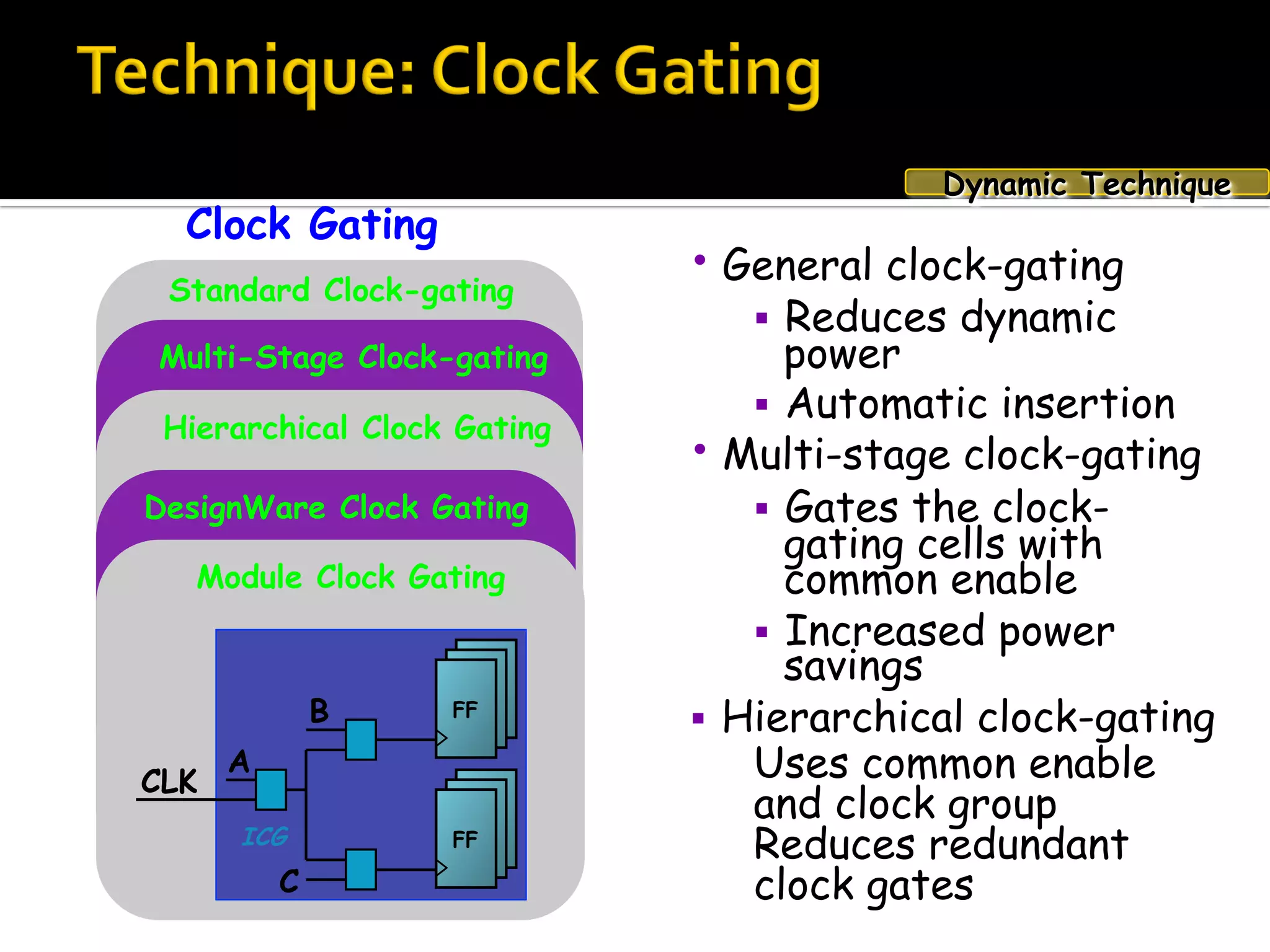

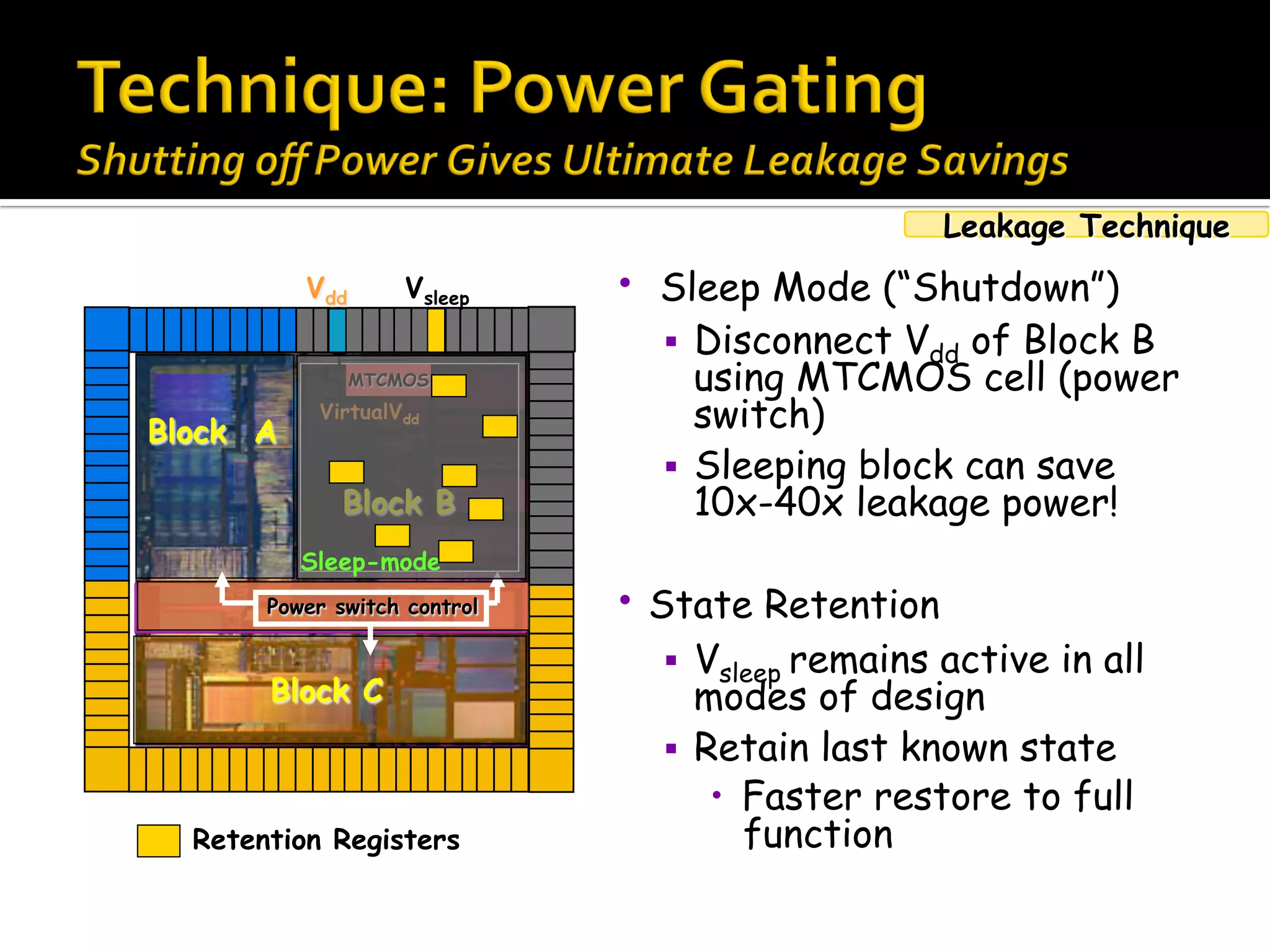

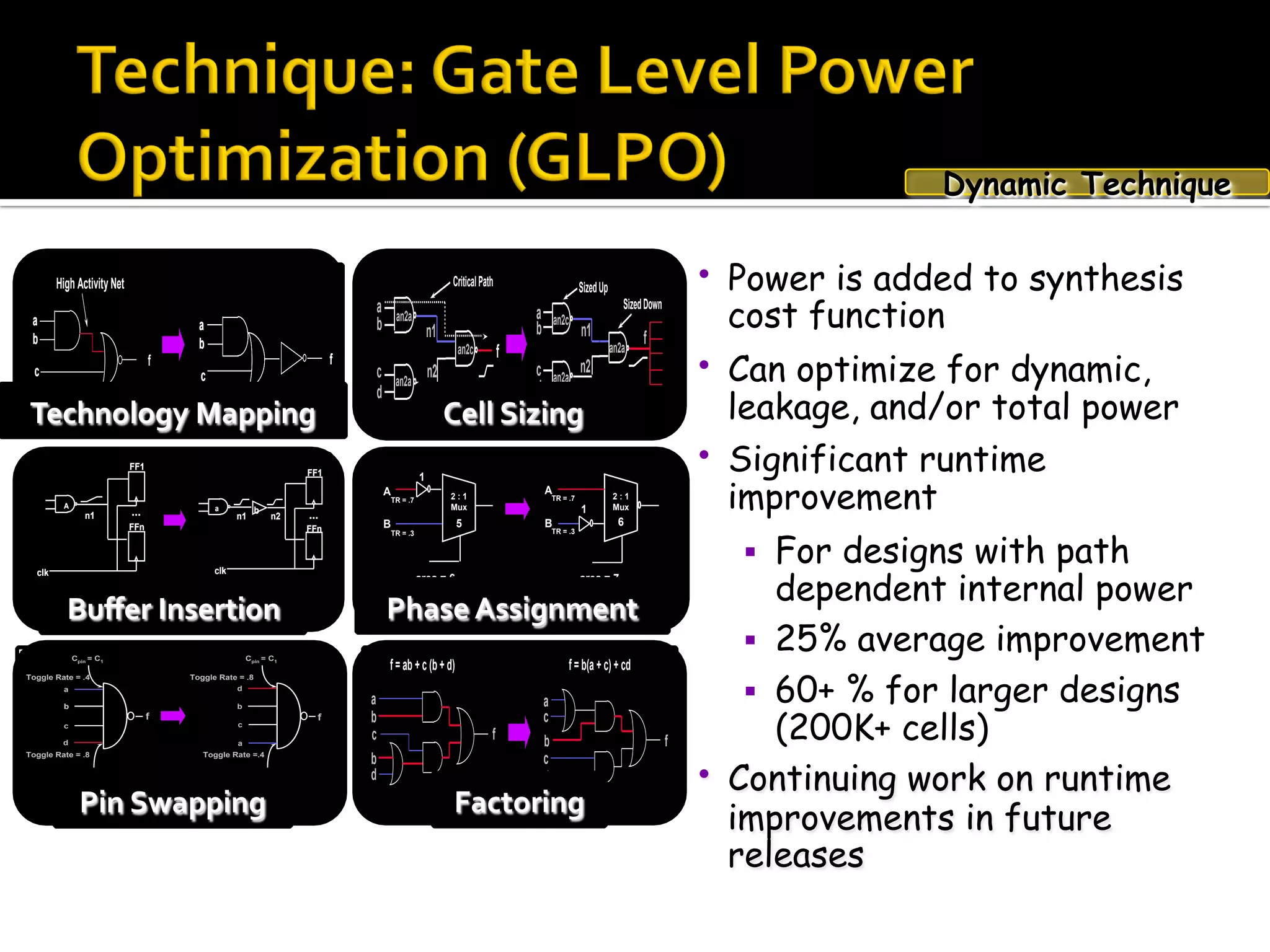

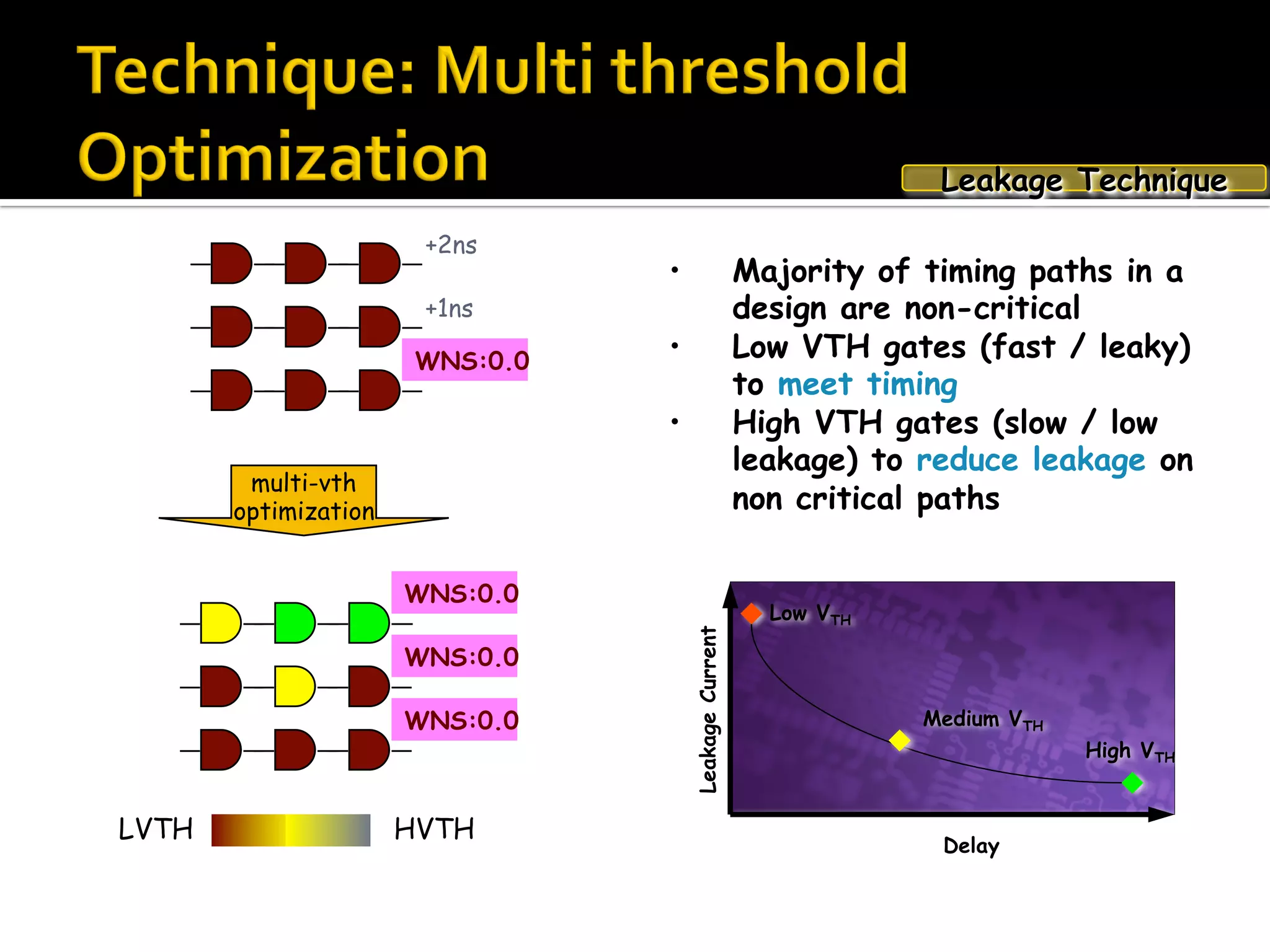

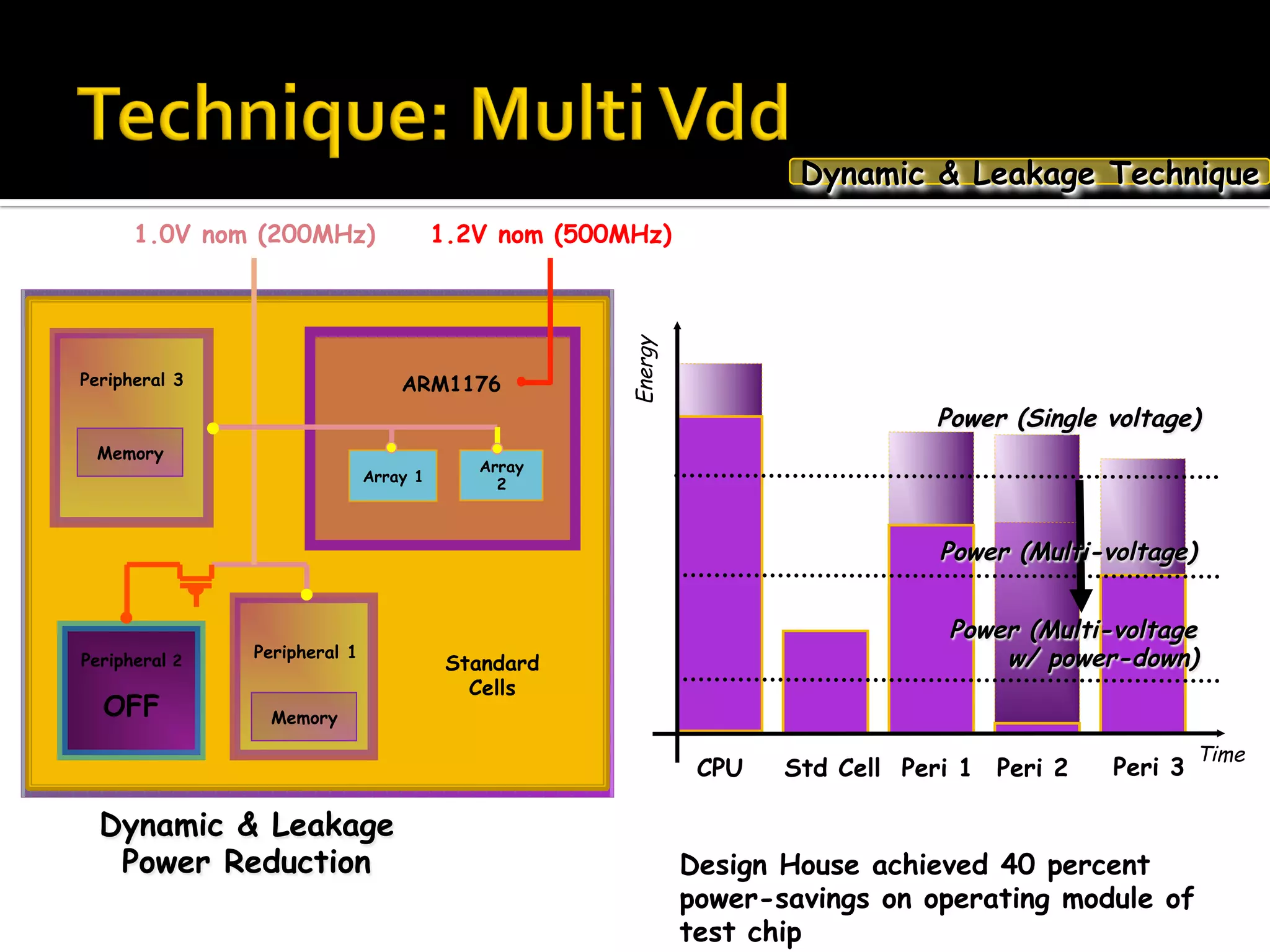

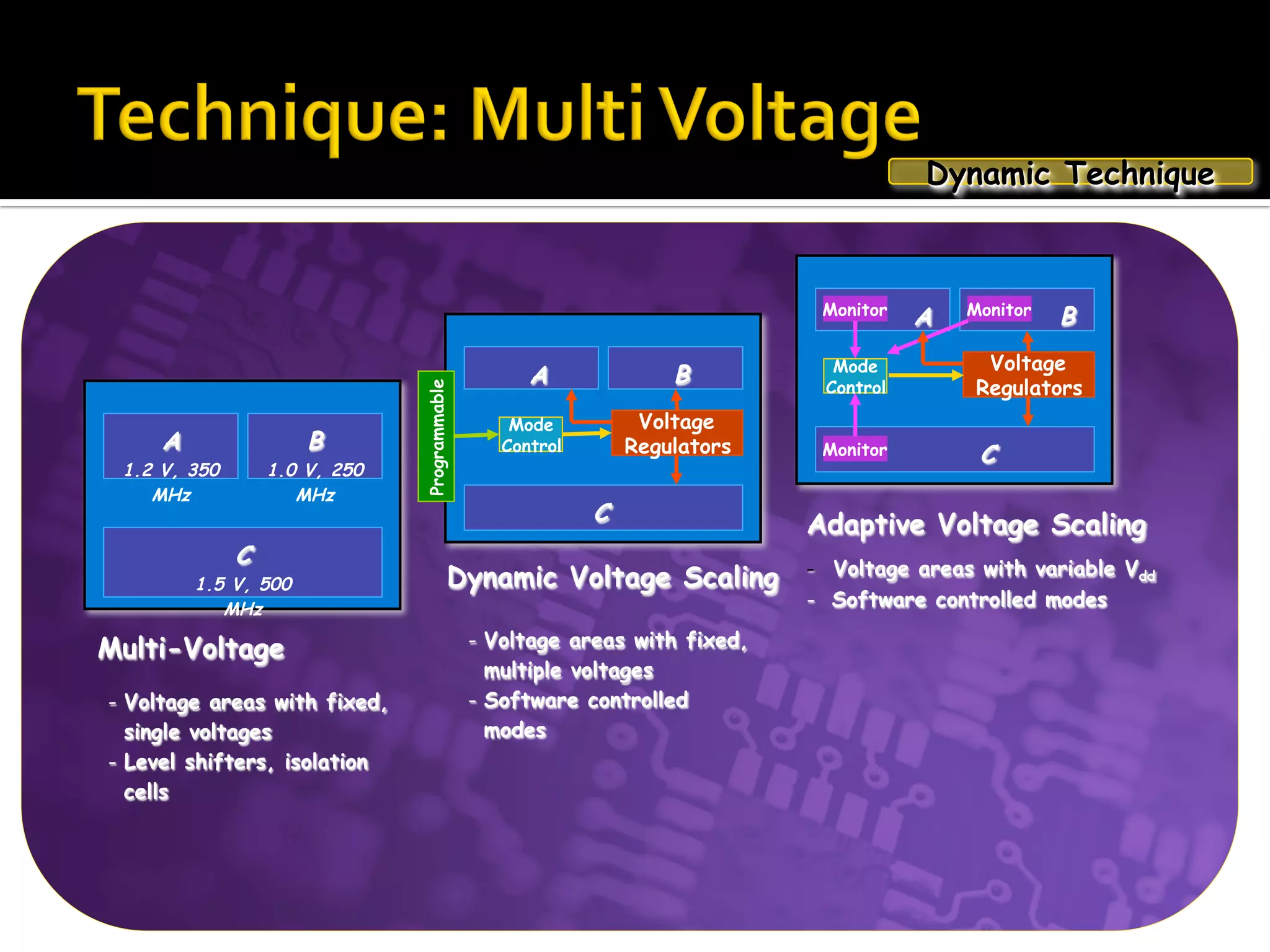

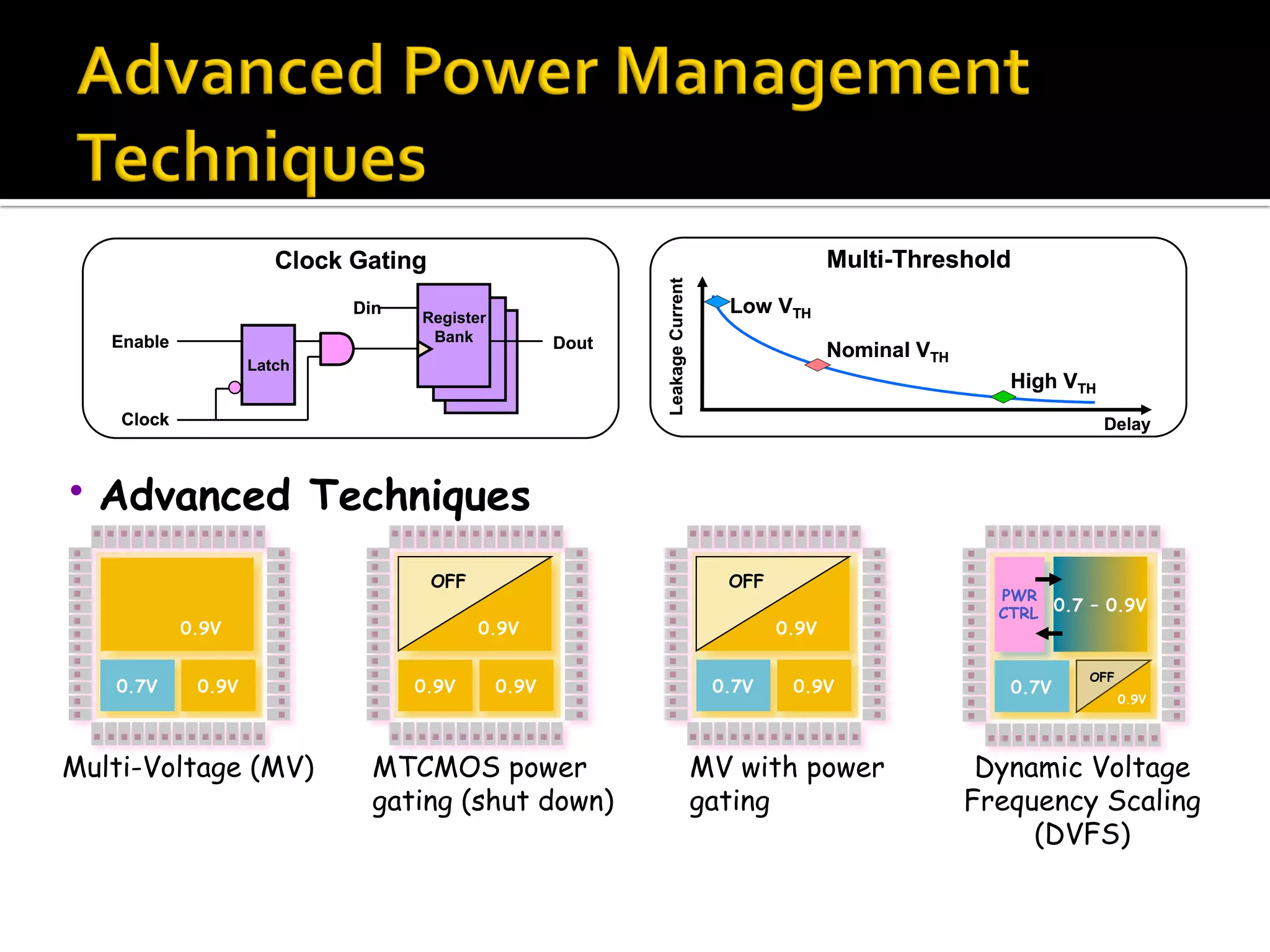

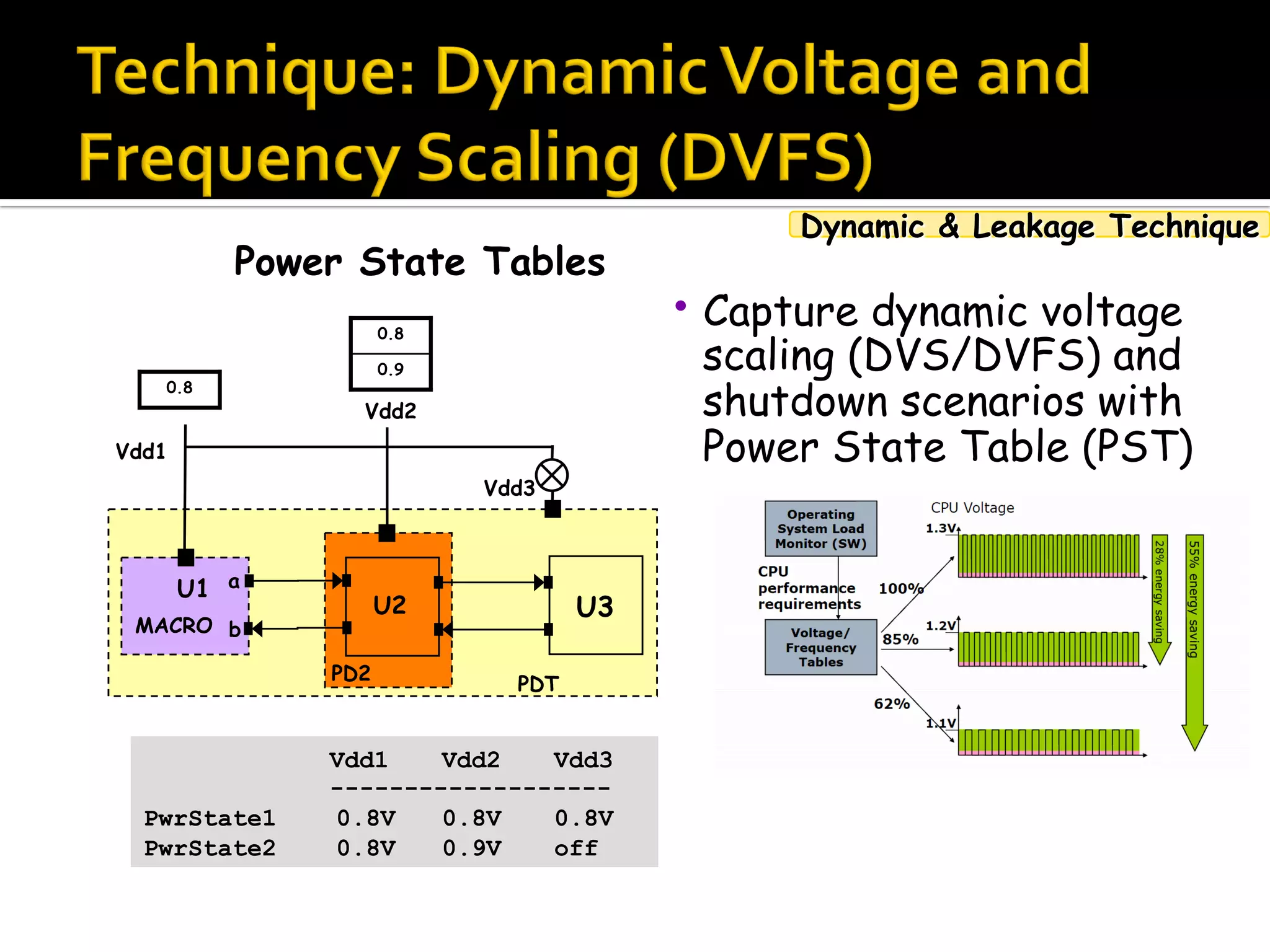

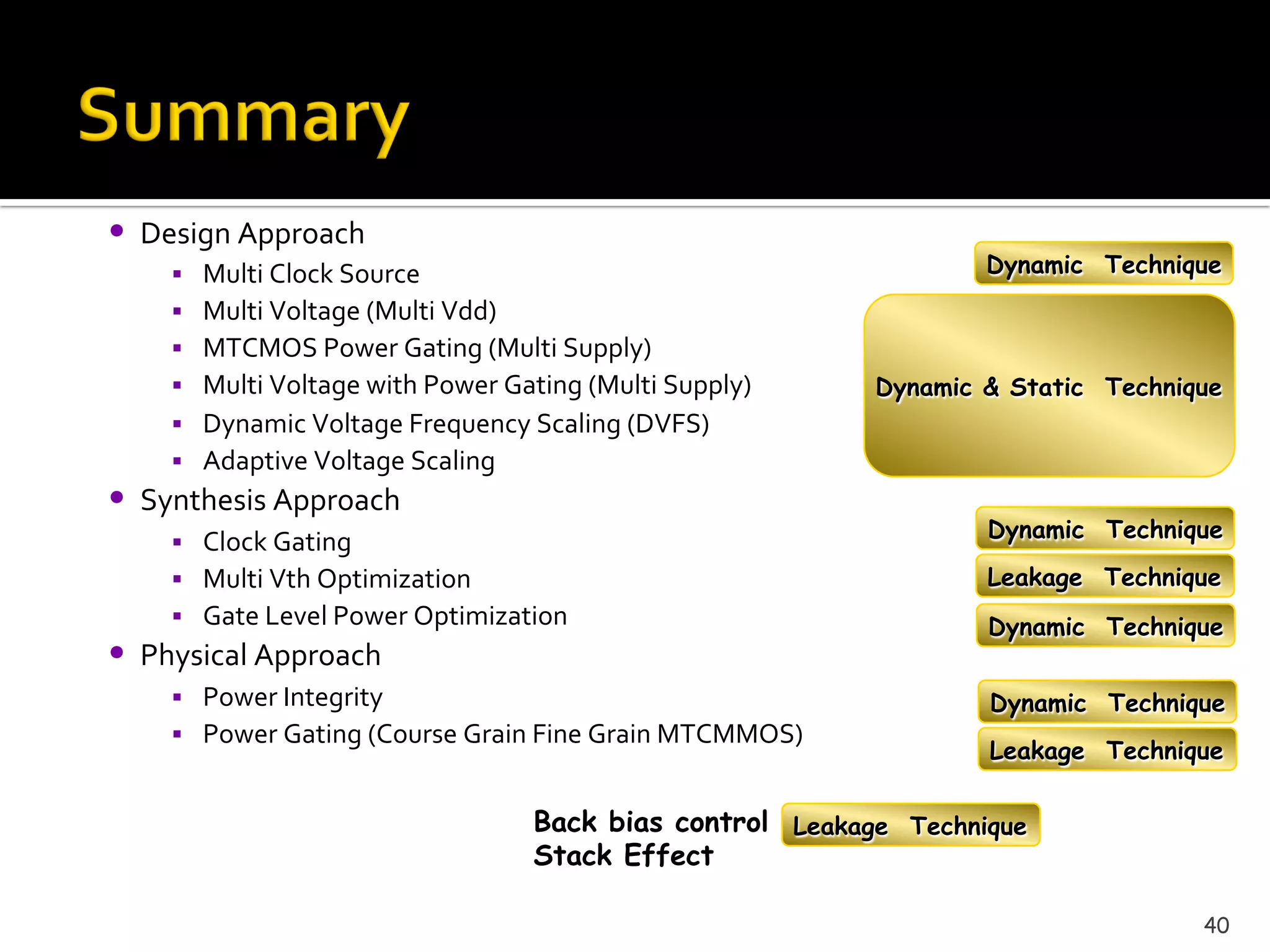

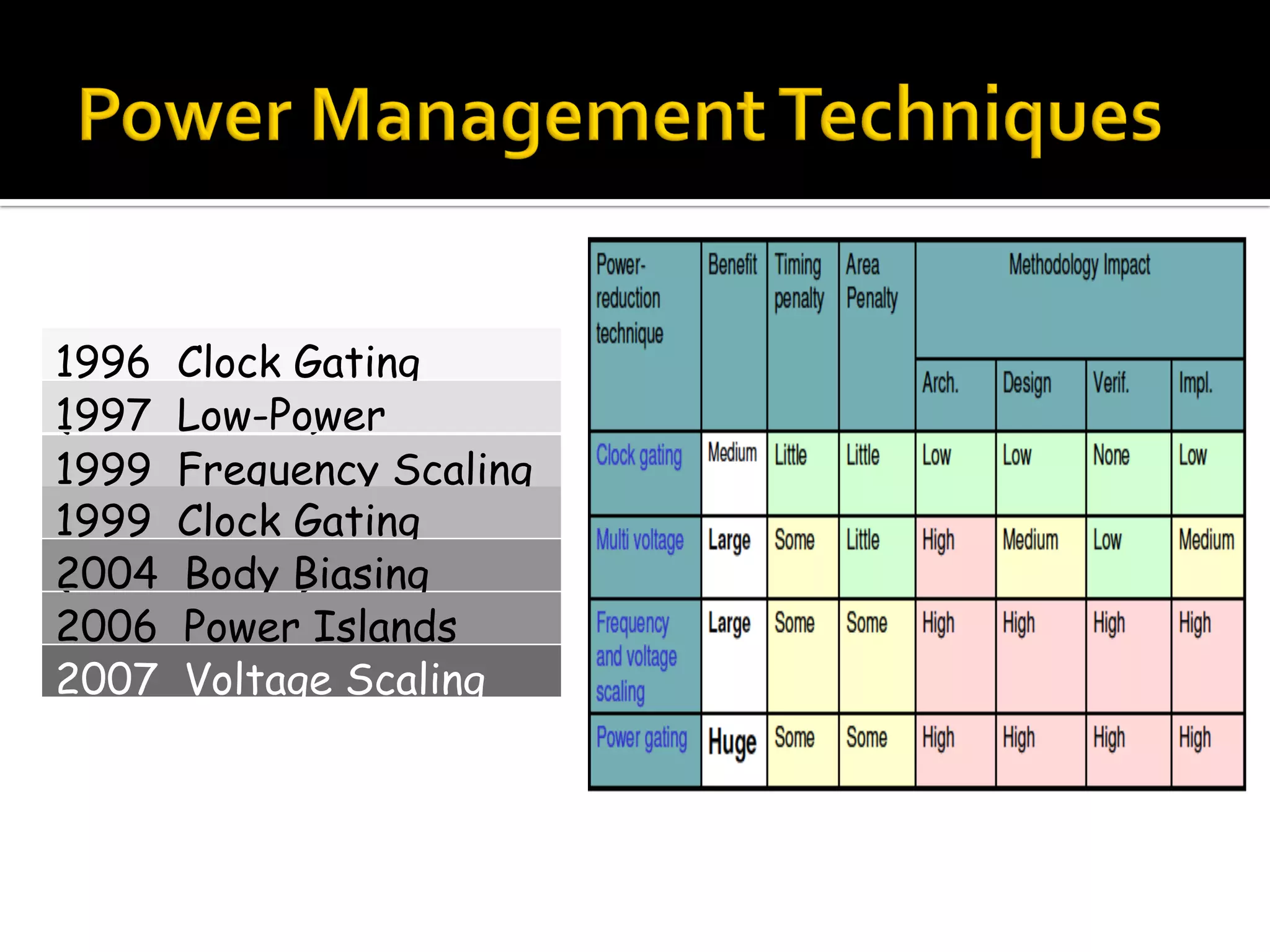

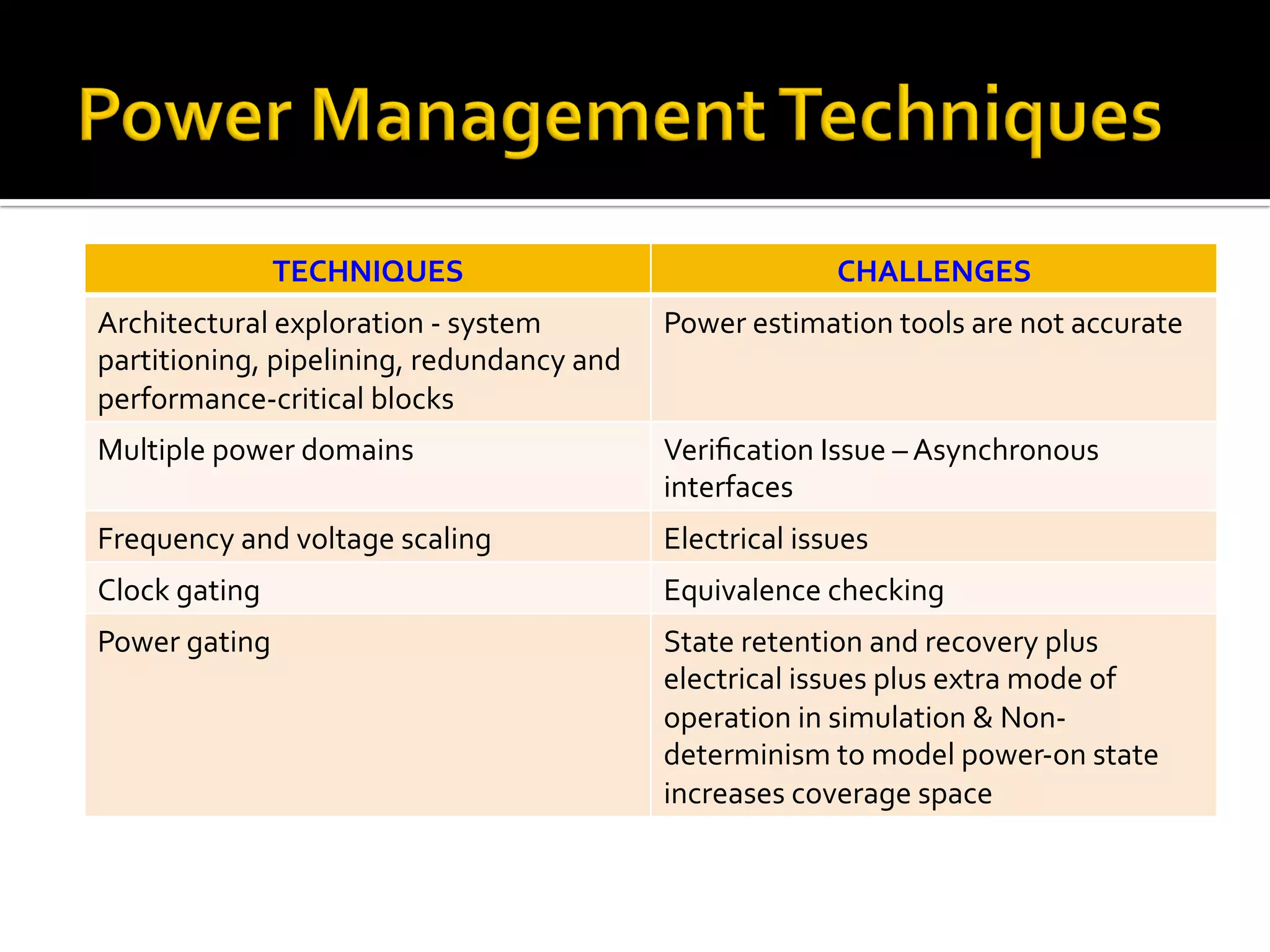

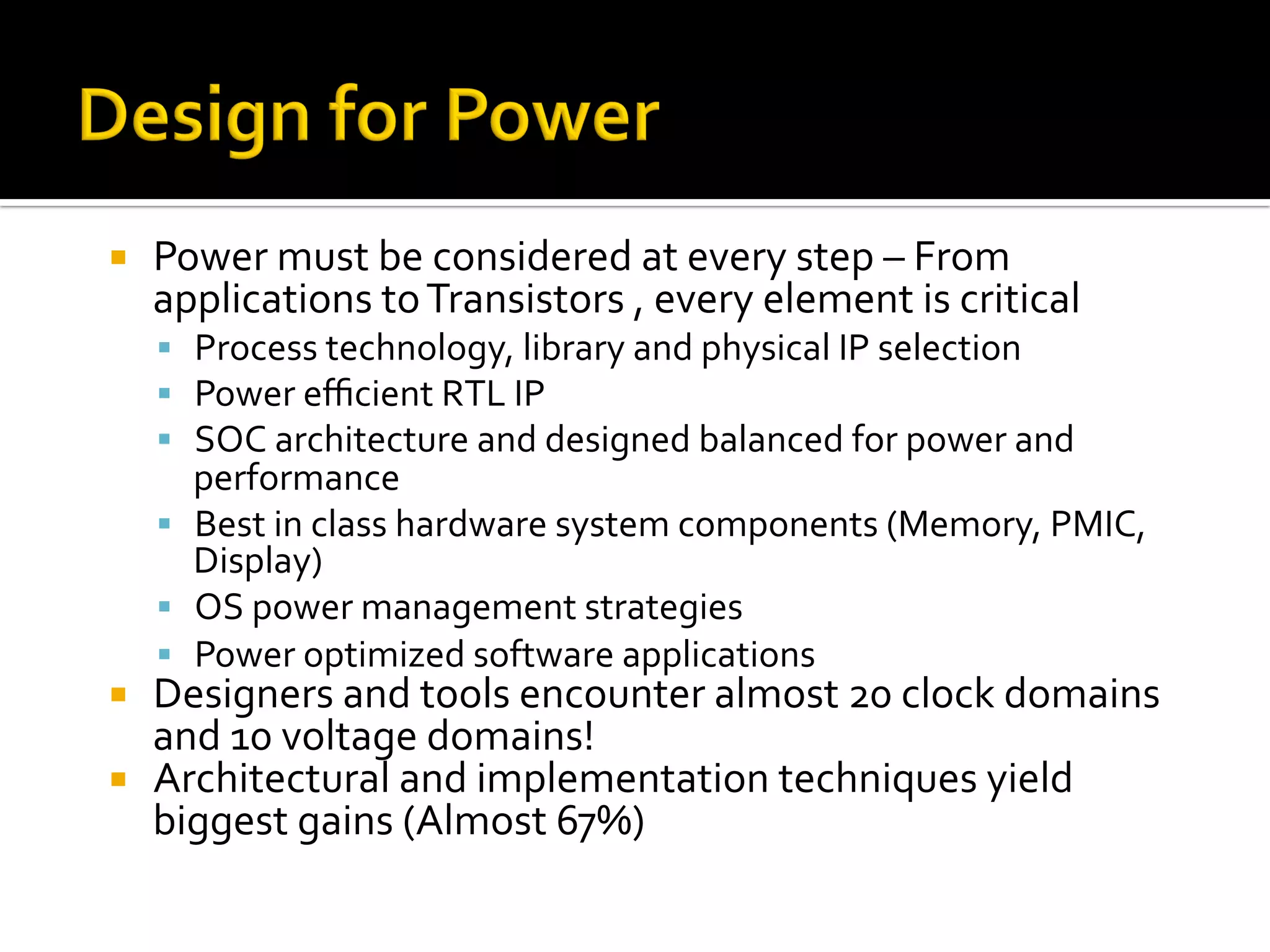

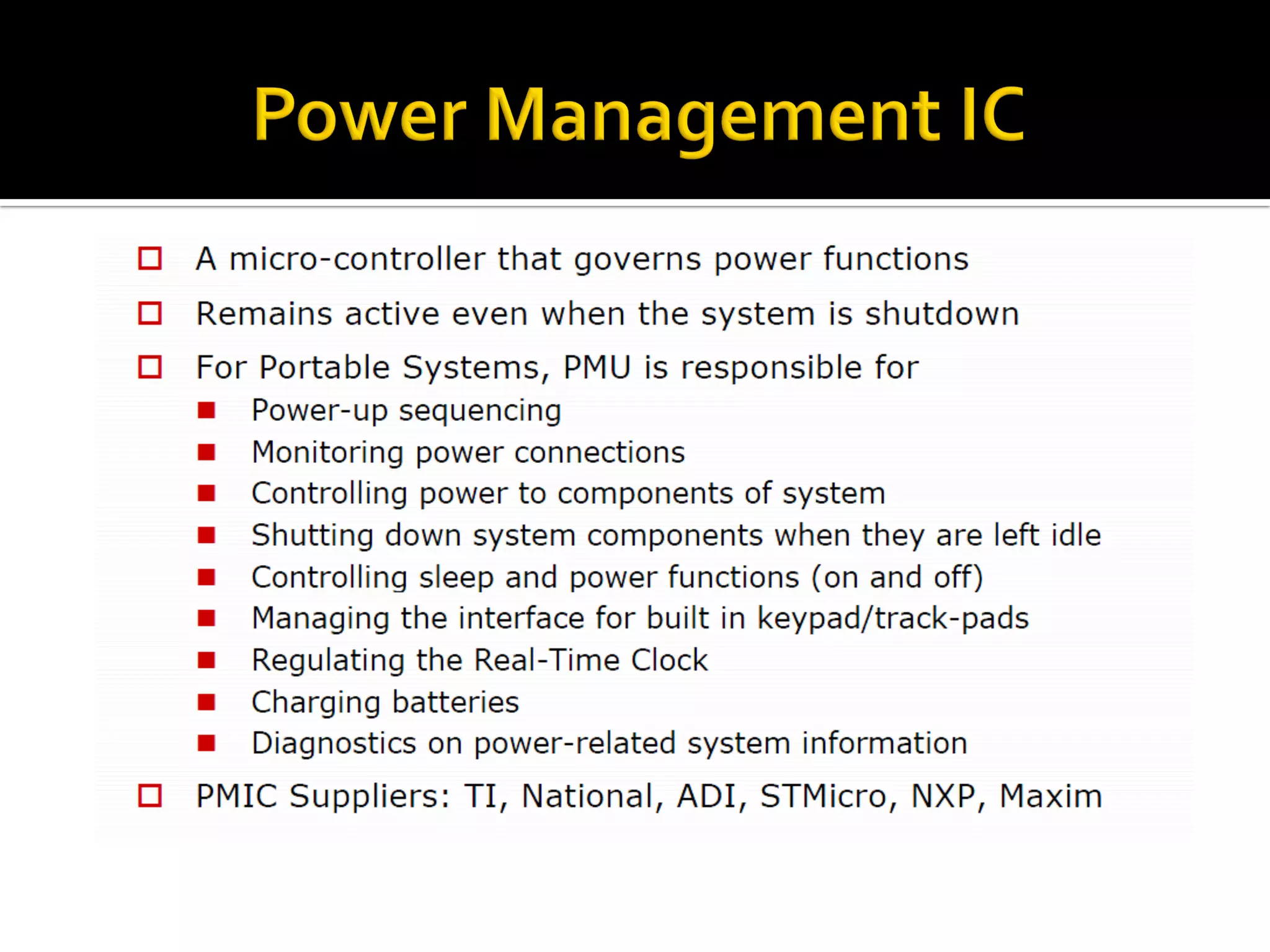

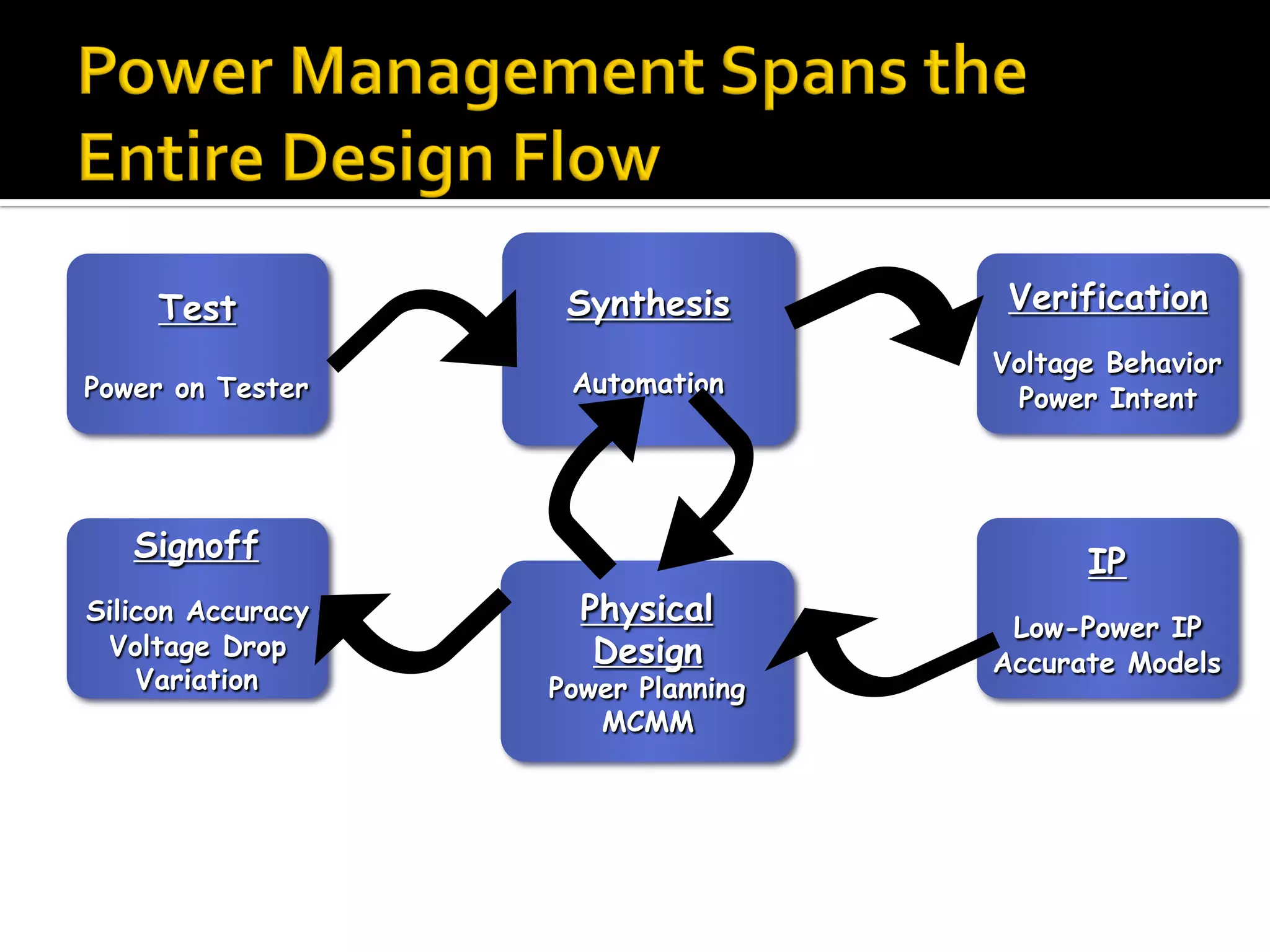

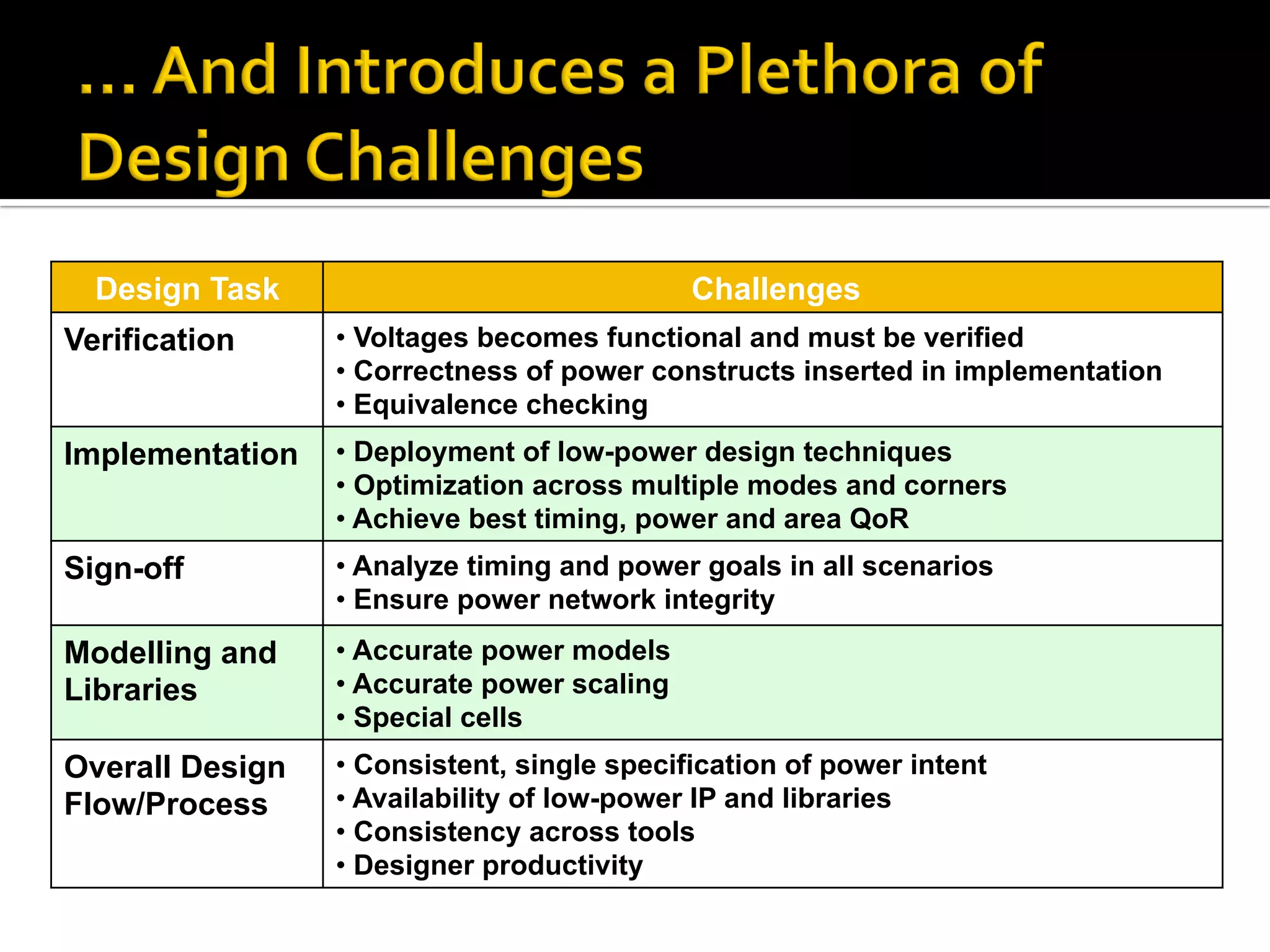

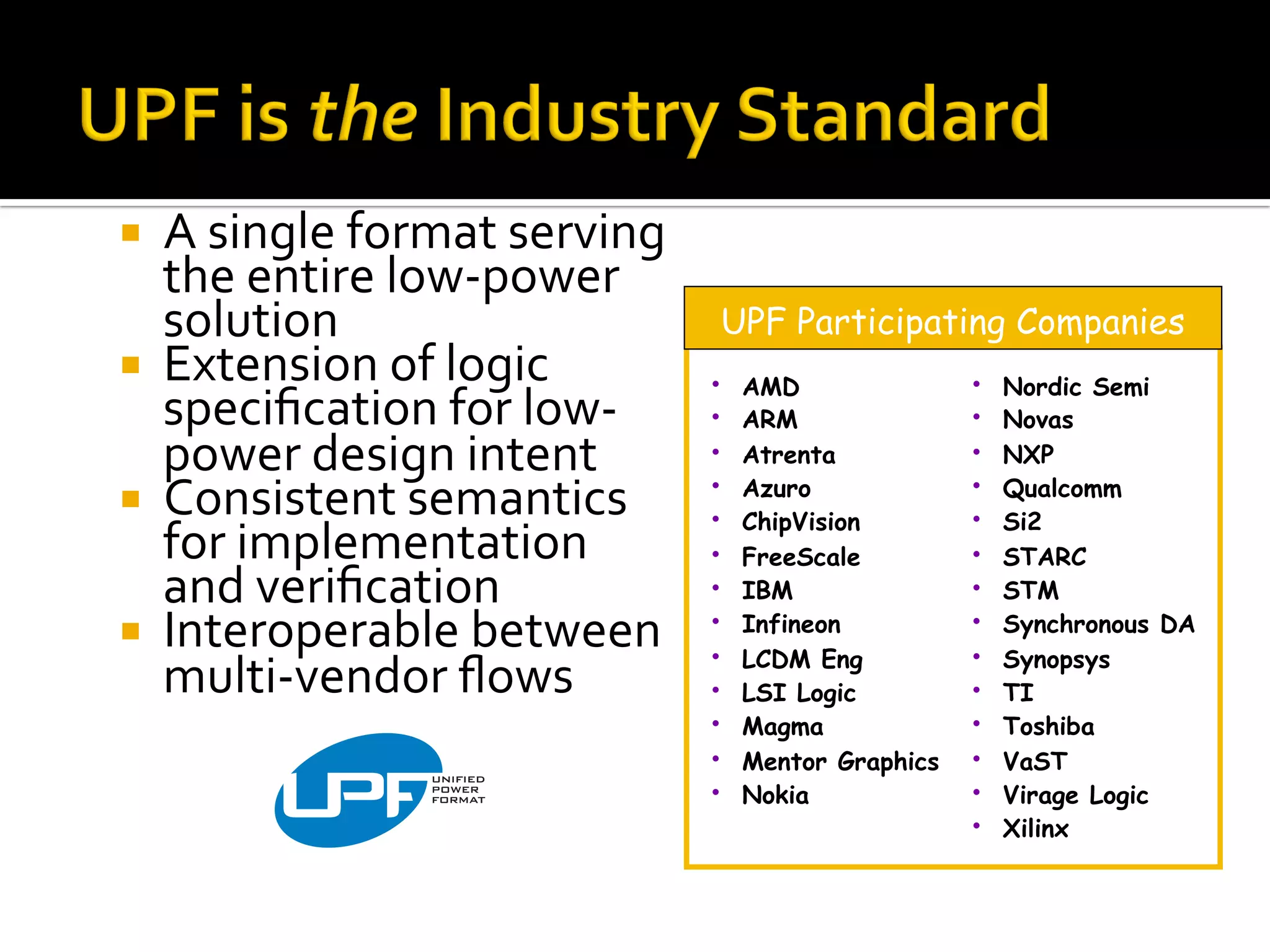

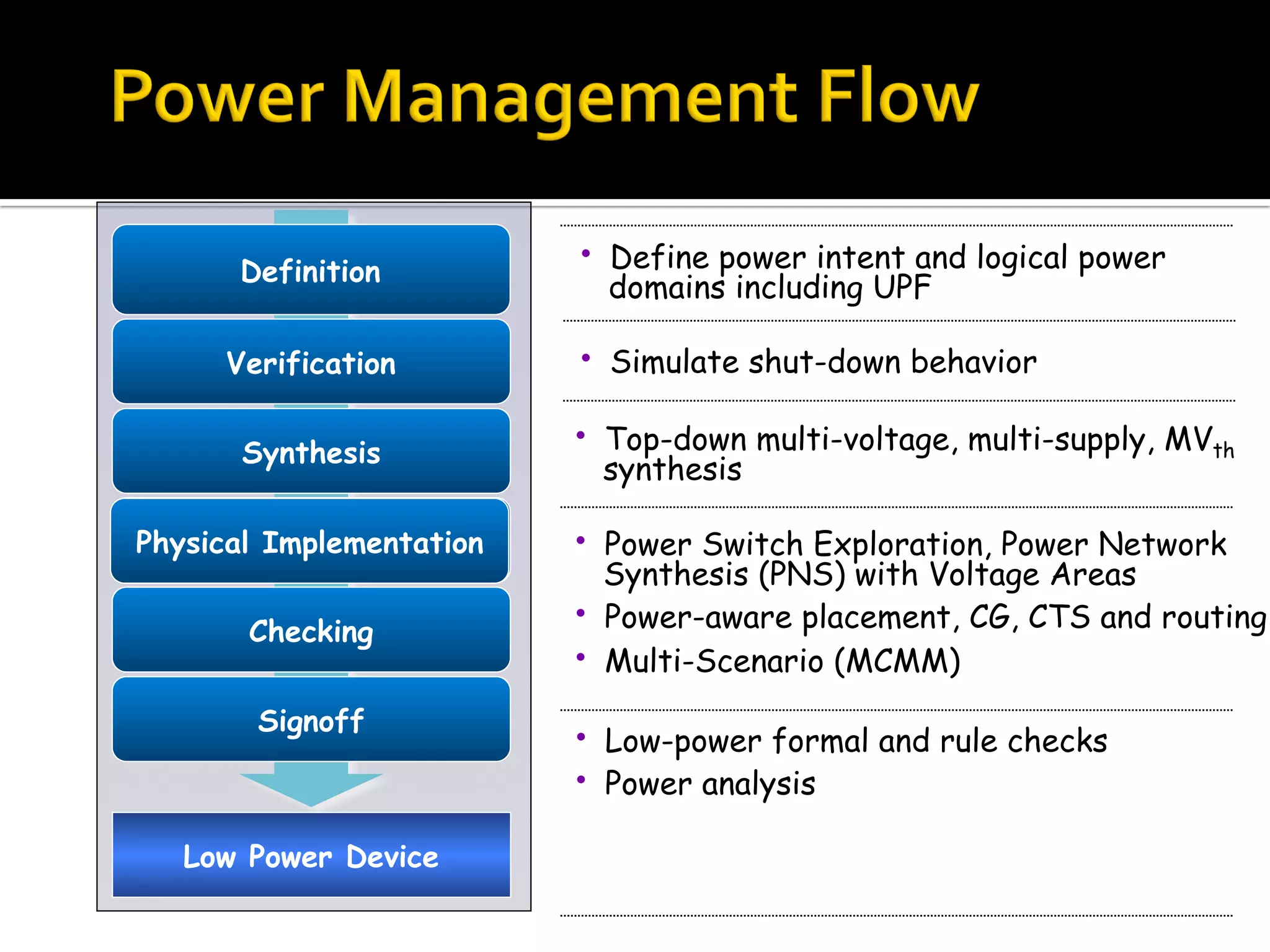

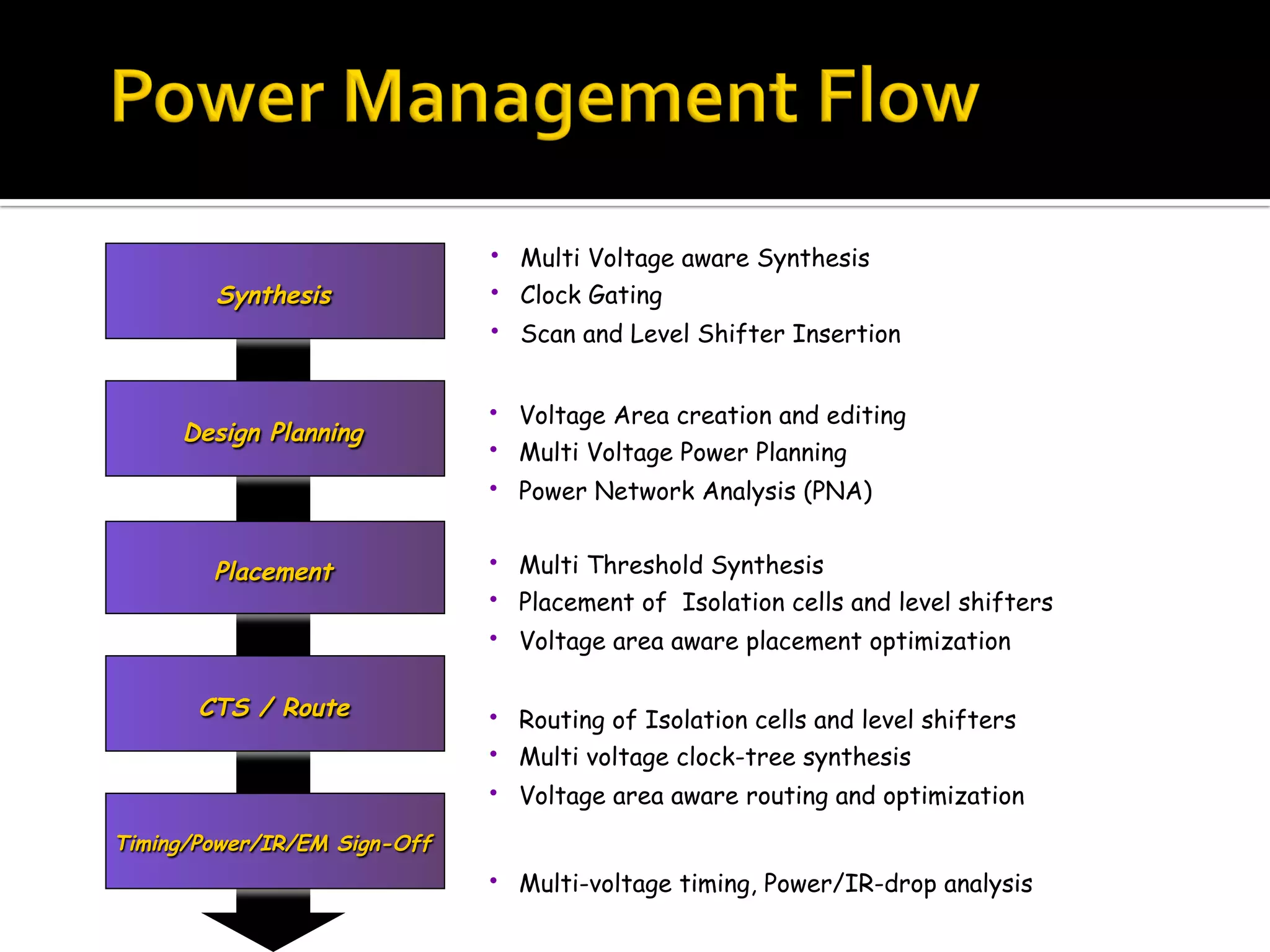

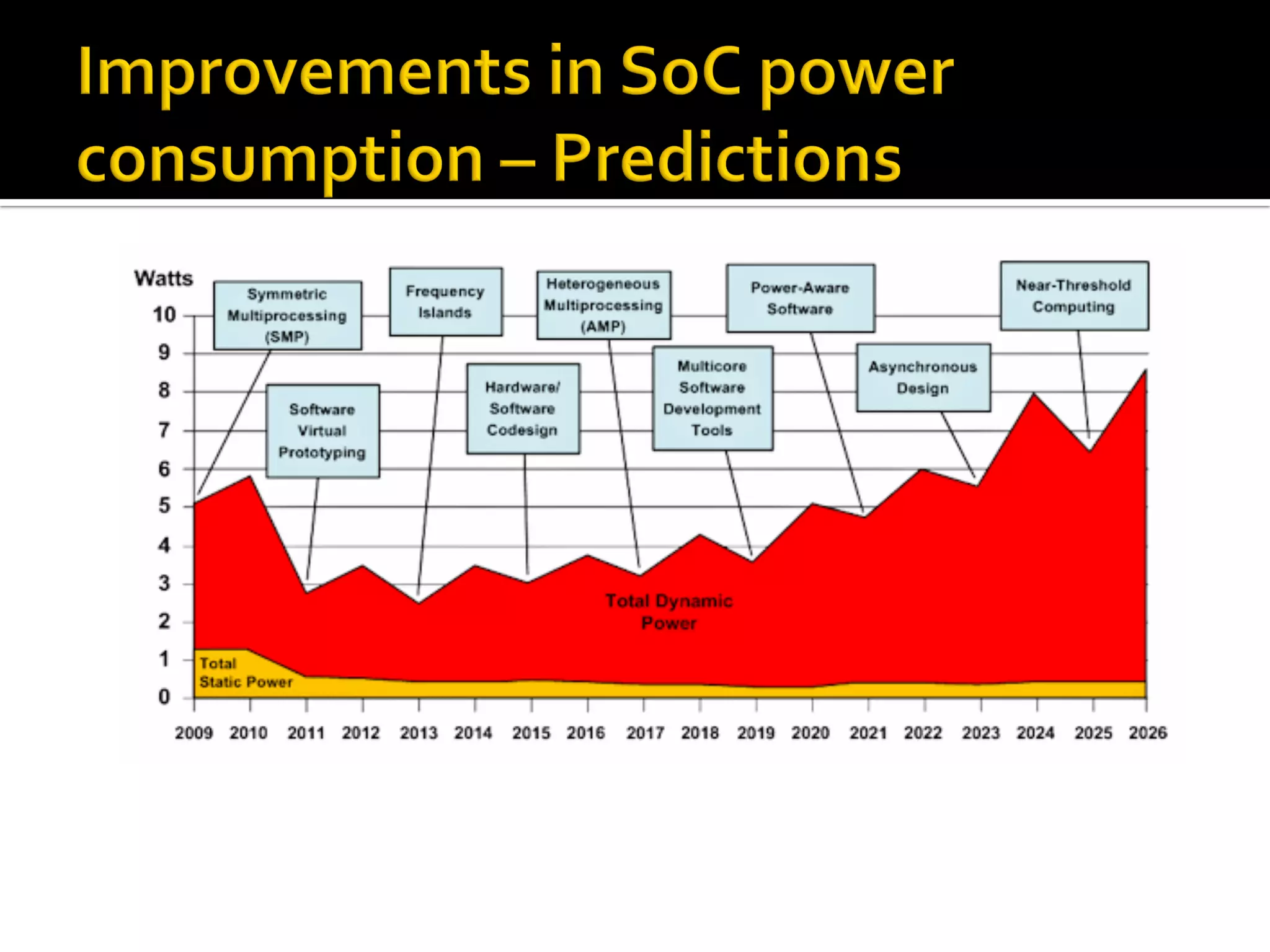

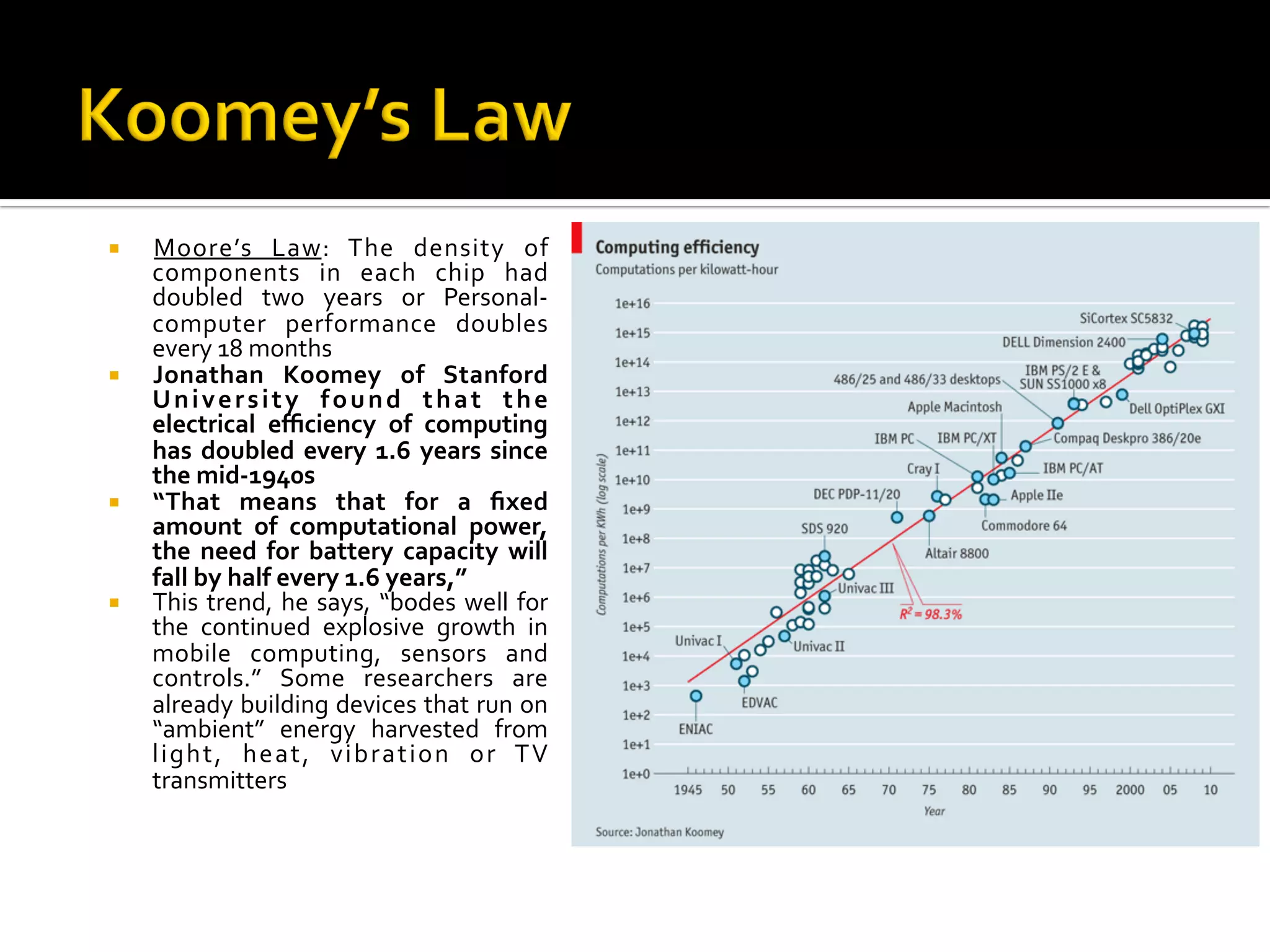

The document discusses techniques for reducing power consumption in integrated circuits and systems. It covers optimization opportunities at various levels of design from system to transistor level. Key techniques discussed include multi-voltage/multi-threshold designs, clock gating, power gating, dynamic voltage and frequency scaling, and reducing switching activity through logic restructuring. The document emphasizes that low power design requires a holistic approach across all levels of the design hierarchy.