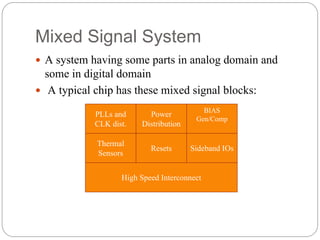

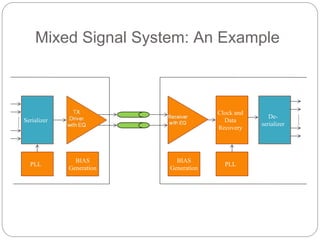

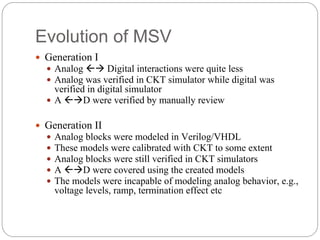

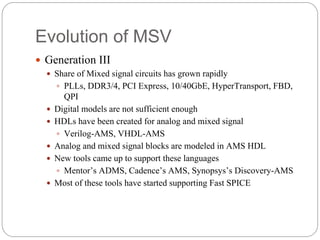

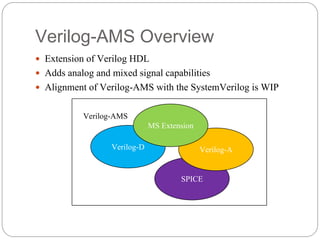

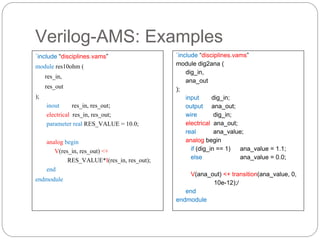

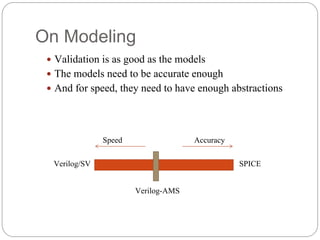

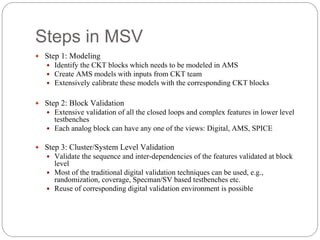

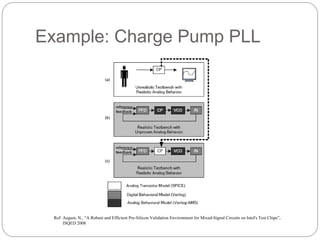

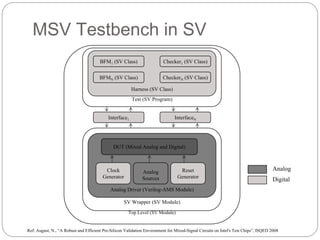

This document discusses trends in mixed signal validation. It begins with an overview of mixed signal systems that contain both analog and digital components. The evolution of mixed signal validation is then described, from early approaches that simulated analog and digital components separately to modern tools that can jointly simulate both domains using languages like Verilog-AMS. The key steps in mixed signal validation are outlined, including modeling components in Verilog-AMS, validating blocks, and performing system-level validation. Throughout, the importance of accurate models for verification is emphasized. Examples of mixed signal modeling and a charge pump PLL validation environment are also provided.