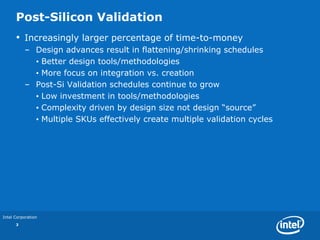

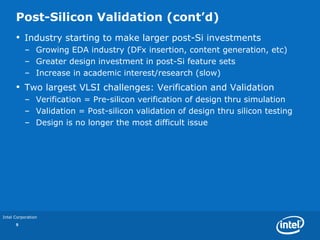

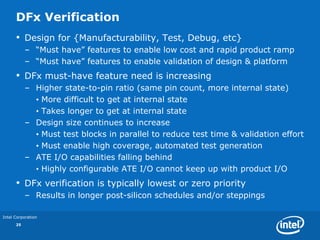

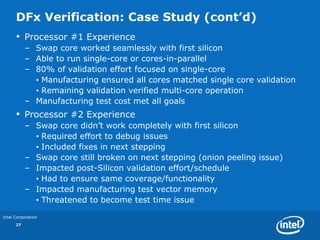

1) Pre-silicon verification is increasingly important for post-silicon validation as design complexity grows and schedules shrink. Bugs that escape pre-silicon verification can significantly impact post-silicon schedules and effort.

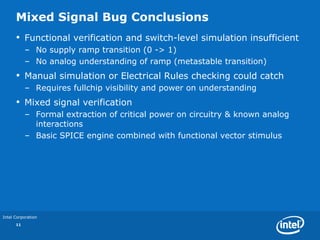

2) Mixed-signal effects, power-on/reset sequences, and design-for-testability features need to be verified pre-silicon to avoid difficult to reproduce bugs during post-silicon validation.

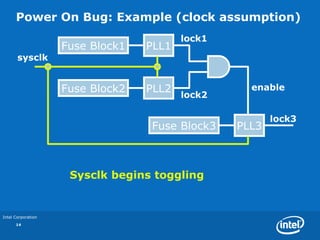

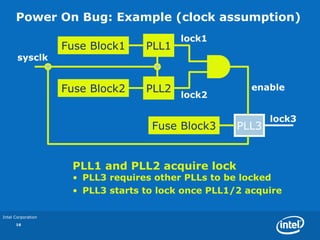

3) Case studies demonstrate how low investment in pre-silicon verification of areas like power-on/reset sequences and design-for-testability features can lead to longer post-silicon schedules due to unexpected bugs.