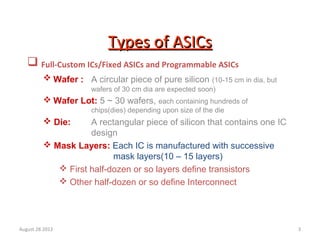

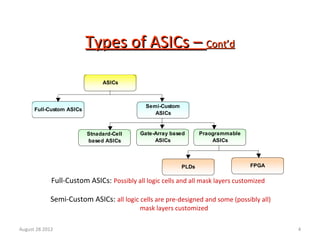

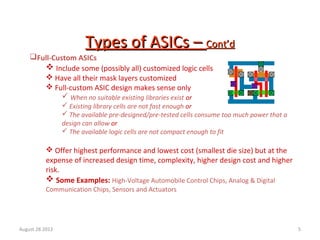

The document discusses different types of application specific integrated circuits (ASICs). It describes ASICs as integrated circuits customized for a particular application, as opposed to standard integrated circuits. The document outlines two main types of ASICs: full-custom ASICs which have all logic cells and mask layers customized, and semi-custom ASICs which use pre-designed logic cells but have customized mask layers. Within semi-custom ASICs it distinguishes between standard cell-based and gate array-based designs. The document also covers programmable ASICs including PLDs, CPLDs and FPGAs.

![11

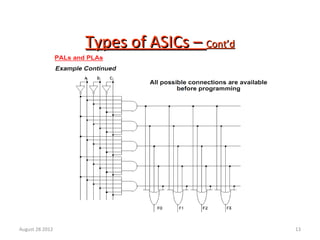

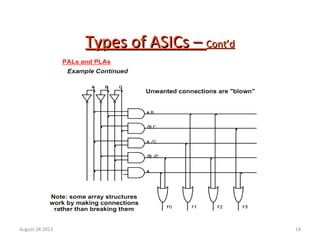

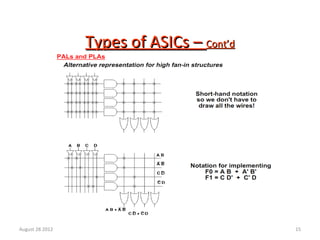

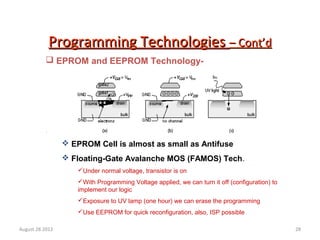

Types of ASICs –Types of ASICs – Cont’dCont’d

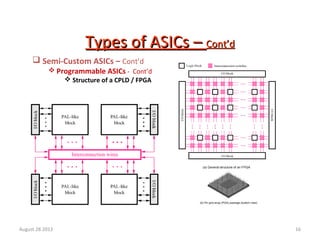

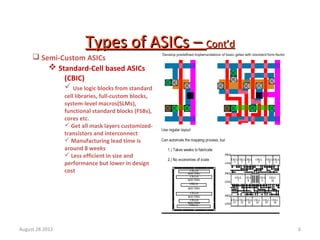

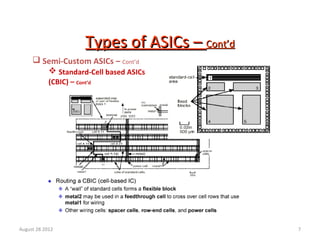

Semi-Custom ASICs – Cont’d

Programmable ASICs

PLDs - PLDs are low-density devices

which contain 1k – 10 k gates and are

available both in bipolar and CMOS

technologies [PLA, PAL or GAL]

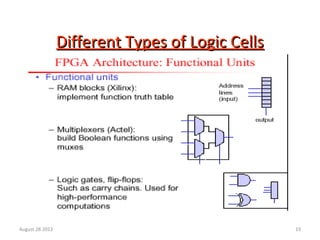

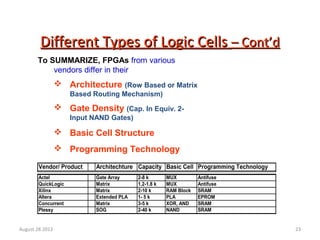

CPLDs or FPLDs or FPGAs -

FPGAs combine architecture of gate arrays

with programmability of PLDs.

User Configurable

Contain Regular Structures - circuit

elements such as AND, OR,

NAND/NOR gates, FFs, Mux, RAMs,

Allow Different Programming

Technologies

Allow both Matrix and Row-based

Architectures

August 28 2012](https://image.slidesharecdn.com/asicdesignlect1-2august282012-130831043644-phpapp01/85/Asic-design-lect1-2-august-28-2012-11-320.jpg)

![12

Types of ASICs –Types of ASICs – Cont’dCont’d

Semi-Custom ASICs – Cont’d

Programmable ASICs

PLDs - PLDs are low-density devices

which contain 1k – 10 k gates and are

available both in bipolar and CMOS

technologies [PLA, PAL or GAL]

CPLDs or FPLDs or FPGAs -

FPGAs combine architecture of gate arrays

with programmability of PLDs.

User Configurable

Contain Regular Structures - circuit

elements such as AND, OR,

NAND/NOR gates, FFs, Mux, RAMs,

Allow Different Programming

Technologies

Allow both Matrix and Row-based

Architectures

August 28 2012](https://image.slidesharecdn.com/asicdesignlect1-2august282012-130831043644-phpapp01/85/Asic-design-lect1-2-august-28-2012-12-320.jpg)