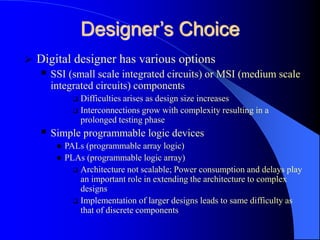

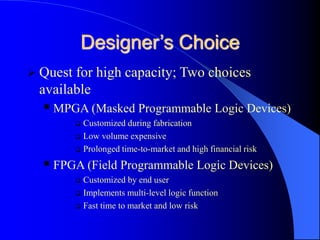

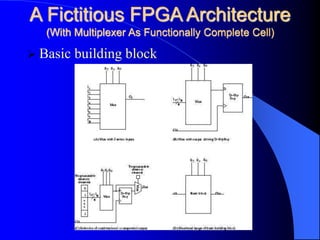

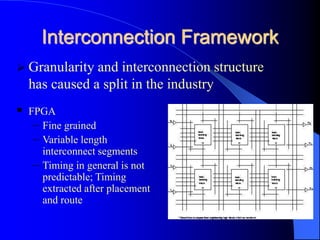

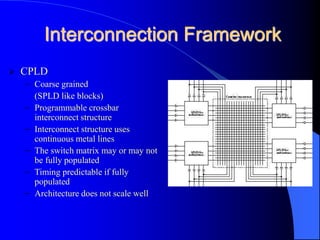

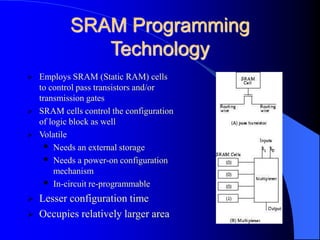

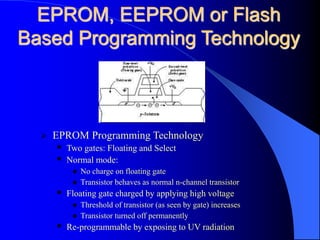

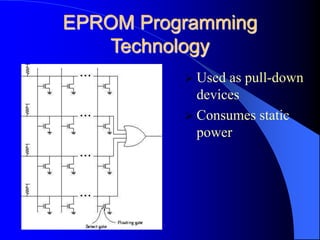

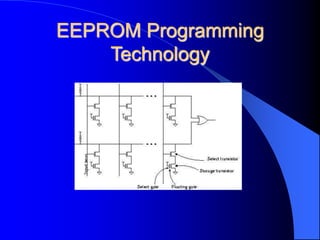

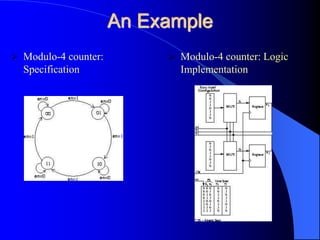

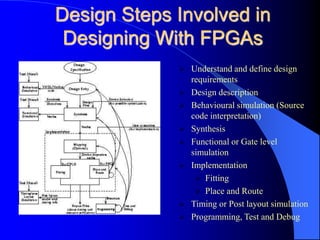

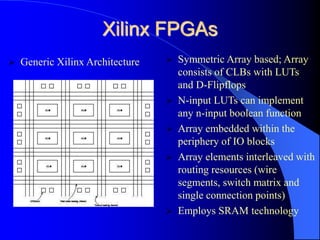

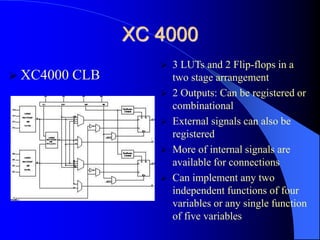

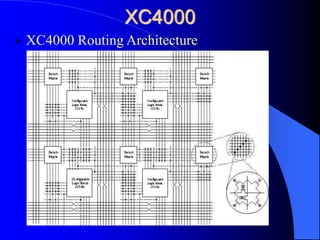

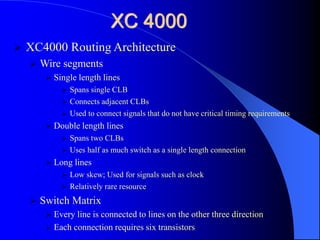

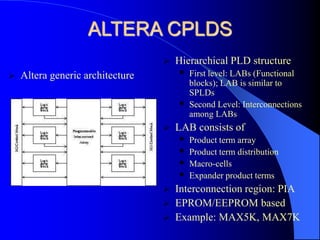

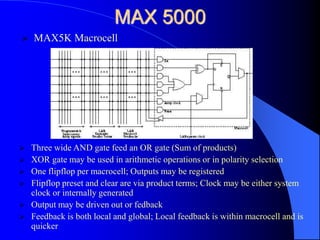

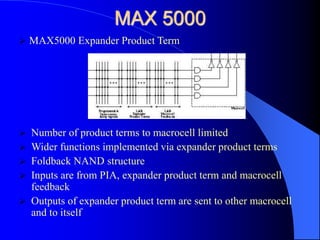

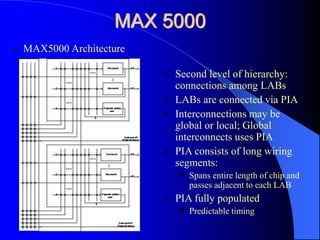

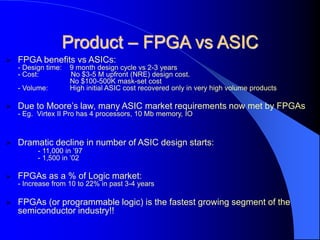

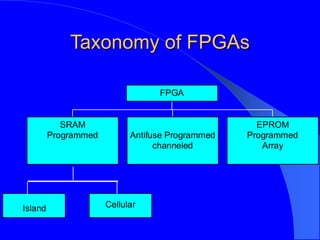

The document discusses field programmable gate arrays (FPGAs), including their architecture, programming technologies, design process, and commercially available devices. FPGAs provide reprogrammability and fast time-to-market compared to application-specific integrated circuits (ASICs). The core of an FPGA consists of an array of configurable logic blocks and a hierarchical interconnect structure that allows the blocks to be wired together. FPGAs can be programmed using SRAM, antifuse, EPROM, or EEPROM technologies. Examples of popular FPGAs are Xilinx's XC4000 series with LUT-based logic blocks and Altera's MAX5000 series consisting of macrocells in logic array blocks.